# An Algorithm for Optimal Sizing of the Capacitor Banks under Non-sinusoidal and Unbalanced Conditions

Murat E. Balci\*1, Shady H.E. Abdel Aleem2, Ahmed F. Zobaa3 and Selcuk Sakar4

<sup>1</sup>Electrical and Electronics Engineering, Balikesir University, Balikesir, Turkey

<sup>2</sup>15<sup>th</sup> of May Higher Institute of Engineering, 15<sup>th</sup> of May, Helwan, Cairo, Egypt

<sup>3</sup>School of Engineering and Design, Brunel University, Uxbridge, UB8 3PH, Middlesex, United Kingdom

<sup>4</sup>Electrical and Electronics Engineering, Gediz University, Gediz, Turkey

\*Corresponding author email: mbalci@balikesir.edu.tr

Fax: +902666121194

Phone: +902666121257

Abstract: In non-sinusoidal and unbalanced systems, optimal sizing of the capacitor banks is not a straightforward task as in sinusoidal and balanced systems. In this paper, by means of qualitative and quantitative analysis, it is interpreted that the classical capacitor selection algorithm widely implemented in Reactive Power Control (RPC) relays does not achieve optimal power factor improvement in non-sinusoidal and unbalanced systems. Accordingly, a computationally efficient algorithm is proposed to find the optimal capacitor bank for smart RPC relays. It is further shown in a simulated test case by using Matlab software that the proposed algorithm provides better power factor improvement when compared with the classical algorithm. It is also figured out from the simulation results that both algorithms cause almost the same harmonic distortion and unbalance deterioration levels in the system.

**Keywords**: Unbalanced conditions, nonsinusoidal conditions, power quality, power systems harmonics.

Short Running Title: Optimal Sizing of Capacitor banks in distorted environment

#### 1. INTRODUCTION

In sinusoidal and balanced systems, conventional power resolution ( $S^2=P^2+Q^2$ ) has been effectively utilized to measure the power transfer efficiency or power factor without any reservations by electrical (pf=P/S)engineering community [1]. Thus, it is well known for sinusoidal and balanced systems that the power of the compensation capacitor banks, which adjust power factor to near unity, is equal to the reactive-power (O) measured at the load terminal, especially if the variation of the terminal voltage is negligible via compensation [2]. As a result, in sinusoidal and balanced systems, RPC relays have been employed to control the switched capacitors for the proper reactive-power compensation of the loads with variable power. In the present day's power systems, voltages and currents are non-sinusoidal and unbalanced due to the fact that large proliferation of nonlinear and single-phase loads. For such systems, optimal capacitor sizing is not a straightforward process, as done for the sinusoidal and balanced systems [3]. Due to this fact, RPC relays generally select the capacitor banks by assuming the system is balanced and free from the harmonic pollution [4]-[7]. With respect to the classical algorithm widely implemented in the current RPC relays [4]-[7], the power quantities given in (1) are calculated for fundamental frequency using measured one line-toline voltage and one line current:

$$S_1 = \sqrt{3}U_{\ell\ell 1}I_{\ell 1}, \cos \varphi_1 = \frac{P_1}{S_1}, Q_1 = \sqrt{S_1^2 - P_1^2}$$

(1)

Thus, the nameplate power of the delta connected balanced capacitor banks, which are needed to improve actual displacement power factor to its desired value, is determined as follows, where  $\varphi_I$  is the difference between the fundamental harmonic phase angles of the line-to-neutral point voltage and the measured line current:

$$Q_{C-R} = P_1 \left( tan \, \varphi_1^{actual} - tan \, \varphi_1^{desired} \right)$$

so that

$$dpf^{actual} = cos \, \varphi_1^{actual} = P_1 / S_1^{actual} ,$$

$$dpf^{desired} = cos \, \varphi_1^{desired} = P_1 / S_1^{desired} .$$

(2)

Additionally, for non-sinusoidal and unbalanced systems, some algorithms on the optimal sizing of the capacitive compensator are studied in the literature [8] -[10]. In [8], optimal reactances of the compensation capacitors are analytically calculated by considering the current minimization approach where the variation of the terminal voltage is negligible via compensation. For the most of the practical operation in three-phase systems the capacitor banks are employed as a delta balanced connection of the identical capacitors. However, this case was not considered for the modeling of the compensator in the same study. In addition to that, it does not consider the requirements, which are defined to prevent the detrimental effects of the non-sinusoidal voltages on the capacitor banks in IEEE Standard 18-2002 [11]. On the other hand, in non-sinusoidal and balanced systems of which the terminal voltage's variation is not negligible via compensation, [9] found optimal capacitive compensator using an optimization technique according to the combination of three criteria: maximizing true power factor, minimizing line loss and maximizing

average power transfer efficiency. For the same system conditions considered in [9], optimization problem of the capacitive compensator is separately solved according to each one of these three criteria in the study [10]. Due to the fact that both studies are based on the optimization technique, they can practically not be implemented in RPC relays.

In this paper, for optimum power factor improvement under non-sinusoidal and unbalanced conditions, the shortage of the compensator sizing algorithm (classical algorithm), which is widely employed in current RPC relays, is figured out by qualitative and quantitative analysis in Section 2. An alternative method on the sizing of the capacitor banks is suggested for the three-phase and three-line applications of smart RPC relays in Section 3. Finally, in Section 4, the proposed method and the classical algorithm are comparatively analyzed in a simulated non-sinusoidal and unbalanced system case.

## 2. Shortage of the Classical Compensator Sizing Algorithm

For sinusoidal conditions, a compensation capacitor's rated power, which is generally called as "Nameplate Power" in electrical engineering community, is calculated using its capacitive reactance  $(X_C)$ , rated voltage  $(U_R)$  and rated line frequency  $(f_R)$  [2]:

$$Q_{C-R} = \frac{U_R^2}{X_C} = 2\pi f_R C U_R^2 = U_R I_R, I_R = 2\pi f_R C U_R$$

(3)

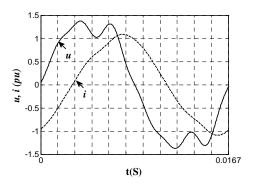

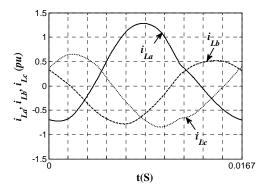

Regarding systems with rated sinusoidal voltage; the reactive power drawn by a capacitor is equal to its nameplate power and the reactive power measured at the load terminals gives the nameplate power of the optimum compensation capacitor which adjusts power factor to its maximum value (unity) in this kind of systems. However, in non-sinusoidal systems, it is not easy to determine the nameplate power of the capacitor banks achieving optimum power factor improvement as in sinusoidal systems. This matter can be interpreted in an exemplary single-phase case, which consists of the voltage source with *THDU* (total voltage harmonic distortion) measured as 15% and R-L impedance load. In the exemplary case, load voltage and load current wave shapes are plotted in Fig (1).

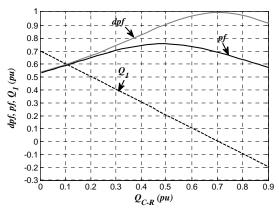

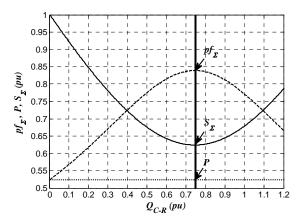

For the case during the variation of the nameplate power ( $Q_{\text{C-R}}$ ) of the compensation capacitor, fundamental harmonic reactive-power ( $Q_1 = U_1 I_1 \sin \varphi_1$ ) measured at the load terminal, true power factor,  $pf = \sum_h U_h I_h \cos \varphi_h \bigg/ \sqrt{\sum_h U_h^2 \sum_h I_h^2}$ , and displacement

power factor (dpf) are shown in Fig. (2).

It is seen from Fig. (2) that  $Q_I$  measured for the system without compensation gives the nameplate power of the capacitor which improve dpf to its maximum (unity). However, it is also seen that  $pf_{max}$  and  $dpf_{max}$  are obtained by using the different nameplate powers of the capacitor (0.488 pu and 0.7 pu respectively). It means that classical

Fig. (1). The load voltage and load current in the exemplary case, t for time in seconds

Fig. (2).  $Q_I$ , dpf and pf values measured at the load terminal during the variation of  $Q_{C-R}$

method does not achieve  $pf_{max}$  in non-sinusoidal conditions. In addition to the above mentioned results, it is clearly understood from the literature [12]-[15] that there is no unique power factor definition for non-sinusoidal and unbalanced three-phase systems due to the fact that apparent power definition is still a discussion topic for this kind of systems. Furthermore, these studies also showed that IEEE Standard 1459-2010 [16] and DIN Standard 40110 [17] apparent power definitions can be employed for the effective measurement of power factor or power transfer efficiency.

First definition, apparent power defined in DIN Standard 40110, can be calculated for three-phase and three-line systems as;

$$S_{\Sigma} = U_{\Sigma} I_{\Sigma} = \sqrt{U_{a0}^2 + U_{b0}^2 + U_{c0}^2} \sqrt{I_a^2 + I_b^2 + I_c^2}$$

(4)

by using the rms values of phase currents  $(I_a, I_b, I_c)$  and the line-to-virtual star point voltages  $(U_{a0}, U_{b0}, U_{c0})$  [12].

For three-phase and three-line systems, second definition, apparent power defined in IEEE Standard 1459-2010, is expressed as;

$$S_e = 3U_e I_e = 3\sqrt{\frac{U_{ab}^2 + U_{bc}^2 + U_{ca}^2}{9}} \sqrt{\frac{I_a^2 + I_b^2 + I_c^2}{3}}$$

(5)

When total line loss is written for three-phase and three-line systems with identical line resistances (r);

$$\Delta P = r \left( I_a^2 + I_b^2 + I_c^2 \right) = r I_{\Sigma}^2$$

(6)

It is obvious from (4), (5) and (6) that minimization of the total line loss can be obtained by maximizing power

factors calculated with respect to DIN Standard 40110 and IEEE Standard 1459-2010 definitions (  $pf_{\Sigma} = P/S_{\Sigma}$ and  $pf_e = P/S_e$ ) where voltage variation is negligible after the compensation. To achieve this goal, the balanced capacitor banks should minimize collective rms value of the line currents:

$$I_{\Sigma}^{2} = I_{a}^{2} + I_{b}^{2} + I_{c}^{2} = \frac{I}{T} \int_{a}^{T} \left( i_{a}^{2} + i_{b}^{2} + i_{c}^{2} \right) dt$$

(7)

However, classical method determines the nameplate power of the balanced capacitor banks regarding the fundamental harmonic reactive-power measured at one phase. Therefore, in three-phase and three-line systems with unbalanced and non-sinusoidal conditions, the current RPC relays can not maximize power factor encouraged by IEEE Standard 1459-2010 and DIN Standard 40110. Furthermore, they can cause lower or over compensation according to both standards.

#### 3. PROPOSED ALGORITHM

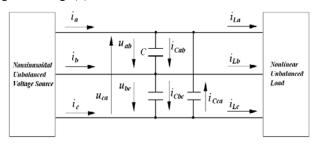

The nameplate power of the optimal balanced capacitor bank, which maximizes true power factor encouraged by IEEE 1459-2010 and DIN 40110 standards, can be determined using the illustrative system given in Fig. (3).

Fig. (3). An illustrative system used for the determination of the nameplate power of the optimal balanced capacitor bank

For the illustrative system, line-to-line voltages, load currents, compensator currents and line currents can be

$$u_{ab} = \sum_{h} \sqrt{2} U_{abh} \cos \left(h \omega t + \alpha_{abh}\right),$$

$$u_{bc} = \sum_{h} \sqrt{2} U_{bch} \cos \left(h \omega t + \alpha_{bch}\right),$$

$$u_{ca} = \sum_{h} \sqrt{2} U_{cah} \cos \left(h \omega t + \alpha_{cah}\right).$$

$$i_{La} = \sum_{h} \sqrt{2} I_{Lah} \cos \left(h \omega t + \beta_{Lah}\right),$$

$$i_{Lb} = \sum_{h} \sqrt{2} I_{Lbh} \cos \left(h \omega t + \beta_{Lbh}\right),$$

$$i_{Lc} = \sum_{h} \sqrt{2} I_{Lch} \cos \left(h \omega t + \beta_{Lch}\right).$$

$$i_{Cab} = C \frac{du_{ab}}{dt}, \quad i_{Cbc} = C \frac{du_{bc}}{dt}, \quad i_{Cca} = C \frac{du_{ca}}{dt}$$

$$(10)$$

$$i_{a} = i_{La} + C \frac{du_{ab}}{dt} - C \frac{du_{ca}}{dt},$$

$$i_{b} = i_{Lb} + C \frac{du_{bc}}{dt} - C \frac{du_{ab}}{dt},$$

$$i_{c} = i_{Lc} + C \frac{du_{ca}}{dt} - C \frac{du_{bc}}{dt}.$$

(11)

By minimizing the collective rms value of the line currents with respect to the capacity,

$$\frac{d\left(I_{\Sigma}^{2}\right)}{dC} = \frac{d\left(I_{a}^{2} + I_{b}^{2} + I_{c}^{2}\right)}{dC} = 0 \tag{12}$$

the capacity of the capacitors placed in the optimum balanced compensator is found to be;

$$C_{opt} = \frac{1}{2\pi f_R} \cdot \frac{A}{2(B-D)} \tag{13}$$

where: A, B and D are expressed as;

$$A = \sum_{h} h U_{abh} \begin{pmatrix} I_{Lah} \sin (\alpha_{abh} - \beta_{Lah}) \\ -I_{Lbh} \sin (\alpha_{abh} - \beta_{Lbh}) \end{pmatrix}$$

$$+ \sum_{h} h U_{bch} \begin{pmatrix} I_{Lbh} \sin (\alpha_{bch} - \beta_{Lbh}) \\ -I_{Lch} \sin (\alpha_{bch} - \beta_{Lch}) \end{pmatrix}$$

$$+ \sum_{h} h U_{cah} \begin{pmatrix} I_{Lch} \sin (\alpha_{cah} - \beta_{Lch}) \\ -I_{Lah} \sin (\alpha_{cah} - \beta_{Lch}) \end{pmatrix}$$

$$B = \sum_{h} h^{2} U_{abh}^{2} + \sum_{h} h^{2} U_{bch}^{2} + \sum_{h} h^{2} U_{cah}^{2}$$

$$D = \sum_{h} h^{2} U_{abh} U_{cah} \cos (\alpha_{abh} - \alpha_{cah})$$

$$+ \sum_{h} h^{2} U_{bch} U_{abh} \cos (\alpha_{bch} - \alpha_{abh})$$

$$+ \sum_{h} h^{2} U_{cah} U_{bch} \cos (\alpha_{cah} - \alpha_{bch})$$

$$(16)$$

The nameplate power of the optimal balanced capacitor bank, which minimizes  $I_{\Sigma}$  and maximizes  $pf_{\Sigma}$  or  $pf_e$ , is found by substituting  $C_{opt}$  calculated from (13) in

$$Q_{C-R} = 3\frac{U_{\ell\ell R}^2}{X_{Copt}}, X_{Copt} = \frac{1}{2\pi f_R C_{opt}}$$

(17)

where  $U_{\ell\ell R}$  is the rated line-to-line voltage of the

Finally, the total rms values of each capacitor's current and total reactive powers drawn by each capacitors can be written as in (18) and (19):

$$I_{Cab} = \frac{1}{X_{Copt}} \sqrt{\sum_{h} h^{2} U_{abh}^{2}},$$

$$I_{Cbc} = \frac{1}{X_{Copt}} \sqrt{\sum_{h} h^{2} U_{bch}^{2}},$$

$$I_{Cca} = \frac{1}{X_{Copt}} \sqrt{\sum_{h} h^{2} U_{cah}^{2}}$$

(18)

$Q_{\it Cab} = U_{\it ab} I_{\it Cab}$  ,  $Q_{\it Cbc} = U_{\it bc} I_{\it Cbc}$  ,  $Q_{\it Cca} = U_{\it ca} I_{\it Cca}$ On the other hand, to prevent the detrimental effects of the non-sinusoidal voltages on the capacitors, the

(19)

following requirements included in IEEE Standard 18-2002 should be satisfied.

- The total rms currents ( $I_{Cab}$ ,  $I_{Cbc}$ ,  $I_{Cca}$ ), which are calculated for each identical capacitors of the optimal compensator, should not exceed 135% of their rated current ( $I_{C-R} = Q_{C-R}/(3U_{\ell\ell R})$ ).

- (ii) The total rms value of the line-to-line voltages  $(U_{ab}, U_{bc}, U_{ca})$  should not exceed 110% of the rated line-to-line voltage of the optimal compensator (  $U_{\ell\ell R}$  ).

- (iii) The total reactive powers ( $Q_{Cab}$ ,  $Q_{Cbc}$ ,  $Q_{Cca}$ ), which are drawn by the capacitors placed in the optimal compensator, should not exceed 135% of their rated power  $(Q_{C-R}/3)$ .

These limits can be formulated as;

$$\frac{max(I_{Cab}, I_{Cbc}, I_{Cca})}{I_{C-R}} \le 1.35 \tag{20}$$

$$\frac{\max(U_{ab}, U_{bc}, U_{ca})}{U_{ab}} \le 1.1 \tag{21}$$

$$\frac{\max(I_{Cab}, I_{Cbc}, I_{Cca})}{I_{C-R}} \le 1.35$$

$$\frac{\max(U_{ab}, U_{bc}, U_{ca})}{U_{\ell\ell R}} \le 1.1$$

$$\frac{\max(Q_{Cab}, Q_{Cbc}, Q_{Cca})}{(Q_{C-R}/3)} \le 1.35$$

(20)

Therefore, a representative pseudo code written for the proposed algorithm is stated below:

**Step 1:** Measure line-to-line voltages and line currents.

Step 2: Find the harmonic spectrums of the measured voltages and currents via DFT (Discrete Fourier Transform).

**Step 3:** Determine the rated power  $(Q_{C-R})$  of optimal balanced capacitor bank from (17).

Step 4: Insert balanced capacitor banks with the rated powers around  $Q_{C-R}$  into the system.

Step 5: Let the tested capacitor bank, which provides the maximum  $pf_{\Sigma}$  value and the requirements given in (20)-(22), connect to the system.

#### 4. COMPARITIVE ANALYSIS

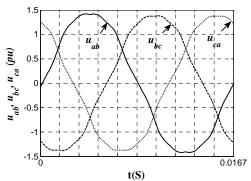

The power factor improvement performances of the alternative algorithm presented in Section 3 and classical algorithm are comparatively analyzed by simulating the illustrative system given in Fig. (3). The system consists of the line-to-line voltages and load currents, which are plotted in Fig. (4a) and (4b). It is shown from this figure that both line-to-line voltages and load currents are nonsinusoidal and unbalanced. In the system, THDU and  $(U_I/U_{I+})$  values are 5.00% and 2.05%, respectively. THDI<sub>a,b,c</sub> values of the load currents are 34%, 22% and 28%, respectively. In addition, the  $I_I/I_{I^+}$  value of the load currents is measured as 28.60%.

In the test system, firstly, the maximum power factor value realizable via a balanced capacitor bank is determined. It was shown in [12]-[15] that DIN Standard 40110 and IEEE Standard 1459-2010 apparent power definitions give the same results for the three-phase and three-line system such as the illustrative one.

Fig. (4a). Line-to-line voltages

Fig. (4b). Load currents Fig. (4). Line-to-line voltages and load currents

Thus, the variations of active power (P), one of apparent power definitions, DIN Standard 40110 apparent power  $(S_{\Sigma})$ , and power factor  $(pf_{\Sigma}=P/S_{\Sigma})$  during increment of the nameplate power  $(Q_{C-R})$  of the balanced capacitor bank are plotted in Fig. (5). Note that the nameplate power of the capacitor bank when power factor reaches its maximum  $(pf_{\Sigma max})$  is pointed in the figure by a vertical line.

Fig. (5). The variations of active power and DIN Standard 40110 apparent power and power factor during the increment of the nameplate power of the balanced capacitor bank

It is shown from Fig. (5) that  $pf_{\Sigma}$  can be improved from 0.521 to 0.842 by means of the balanced capacitor bank. It is also carried out that  $Q_{C-R}$  is 0.743 pu when  $pf_{\Sigma}$ reaches 0.842.

In the studied system, by using classical and proposed algorithms, the calculated  $Q_{C-R}$  values and achieved  $pf_{\Sigma}$  levels are given in Table I. Classical method can be applied by implementing several voltage and current measurement strategies such as (i) measurement of  $u_{ab}$  and  $i_{Lc}$ , (ii) measurement of  $u_{bc}$  and  $i_{La}$ , and (iii) measurement of  $u_{ca}$  and  $i_{Lb}$ , are considered in the analysis. Thus,  $pf_{\Sigma}$  can be increased to 0.810, 0.757 or 0.830 using the balanced capacitor banks with the  $Q_{C-R}$  values determined as 0.590, 1.028 or 0.785 pu respectively. One can see from the variation of  $pf_{\Sigma}$  with  $Q_{C-R}$  plotted in Fig. (5) and Table I that the result of the classical algorithm depends on the measurement strategy and it can cause lower or over compensation with respect to IEEE Standard 1459-2010 and DIN Standard 40110.

On the other hand,  $pf_{\Sigma}$  attains 0.842 when the balanced capacitor banks, of which the nameplate power  $(Q_{C-R})$  is determined as 0.743 pu according to proposed algorithm, is employed for the compensation.

In addition to the above mentioned results,  $I_I J_I^+$  and THD values of the line currents measured in the system compensated with respect to classical and proposed algorithms are given in Table II. This table shows that both algorithms cause almost the same deterioration in  $I_I J_I^+$  and THD values of the line currents. As a result, the proposed one does not have disadvantage on the deterioration in harmonic distortion and unbalance when compared with classical one. It should be noted that the deterioration in THDI can be reduced by means of passive filters [18]-[21].

TABLE I

CALCULATED NAMEPLATE POWERS OF THE BALANCED CAPACITOR

BANKS AND ACHIEVED POWER FACTORS WITH RESPECT TO CLASSICAL

AND PROPOSED ALGORITHMS

| Methods          | Measured voltage and current                          | $Q_{C-R}(pu)$  | $pf_{\Sigma}$  |

|------------------|-------------------------------------------------------|----------------|----------------|

| Classical Method | $u_{ab}, i_{Lc}$ $u_{bc}, i_{La}$                     | 0.590<br>1.028 | 0.810<br>0.757 |

|                  | $u_{ca}$ , $i_{Lb}$                                   | 0.785          | 0.830          |

| Proposed Method  | $u_{ab},\ u_{bc},\ u_{ca}$ $i_{La},\ i_{Lb},\ i_{Lc}$ | 0.743          | 0.842          |

TABLE  ${f II}$   $I_I$ ,  $I_I^+$  and THD values of the line currents for the system compensated with respect to classical and proposed algorithms

| Methods          | $THD_{Ia}$                   | $THD_{Ib}$ | $THD_{Ic}$ | $I_1^{-}/I_1^{+}$ |

|------------------|------------------------------|------------|------------|-------------------|

|                  | All are given in percent (%) |            |            |                   |

| Classical Method | 60                           | 74         | 42         | 47                |

|                  | 82                           | 78         | 43         | 45                |

|                  | 70                           | 94         | 44         | 50                |

| Proposed Method  | 64                           | 90         | 41         | 49                |

#### 5. CONCLUSIONS

At present day, the capacitor banks switched on and off automatically via RPC relays are still the most economical way for the reactive power compensation. However, in current RPC relays, the nameplate power of

the capacitor banks is generally determined by assuming the system is balanced and free from the harmonic pollution. Due to this fact, current RPC relays are not adequate to maximize true power factor definition, which is encouraged by IEEE Standard 1459-2010 and DIN Standard 40110.

Consequently, under unbalanced and non-sinusoidal conditions, a computationally efficient algorithm is proposed to calculate the nameplate power of the optimal balanced capacitor bank, which maximizes the power factor definition of both standards, for implementation in smart RPC relays. It is seen from the results obtained in a simulated test case that the proposed algorithm provide better power factor improvement performance when compared with the classical algorithm.

#### **CURRENT & FUTURE DEVELOPMENTS:**

The shortage of the capacitor sizing algorithm (classical algorithm), which is widely employed in current RPC relays, is discussed under non-sinusoidal and unbalanced systems. It is further shown in a simulated unbalanced and non-sinusoidal test case that the proposed algorithm, which can practically be implemented in the smart RPC relays, provides better results on power factor improvement when compared with the classical algorithm.

The recent trend of harmonic system standards is considering the random nature of voltage and current harmonics. The IEC 1000-3-6 [22] uses probabilistic approaches both in comparing the actual current and voltage harmonic levels for distorting loads; the IEEE Standard 519 [23] slightly addresses the probabilistic application of harmonic distortion limits, but various efforts are in progress to more extensively include the probabilistic aspects. Consequently, the whole design basis may be redefined to include probabilistic aspects.

#### **CONFLICT OF INTEREST:**

The authors declare no conflict of interest.

### NOMENCLATURE

$U_{\ell\ell 1}$ : Fundamental harmonic line-to-line voltage,

$I_{\ell 1}$ : Fundamental harmonic line current,

$P_1$ ,  $Q_1$ ,  $S_1$ : Fundamental harmonic active, reactive and apparent powers,

$\varphi_1$ : Difference between phase angles of fundamental harmonic line-to-neutral voltage and line current, *dpf*: Displacement power factor,

$u_{ab}$ ,  $u_{bc}$ ,  $u_{ca}$ : Instantaneous line-to-line voltages,

$U_{ab}$  ,  $U_{bc}$  ,  $U_{ca}$  : Total rms values of the line-to-line voltages,

$U_{\it abh}$  ,  $U_{\it bch}$  ,  $U_{\it cah}$  : Rms values of the  $\it hth$  harmonic line-to-line voltages,

- $\alpha_{abh}$ ,  $\alpha_{bch}$ ,  $\alpha_{cah}$ : Phase angles of the *hth* harmonic line-to-line voltages,

- $I_{Lah}$  ,  $I_{Lbh}$  ,  $I_{Lch}$  : Rms values of the hth harmonic load current.

- $\beta_{Lah}$ ,  $\beta_{Lah}$ ,  $\beta_{Lah}$ : Phase angles of the *hth* harmonic load current,

- $i_a$ ,  $i_b$ ,  $i_c$ : Instantaneous line currents,

- $I_a$ ,  $I_b$ ,  $I_c$ : Total rms values of the line currents,

- $Q_{C-R}$ : Rated or nameplate power of the compensation capacitor,

- $S_{\scriptscriptstyle \Sigma}$ ,  $U_{\scriptscriptstyle \Sigma}$ ,  $I_{\scriptscriptstyle \Sigma}$ : Collective apparent power, collective rms voltage and collective rms current defined in DIN Standard 40110, respectively,

- $S_e$ ,  $U_e$ ,  $I_e$ : Equivalent apparent power, equivalent rms voltage and equivalent rms current defined in IEEE Standard 1459-2010, respectively,

- $pf_{\Sigma}$ ,  $pf_{e}$ : Power factors calculated by considering DIN Standard 40110 and IEEE Standard 1459-2010 apparent power definitions.

- *THDU:* Total harmonic distortions of the line-to-line voltages.

- *THDI*<sub>a</sub>, *THDI*<sub>c</sub>, *THDI*<sub>c</sub>. Total harmonic distortions of a, b, c line currents.

- $U_I/U_{I+}$ : Ratio between magnitudes of the fundamental frequency negative- and positive- sequence voltages.

- $I_I/I_{I+}$ : Ratio between magnitudes of the fundamental frequency negative- and positive- sequence currents

#### REFERENCES

- [1] IEEE Standard 100, IEEE Standard for the Authoritative Dictionary of IEEE Standards Terms, 2000.

- [2] T.J.E. Miller. Reactive Power Control in Electric Systems. 1st ed., Wiley-Interscience, 1982.

- [3] W. Shepherd and P. Zakikhani. (1973, Jul.). Power factor correction in nonsinusoidal systems by the use of capacitance. *Journal of Phys. D: Appl. Phys.* 6 (16), pp. 1850-1861.

- [4] A. Ozdemir. (2006). A reactive power control relay design with a new approach. *Electrical Eng.* 88 (2), pp. 133-140.

- [5] ABB, Modbus-power factor controller installation and operating instructions manual. Accessible on June 1<sup>st</sup>, 2011, from the web site http://www05.abb.com/global/scot/scot209.n ns/veritydisplay/38f856498d1078d0c125731b004abd31/\$ffile/2 GCS302016A0050%20-%20RVT%20Pamphlet%20en%20.pdf.

- [6] COMAR Condensatori Co., P.F.C. electronic regulator BMR series user manual. Accessible on June 1st, 2011, from the web site http://www.comarcond.com/tedesco/download\_d/MU%20 03.14.mmm%20REV3%20 BMR%20ENG.pdf.

- [7] BARON Co., Janitza power factor control relay features. Accessible on June 1st, 2011, from the web site http://www.baronpower.com/janitza.html.

- [8] T.B. Sekara, J.C. Mikulovic and Z.R. Djurisic, "Optimal reactive compensators in power systems under asymmetrical and nonsinusoidal conditions," *IEEE Trans. on Power Deliv.*, vol. 23, no. 2, pp. 974-984, Apr. 2008.

- [9] I.M. El-Amin, S.O. Duffuaa and A.U. Bawah, "Optimal shunt compensators at nonsinusoidal busbars," *IEEE Trans. on Power Syst.*, vol. 10, no. 2, pp. 716-723, May 1995.

- [10] M.M. Abdel Aziz, E.E. Abou Elzahab, A.M. Ibrahim and A.F. Zobaa. (2003, Oct.). Sizing of capacitors to optimize the power factor at non-sinusoidal frequencies. *EPSR*. 64(1), pp. 81-85.

- [11] IEEE Standard 18-2002, IEEE Standard for Shunt Power Capacitors, 2002.

- [12] M.E. Balci and A.E. Emanuel. (2011, Nov.). Apparent power definitions: a comparison study. *IREE*. 6(6), pp. 2713-2722.

- [13] J.L. Willems, "Reflections on apparent power and power factor in nonsinusoidal and polyphase situations," *IEEE Trans. on Power Deliv.*, vol. 19, no. 2, pp. 835-840, Mar. 2004.

- [14] J.L. Willems, J.A. Ghijselen and A.E. Emanuel, "The apparent power concept and the IEEE standard 1459-2000," *IEEE Trans. on Power Deliv*, vol. 20, no. 2, pp. 876-884, Apr. 2005.

- [15] J.L. Willems, J.A. Ghijselen and A.E. Emanuel, "Addendum to the apparent power concept and the IEEE standard 1459-2000," *IEEE Trans. on Power Deliv.*, vol. 20, no. 2, pp. 885-886, Apr. 2005.

- [16] IEEE Standard 1459-2010, Definitions for the Measurement of Electric Power Quantities under Sinusoidal, Non-sinusoidal, Balanced or Unbalanced Conditions. 2010.

- [17] DIN Standard 40110, Part 2: Polyphase Circuits, 2002 (in German).

- [18] S. H. E. Abdel Aleem and A. F. Zobaa. (2013, Jan.) Different Design Approaches of Shunt Passive Harmonic Filters Based on IEEE Std. 519-1992 and IEEE Std. 18-2002. Recent Pat. Elec. Eng. 6(1), pp. 68-75.

- [19] H. A. M. Ali, A. F. Zobaa and E. E. A. El-Zahab. (2012, Apr.). Single-tuned passive harmonic filters design with uncertain source and load characteristics. *Recent Pat. Elect. Eng.* 5(3), pp. 72–80.

- [20] S. H. E. Abdel Aleem, A. F. Zobaa, and A. C. M. Sung, "On the economical design of multiple-arm passive harmonic filters," in 47th International Universities' Power Engineering. Conf., UPEC'12, Uxbridge, Middlesex, United Kingdom, Sep. 4–7, 2012, pp. 1–6.

- [21] S.H.E. Abdel Aleem, M.E. Balci, A. F. Zobaa, and S. Sakar, "Optimal passive filter design for effective utilization of cables and transformers under non-sinusoidal conditions", *Proc. of* 16th Int. Conf. Harmonics and Quality of Power, ICHQP'14, Bucharest, Romania, May 25–28, pp. 626–630, 2014.

- [22] IEC Standard 1000-3-6, Part 3: Limits. Section 6: Assessment of Emission Limits for Distorting Loads in MV and HV Power Systems Basic EMC Publication, 1996.

- [23] IEEE Standard 519, IEEE Recommended Practices and Requirements for Harmonic Control in Electric Power Systems, 1992.