# Generalized Disjunction Decomposition for Evolvable Hardware

Emanuele Stomeo, Student Member, IEEE, Tatiana Kalganova, and Cyrille Lambert

Abstract—Evolvable hardware (EHW) refers to selfreconfiguration hardware design, where the configuration is under the control of an evolutionary algorithm (EA). One of the main difficulties in using EHW to solve real-world problems is scalability, which limits the size of the circuit that may be evolved. This paper outlines a new type of decomposition strategy for EHW, the "generalized disjunction decomposition" (GDD), which allows the evolution of large circuits. The proposed method has been extensively tested, not only with multipliers and parity bit problems traditionally used in the EHW community, but also with logic circuits taken from the Microelectronics Center of North Carolina (MCNC) benchmark library and randomly generated circuits. In order to achieve statistically relevant results, each analyzed logic circuit has been evolved 100 times, and the average of these results is presented and compared with other EHW techniques. This approach is necessary because of the probabilistic nature of EA; the same logic circuit may not be solved in the same way if tested several times. The proposed method has been examined in an extrinsic EHW system using the  $(1+\lambda)$  evolution strategy. The results obtained demonstrate that GDD significantly improves the evolution of logic circuits in terms of the number of generations, reduces computational time as it is able to reduce the required time for a single iteration of the EA, and enables the evolution of larger circuits never before evolved. In addition to the proposed method, a short overview of EHW systems together with the most recent applications in electrical circuit design is provided.

*Index Terms*—Adaptive system, evolutionary computation, evolvable hardware (EHW), problem decomposition.

#### I. Introduction

VOLVABLE hardware (EHW) [1]–[12], also known as evolutionary electronics and hardware evolution, is a technique to automatically design circuits (digital [5], [9], [13] and analog [5]–[7], [14], [15], antennas [16]–[18], and robots [1], [19], [20]) using methods inspired by natural evolution. The circuit configuration is carried out under the control of evolutionary algorithms (EAs) [21]–[25]. These techniques began to be treated with increasing interest in the 1960s when Holland introduced the concept of genetic algorithms (GAs) [26], [27], which are the most general methods of solving search and optimization problems. Research in this area has introduced other EAs, such as genetic programming (GP) [28]–[30], evolution strategy (ES) [24], grammatical evolution (GE) [31],

Manuscript received May 4, 2005; revised July 25, 2005 and December 27, 2005. This work was supported in part by the Engineering and Physical Sciences Research Council under Grant GR/S17178. This paper was recommended by Associate Editor H. Takagi.

The authors are with the School of Engineering and Design, Brunel University, UB8 3PH Middlesex, U.K. (e-mail: stomeo@ieee.org; tatiana. kalganova@brunel.ac.uk).

Digital Object Identifier 10.1109/TSMCB.2006.872259

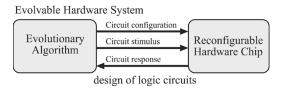

Fig. 1. Schema of a basic EHW system. The EA sends the circuit configurations (the chromosome) to the chip, which configures itself with the configuration received. The EA is also responsible for sending test vectors to stimulate the design inputs and to check the circuit's response received against the expected values. Based on those responses, the EA modifies the chromosomes and supplies a new configuration to the chip. In the case of digital logic circuits, the stimuli are the input combinations of the truth table.

evolutionary programming (EP) [32], Cartesian GP (CGP) [33], [34], adaptive GA (AGA) [35], parallel GA (PGA) [36]–[38], compact GA [39], etc. The basic schema of an EHW system, adapted for the evolution of logic circuits defined by truth tables, is illustrated in Fig. 1. Initially, EHW was intended for real-world applications [41], but due to its limitations in scalability (see Section II), to date few real-world applications have been developed. Table I outlines the most important applications for electrical circuits developed with EHW systems so far. The performance of EHW has been actively studied on the evolution of multipliers. Both programmable logic array (PLA)-based and field-programmable gate array (FPGA)-based circuits have been considered. For example, the three-bit multiplier containing 26 logic gates [40] (the best solution obtained to date) has been evolved for an FPGA structure after 3 000 000 generations using the gate-level EHW approach, introduced in [42] and [43]. In gate-level evolution, the design of digital circuits is based on primitive hardware gates such as AND and OR. Analysis of the complexity of evolved logic circuits in one run revealed that the most complex multiplier evolvable is the four-digit multiplier [44]. The four-bit multiplier was designed using logic gates as building blocks for an FPGA target structure after 643 274 721 generations [44].

This paper presents a new type of decomposition strategy for the evolutionary design of relatively large combinational circuits. The proposed method involves reducing the number of inputs prior to evolving logic circuits by introducing a new function, which was previously briefly discussed in [45]. Here, the authors intend to investigate more thoroughly the behavior of the proposed technique and to show the following.

It is capable of evolving larger circuits never before evolved with any other evolutionary computational technique in a reasonably short time. The most complex circuits evolved are the 17-bit parity, the six-bit multiplier, and the alu4, which is a circuit with 14 inputs and eight

TABLE I

MAIN ELECTRICAL CIRCUITS DESIGNED WITH EHW SYSTEMS

| Author           | Year             | Target device                                                                                                                                     | Approach                                                                                     | Design                                                                                                                                  |

|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Koza et al.      | 1992-<br>present | Computer program presented as trees.                                                                                                              | Genetic programming [28]–[30].                                                               | Synthesize design for complex structures as analog electrical circuits, controllers and mathematical algorithm [28]—[30], [106], [107]. |

| Xu et al.        | 1995             | An Intel Hypercube iPSC <sup>TM</sup> , with 16 microprocessor [63].                                                                              | Parallel genetic algorithm [36]— [38].                                                       | Digital filter [63].                                                                                                                    |

|                  |                  | Analog EHW chip [5].                                                                                                                              | Function Level Evolution [42], [43], [64].                                                   | Chip for cellular phones [5]. Clock timing for Giga hertz systems [5].                                                                  |

| Higuchi et al.   | 1999             | Digital chip which includes GA                                                                                                                    | Function Level Evolution [42], [43], [64].                                                   | Neural network chip [5].                                                                                                                |

|                  |                  | hardware, reconfigurable logic gates and a CPU core.                                                                                              | Gate level evolution [42], [43].                                                             | Data compression chip for electrophotographic printers [5].  Prosthetic hand [5].  Mobile robot navigation [5].                         |

| Thompson et al.  | 1999             | Dynamic state machine [66].  Xilinx XC6216 FPGA [100].                                                                                            | Genetic algorithm.                                                                           | Robot controller [66].  Tone discriminator [66].                                                                                        |

| Miller et al.    | 2000             | Software based with array of AND, XOR [44].                                                                                                       | Cartesian genetic programming [33], [34] together with (1+λ) Evolution Strategy [24], [25]   | 4-bit multiplier [44].                                                                                                                  |

| Kalganova        | 2000             | Software simulation: array of AND, OR, XOR, NOT gates and                                                                                         | Bi-directional incremental evolution [62], [84].                                             | Logic functions from MCNC<br>benchmark [81]. Best circuit evolved<br>was with 7 inputs and 10 outputs.                                  |

|                  |                  | multiplexer.                                                                                                                                      | Extrinsic Function Level evolution [67].                                                     | 3-bit multiplier.                                                                                                                       |

| Seok et al.      | 2000             | Xilinx XC6216 FPGA [100].                                                                                                                         | Context switching [68].                                                                      | Controllers for autonomous mobile robot [68].                                                                                           |

| Keymeulen et al. | 2000             | The GA runs in UNIX workstation.<br>The circuit configurations are<br>downloaded from the workstation<br>to a PC board with 4 FPTA [97]—<br>[99]. | Evolutionary algorithm with: fitness and population based approach [6], [96].                | Fault tolerant digital (XNOR) and analog (2-bit multiplier) circuit [6].                                                                |

| Stoica et al.    | 2003             | The evolutionary algorithm is implemented on DSP and the reconfigurable chip is a JPL FPTA [97]—[99].                                             | Evolutionary algorithm.                                                                      | Half-wave rectifier circuit [7].                                                                                                        |

| Vinger et al.    | 2003             | Xilinx Virtex FPGA XCV1000 [101].                                                                                                                 | Genetic algorithm.                                                                           | Digital Filter: 8 tap 12 bit [69].                                                                                                      |

|                  | 2003             | Software simulation: array of AND-gates and XOR-gates [70].                                                                                       | Incremental evolution with training partitioning vector [70].                                | 5-bit multiplier [70].                                                                                                                  |

| Torresen         |                  | Software simulation: FPGA-based [71].                                                                                                             | Data bus architecture [71].                                                                  | Multipliers (max 4 bits).                                                                                                               |

|                  | 2004             | Software simulation. The proposed architecture fits into most FPGA [72].                                                                          | Classic GA with incremental evolution [72].                                                  | Traffic signs classifier [72].                                                                                                          |

| Hartmann et al.  | 2004             | Software simulator of digital circuits including analogue noise.                                                                                  | Tournament selection genetic algorithm [104], [105].                                         | 2-bit multiplier with noise [13].  2-bit adders with noise [13].  3-bit multiplier with noise [13].                                     |

| Zhang et al.     | 2004             | Xilinx Virtex FPGA XCV1000<br>[101]. It is reconfigured by an<br>external hardware GA.                                                            | Cartesian Genetic programming [33], [34]                                                     | Digital image filter [73].                                                                                                              |

| Gallagher et al. | 2004             | FPGA XC400 [102] on BORG<br>board and VirtexII XC2V1000<br>[101].                                                                                 | Modified compact genetic algorithm (CGA) [39].                                               | De Jong test suite [74], [76].  Dynamic benchmark designed by Gallagher et al. [74].  Locomotion controller [74].                       |

| Sekanina         | 2003             | Xilinx FPGA XC4028XLA [102].                                                                                                                      | Cartesian Genetic [33], [34]<br>Programming operating at function<br>level [42], [43], [64]. | Several image digital noise filter and edge detectors [75].                                                                             |

|                  | 2005             | Software simulation with polymorphic gate-level circuits.                                                                                         | Cartesian Genetic Programming [33], [34].                                                    | Polymorphic circuits [77], [78].                                                                                                        |

outputs taken from the Microelectronics Center of North Carolina (MCNC) library [81].

It is able to significantly reduce the number of generations required to evolve digital logic circuits and to reach higher fitness values, which result in better optimized circuits, although the research presented in this paper concentrates only on the evolution of fully functional circuits rather than on the optimization.

The method presented here therefore breaks through the scalability barrier and opens up new opportunities in the design and application of evolvable combinational electrical circuits. The significance of this paper lies in the potential for EHW to contribute to the design of electrical circuits by removing human intervention and associated costs. Not only electrical

circuits but also antennas and robot controllers could be automatically designed without the need for human inputs. Furthermore, EHW, because of its basis in EAs, could adapt itself to change task requirements and optimize its performance, which would be particularly desirable where human intervention is unfeasible or very expensive. Despite recent advancements in research and technology, a number of issues remain unresolved, including the following.

- Reducing the number of logic gates, which is quite high if compared with hand design circuits.

- Increasing the evolvability [46]–[49]. Evolvability, as defined in [52] is the ability of the genetic operator/representation scheme to produce offsprings that are fitter than their parents.

- Fault tolerance [6], [13], [49]–[51].

- Maintainability and comprehensibility of the evolved circuit [53]. Maintainability as in [54] is the system's ability to preserve and improve its performance and fault tolerance properties and to adjust them to the varying environment.

This paper is organized as follows. The next section considers the problems of scalability and stalling effect in the fitness function. In Section III, a brief description of the benchmarks used to carry out the simulations is presented. Section IV illustrates the basis of an extrinsic EHW system (first introduced in [55]), together with the EA implemented, the chromosome encoded, and the fitness function applied to the system. Furthermore, a short introduction on bidirectional incremental evolution (BIE) is given. Section V outlines the limitations of an EHW system by testing the evolution of several logic circuits of different complexities. Section VI proposes the generalized disjunction decomposition (GDD) for EHW, together with a study case. Section VII gives the parameter's setting for the experiments carried out with the proposed method. Section VIII illustrates the experimental results of the proposed method together with BIE. The proposed method is compared against other techniques and the advantages and disadvantages are outlined. Section IX concludes this paper and provides a summary of key conclusions.

# II. SCALABILITY PROBLEMS AND STALLING EFFECT IN THE FITNESS FUNCTION

In this section, the problem of scalability [1], [49], [60], [85]–[87] and the stalling effect in the fitness function for an EHW system are outlined. The word scalable, or scalability, as written in [93], has been used to describe how the size of the problem will influence the performance of algorithms. EHW systems are not scalable because of the genotype length, which increases with problem size [61], and the time required for fitness evaluation, which increases rapidly with the size of the desired evolvable circuits.

The length of the genotype increases with the number of logic gates used during the evolution and the level of permitted connectivity between logic gates. The time necessary for fitness evaluation is not scalable because it is exponentially dependent on the number of inputs of the system that should be evolved. If the number of inputs increases linearly, the number of input—output combinations, which represent the description of the digital logic circuits problem, increases by a power of 2. Consequently, as the number of inputs increases, the system needs more time to produce new potential solutions, to evaluate them, and to select new individuals. The time required for the evolutionary process is given by the time for a single iteration  $(\mu)$  multiplied by the total number of iterations  $N_{\rm gen}$  needed to solve the problem, i.e.,

$$T_{\text{tot}} = \mu N_{\text{gen}}.$$

(1)

A possible method to reduce the total time for the evolutionary process is to introduce a new algorithm to reduce the number of generations needed or to reduce the time for a single iteration. The method proposed in this paper is able to accomplish both reductions.

Recently, the scalability problem has been investigated mainly in the following areas.

- Introducing and/or improving existing evolutionary processes [19], [74], [90].

- Developing multievolutionary processes using the principles of problem decomposition [68], [79], [84].

- Improving the genotype—phenotype mapping on biological development [85], [86], [88], [89], [91], [92]. This approach is achieving good results, for example, Gordon [86] was able to evolve a 12-bit parity function.

One approach to tackling scalability is the function-level EHW proposed in [42], [43], [64], and [65]. In function-level evolution, the synthesis of circuits is done based on higher functions as sin, adders, etc., instead of primitive gates such as AND and OR. Function-level evolution has proven to be successful in achieving the evolution of relatively complex tasks [64]. However, one of the main weaknesses of this approach is that it still requires human intervention to select the most appropriate functions for specific problems. Function-level evolution has been further extended in [67]. Although the proposed approach significantly reduces the number of generations required to obtain a fully functional solution, the evolvability [46], [48], [49] of logic circuits with a higher number of inputs remains the central issue.

Using decomposition strategies, a number of approaches intended to overcome scalability have been introduced, such as divide-and-conquer for EHW [79] and BIE [62], [84].

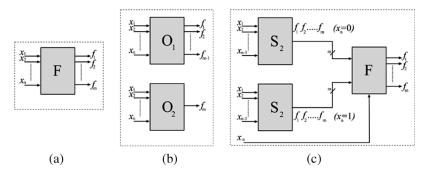

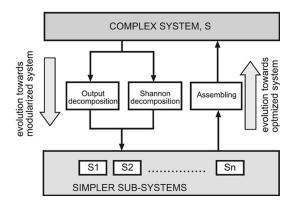

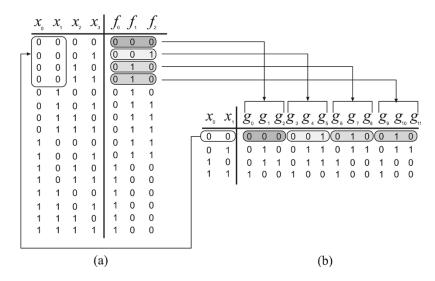

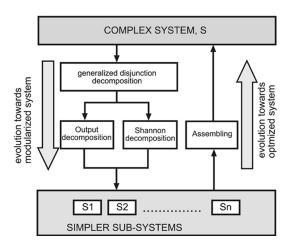

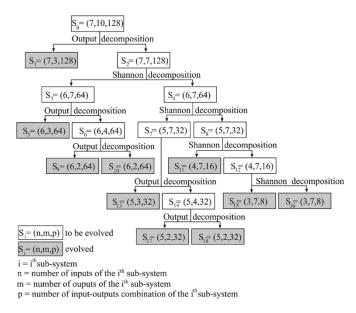

The divide-and-conquer method, also called increased complexity evolution [80], has been introduced to reduce the search space, which allows complete evolution of logic circuits with ten inputs by introducing the training vector and partitioned training set [70]. However, a significant weakness is also present, that is, the difficulties in defining the fitness function for the initial stages of evolution, which makes it less suitable for completely automatic systems. Furthermore, this method creates an unconditional constraint on the system: the top-down solving approach that does not allow the discovery of new designs. BIE [62], [84] is a completely automatic decomposition method that does not require any knowledge from the designer. However, it is not scalable to really large circuits due to the limitations of EHW-oriented output and Shannon decompositions (see Fig. 2). The first attempt to use BIE in EHW was achieved by the evolution of a seven-input ten-output logic function from MCNC benchmark [81]. BIE has been further improved by the introduction of new assembling techniques [82]. Although BIE and increased complexity evolution have proven to be successful in the evolution of logic circuits, the scalability problem remains to be one of the main issues in achieving the evolution of relatively large logic circuits in a reasonably short time. This paper addresses that issue.

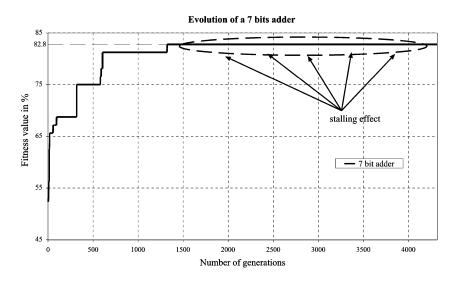

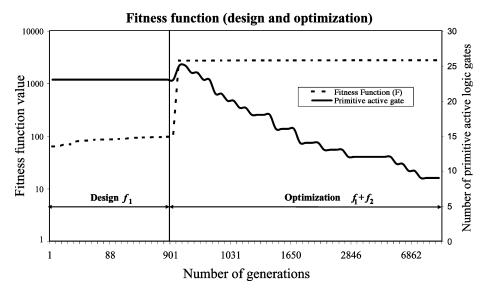

The problem of stalling effect in fitness functions is related to the nonimprovement of the fitness values during the evolutionary process. Fig. 3 shows the stalling effect of the fitness function during an evolutionary process for evolving a

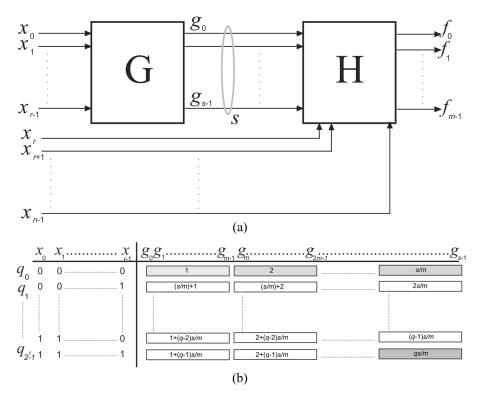

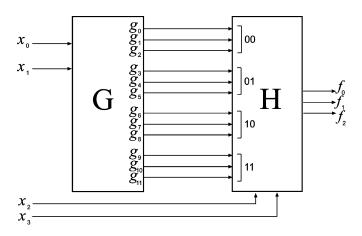

Fig. 2. Decomposition of logic circuits. (a) Initial system with n inputs and m outputs. (b) Output decomposition. (c) Shannon decomposition [62].

Fig. 3. Stalling effect in fitness function. Stalling effect in fitness function refers to a nonimprovement of the fitness value during the evolution process. In this graph, the stalling effect during an evolution of a seven-bit adder is shown.

seven-bit adder using  $(1+\lambda)$  ES. It may be observed that when the fitness function reaches 82.8% the stalling effect occurs. It means that the EA chosen and/or the initial configuration for solving that particular problem are not suitable.

#### III. BENCHMARKS

In this paper, several combinational circuits have been considered for use in simulations. First of all, the benchmarks usually used within the EHW community were considered, i.e., multipliers, used in [13], [44], [49], [70], [88], [94], and [95], and parity circuits, used in [30], [85]–[87], and [108].

Then, the MCNC benchmark [81], usually used by the logic design community, was taken into account. Finally, simple logic circuits with randomly generated truth tables were considered. The rationale for choosing several benchmarks is that it is beneficial to be able to compare the method proposed here with other existing methods in order to establish its contribution.

# IV. EXTRINSIC EHW

In this section, an explanation of the system used to evolve combinational logic circuits is given. The EA that has been used and the chromosome representations, fitness function, genetic operators, and BIE are presented.

#### A. Description of the Algorithm

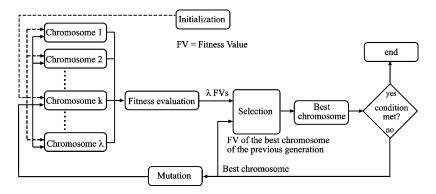

The EA used for the simulation is the well-known  $(1 + \lambda)$ ES already tested for its in performance in [24], [25], [33], and [83], where  $\lambda$  represents the population size (see Fig. 4). First, all the chromosomes are randomly initialized. Second, the fitness value of each individual is computed. Third, the fittest individual is selected. Fourth, the previously selected individual is used to test if the conditions to stop the process have been met. These conditions are: the fitness value of the chromosome is 100% or the number of generations has reached the maximum value set by the user for that particular experiment. If the conditions are not met, a new population will be generated by mutating the best chromosome (selected at the third step)  $\lambda$ times in order to obtain other  $\lambda$  individuals. In the next cycle, all  $\lambda$  newly created chromosomes are evaluated, the fitness value of each of them is compared with the fitness value of the best chromosome of the previous generation, and the best of these  $(1 + \lambda)$  individuals is selected.

#### B. Chromosome Encoding

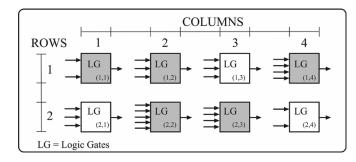

The chromosome defines the structure of the logic circuit and the connectivity between logic gates. In our approach, the logic circuit has been presented as a rectangular array of logic cells. The type of each logic cell is randomly chosen from the set of

Fig. 4. Schema of  $(1 + \lambda)$  ES.

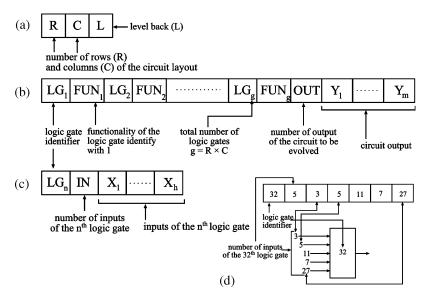

Fig. 5. Chromosome's structure. (a) Geometry level. (b) Functional level. (c) Connection level. (d) Example of a chromosome at the connection level. In this example, the logic gate identified by the number 32 is considered. This logic gate has five inputs, which are taken from the outputs of the logic gates identified by the numbers 3, 5, 11, 7, and 27.

AND, OR, XOR, NOT, and MUX, where MUX is a multiplexer with two inputs and one control signal. The chromosome has been represented by a three-level structure.

- Geometry level [see Fig. 5(a)] contains information about the number of rows, the number of columns of the rectangular array, and the degree of internal connectivity, also referred to as level-back parameter [34]. The level-back parameter defines how many columns of cells to the left of the current column may have their outputs connected to the inputs of the current cell.

- Functional level [see Fig. 5(b)] describes the array of cells and determines the circuit's outputs.

- Connection level [see Fig. 5(c)] represents the structure of each cell in the circuit and the connections between them.

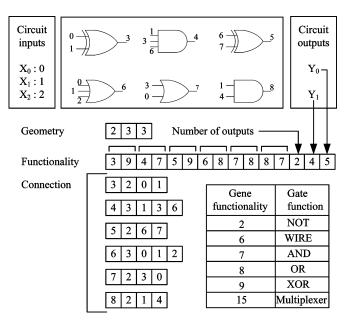

In Fig. 6, an example of chromosome encoding for a circuit layout with three inputs and two outputs is given. The circuit layout is a circuit with two rows and three columns, and the level back is set to three; therefore, the chromosome at geometry level is "2," "3," and "3." The chromosome at functional level encodes the array of cells. For example, the logic gate identified by the output "3" is an XOR gate. XOR is encoded with

Fig. 6. Example of a chromosome encoding.

the number "9." Thus, the first two cells of this chromosome are "3" and "9." The logic gate with output "4" is an AND gate (encoded with the number "7"); thus, the next two cells of the functional level's chromosome are "4" and "7." All the other logic gates are encoded in the same way. The last two cells of that chromosome contain the outputs of the circuit (in this case, the outputs of the circuit are taken from the output of the logic gates "4" and "5").

The chromosome at connection level identifies the logic gates, its number of inputs, and from which gate's output those inputs are taken. The chromosome of the first logic gate (first row, first column) contains "3" (which is the logic gate identifier), then "2" (which means that circuit has two inputs), and then "0" and "1," which means that one input is taken from  $X_0$  and the other from  $X_1$ . All the other five logic gates are encoded in the same way.

#### C. Fitness Function

The fitness function evaluates the evolved circuits in terms of their functionality. The fitness function selected for the experiments has two main criteria, namely; 1) design, and, once the circuit is fully functionally evolved, 2) optimization, which leads to reduced numbers of active logic gates used in the circuit configuration.

The fitness function  $f_{\text{tot}}$  is calculated as

$$f_{\rm tot} = \begin{cases} f_1, & \text{if } f_{\rm tot} \le 100 \text{ design} \\ f_1 + f_2, & \text{if } f_{\rm tot} > 100 \text{ optimization} \end{cases}$$

(2)

where  $f_1$  is a design criterion that defines the percentage of correct output bits produced by the evolved circuit after the application of all possible input combinations.  $f_2$  is the optimization criterion for the optimization stage.

The fitness function for the functionality of the evolved circuit  $f_1$ , or the so-called design criterion, has been calculated as

$$f_1 = 100 - \frac{100}{mp} \sum_{f_c=0}^{2^n - 1} \sum_{i=0}^{m-1} |y_i - d_i|$$

(3)

where m and n are the number of outputs and inputs of the given logic function, respectively, p is the number of input-output combinations,  $y_i$  is the ith digit of the output combination produced by the evaluation of the circuit,  $d_i$  is the desired output for the fitness case  $f_c$ , and  $|y_i - d_i|$  is the absolute difference between the actual and the required outputs.

The fitness function for the optimization stage has been calculated below, where  $N_{\rm LG}$  is the number of total logic gates present in the chromosome and is equal to the number of rows multiplied by the number of columns of the chromosome.  $N_{\rm PLG}^{\rm max}$  is the number of primitive logic gates necessary for building the logic gate with the highest number of inputs present inside the chromosome. Fig. 7 shows how to decompose a logic gate with four inputs. Therefore, if a logic gate has four inputs, the number of primitive logic gates necessary to build it is 3.  $N_{\rm row}$  and  $N_{\rm col}$  are the number of rows and columns of the chromosome, respectively.  $N_{\rm PLG}_{(i,j)}$  is the number of primitive

Fig. 7. Decomposition of a logic gate with four inputs into primitive logic gates.

Fig. 8. Example of a possible chromosome configuration.

logic gates necessary to build the (i, j)th logic gates.  $N_{\text{PLG}_{(i,j)}}$  is 0 if the (i, j)th logic gate is unconnected, i.e.,

$$f_2 = N_{\text{LG}} N_{\text{PLG}}^{\text{max}} - \sum_{1=1}^{N_{row}} \sum_{j=1}^{N_{\text{col}}} N_{\text{PLG}_{(i,j)}}.$$

(4)

An example of how the fitness function for a chromosome during the optimization stage is calculated is given below. Suppose that the chromosome in examination is a rectangular array of two rows and four columns (see Fig. 8) and for a particular configuration the highlighted logic gates are connected (see Fig. 8). Therefore, the total number of logic gates  $N_{\rm LG}$  is two rows multiplied by four columns, so  $N_{\rm LG}=8$ .

The logic gate with the highest number of inputs is the cell marked with index (2, 2), which contains five inputs; consequently,  $N_{\rm PLG}^{\rm max}=4$ . The fitness function for the optimization stage can be calculated as

$$f_2 = N_{LG} \times N_{PLG}^{max} - \sum_{i=1}^{N_{row}} \sum_{j=1}^{N_{col}} N_{PLG_{(i,j)}}$$

$$= 8 \times 4 - (1 + 2 + 0 + 3 + 0 + 4 + 3 + 0) = 19. \quad (5)$$

Fig. 9 shows the behavior of the fitness function during the evolution of functionality for the function

$$f = \lceil sqrt(x) \rceil \tag{6}$$

with four inputs and three outputs. In Fig. 9, two different stages are noticeable. The first shows the design of the function, so with each generation the fitness function value increases until it reaches 100%; therefore, the functionality of the circuit is completely evolved. During the first stage, the fitness function has been calculated using (3). The second stage starts just after the circuit is evolved. This stage performs the optimization of evolved circuits by reducing the number of active logic gates. Furthermore, during this stage, the fitness function, as

Fig. 9. Fitness function behavior. This graph shows the effect of the use of the selected fitness function during the evolution of a logic circuit. When the fitness value reaches 100% (functionality evolved), the optimization process begins.

Fig. 10. BIE approach.

calculated using (4), also increases its value because the circuit is better optimized.

### D. BIE

BIE [62], [84] operates by gradually decomposing a complex system into a series of simpler ones when the evolution does not bring any improvement in terms of fitness function value (see Fig. 10). These simpler blocks are evolved separately and then merged together once completely developed. If, during the evolution of each single subsystem, the stalling effect in the fitness function (see Fig. 3) occurs again, the single subcircuits will be decomposed again and again until all the subcircuits are simple enough to be evolved. The systems are decomposed by using Shannon and output decomposition (see Fig. 2). Evolution occurs on both sides. First toward modularization (having simpler and smaller logic circuits) and second toward an optimized system by assembling the simpler subcircuits together. This system is completely automatic and does not require any human intervention.

# E. Genetic Operators

Gene mutation and elitism [21] have been used in our extrinsic EHW system. Elitism ensures that the best individual of one

| Number of g   | generations        | 800.000                                    |  |  |  |

|---------------|--------------------|--------------------------------------------|--|--|--|

| Population s  | size, λ            | 5                                          |  |  |  |

| Number of     | runs per each      | For circuits with up to 4 inputs 100 runs. |  |  |  |

| experiment    |                    | For circuits with 5 and 6 inputs 50 runs.  |  |  |  |

| Elitism is ap | plied              |                                            |  |  |  |

| Gene mutati   | on rate            | 0.05                                       |  |  |  |

|               | Rows               | 10                                         |  |  |  |

| Circuit       | Columns            | 10                                         |  |  |  |

| layout        | Level Back<br>[34] | 10                                         |  |  |  |

generation is transferred to the next one. The mutation operator is involved in changing the value of some genes inside the chromosome. The aim of this operation is to bring more change (diversity) into the population. By increasing the mutation rate, the genetic search will be transformed into a random search but will help to reintroduce lost genetic material [22].

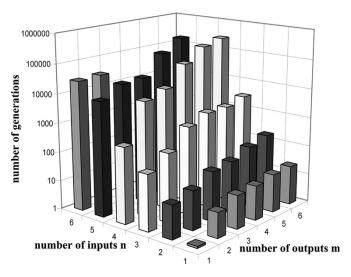

# V. LIMITATIONS OF EHW EVOLUTION

In order to identify the limitations of the previous systems, a number of experiments have been carried out. The purpose of these experiments was to quantify how the performance of the evolutionary process is dependent on the complexity of the tasks used. Logic circuits have been evolved using the extrinsic EHW approach with  $(1 + \lambda)$  ES described in detail in the previous section, with  $\lambda = 5$ . Each logic circuit, randomly generated, has been evolved either 50 or 100 times, and the average number of generations needed for each run has been reported. The initial configuration used for evolving the logic circuits has been set out in Table II, where all the parameters for the ES are outlined. The obtained results were classified according to the number of inputs, number of outputs of logic circuits, and number of generations required to evolve such circuits. In Fig. 1, the relationship between the dimension of the circuits and the required number of generations in order to evolve them has been considered. The experimental results have shown that the number of generations required in order to evolve a

Fig. 11. Average number of generations required to evolve logic circuits with n inputs and m outputs using  $(1 + \lambda)$  ES.

logic circuit is mainly dependent on the number of inputs. The system set-up together with the EHW algorithm used was able to evolve only the circuit for which the results are given in Fig. 11. The considered system has not been able to evolve more complex logic circuits. Based on the obtained results, one may conclude that there is a need for the development of a method that would concentrate on the input decomposition for EHW systems. That method is proposed in the next section. The experimental results prove that such a method will tackle the scalability problem better than the methods focused on output decomposition. This paper is devoted to proposing that method.

Therefore, a new system that is capable of reducing the number of required generations and at the same time improving the fitness values and evolving larger logic circuits has been introduced.

# VI. GENERALIZED DISJUNCTION DECOMPOSITION

In this section, the proposed method, GDD, which speeds up the evolutionary process and optimizes the logic circuit, is explained. This method improves the scalability for evolving logic circuits. This method has been introduced as a result of the limitation of EHW evolution demonstrated in the previous section: the number of generations required to evolve a circuit is mainly dependent on the number of inputs rather than on the number of outputs.

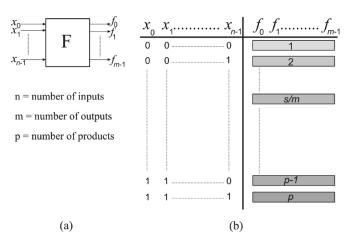

# A. Proposed Method

This method is based on rewriting the truth table in such a way that the inputs needed to describe the system are decomposed in two parts. Supposing that a system with n inputs and m outputs, see Fig. 12(a), should be evolved using either the extrinsic EHW approach previously described or other EAs. The functionality of this system can be described by the truth table given in Fig. 12(b), where  $p=2^n$  is the number of products (or the so-called number of input–output combinations). The system depicted in Fig. 12(a) can be decomposed into two subsystems as shown in Fig. 13(a).

Fig. 12. General description of logic circuits.

Subsystem G with r inputs and s outputs represents the evolvable part of the newly created system, where

$$s = m \times 2^{n-r} \tag{7}$$

and subsystem H with (s + n - r) inputs and m outputs represents the fixed part of the circuit that is generated using multiplexers. This part does not participate in the evolutionary process. The structure of this subcircuit depends on the number of used inputs and outputs. The next section gives a description of the system H. The decomposition of the system F into the two subsystems (G and H) is done automatically. At the moment, the user decides how many inputs G should have. Then the initial system F, defined by its truth table, is decomposed. Software in C++ has been written to accomplish this decomposition. Subsystem G can be evolved using either the traditional EHW approach or any other scalable approach such as divide-and-conquer, BIE, etc. The complexity of the evolutionary process will depend on the type of method used. Let us consider the process of generating the truth table for subsystem G. Let us assume that r should be always less than n(r < n), where r is the number of inputs in the G subsystem and n is the number of inputs in the initial system. The new truth table, shown in Fig. 13(b), has been calculated by applying the following procedure.

- Generation of all the input combinations of the truth table G.

- Identification, per each input combinations, of the truth table G, s/m output combinations on truth table F, wherever the input combinations of the truth table G match in sequence the input combinations of the initial system (truth table F).

- The outputs, of the initial system (truth table F) previously identified, become the outputs of the reduced truth table (output of G).

#### B. Multiplexer Part

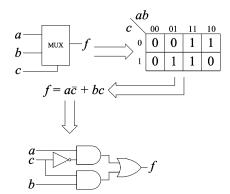

In this section, the complexity of subsystem H, the multiplexer part, is shown. A multiplexer with two inputs and one control signal is composed of four logic gates: one NOT, two AND, and one OR, as shown in Fig. 14.

Fig. 13. (a) Proposed decomposition of the initial logic circuit. r and g refer to the number of inputs and outputs of the reduced subsystem, respectively. (b) Truth table of the evolved part of the proposed subsystem.

Fig. 14. Multiplexer with one control signal and how it is built with logic gates.

Fig. 15. Multiplexer with two control signals.

In Fig. 15, a multiplexer with two control signals is shown, as well as the process for constructing it. The number of logic gates required for a generic multiplexer is given by

$$N_{\rm lg} = 4(2^c - 1) \tag{8}$$

where  $N_{\rm lg}$  is the number of logic gates required to build the multiplexer with c control signals.

# C. Case Study

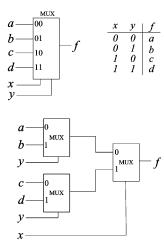

In this section, a case study regarding the generation of a truth table for subsystem G based on a simple example is considered. The truth table corresponding to the function given in (6) with four inputs and three outputs has been taken into account as an initial system to be decomposed. Therefore, the system F has n=4 [number of inputs  $(x_0,x_1,x_2,x_3)$ ], m=3 [number of outputs  $(f_0,f_1,f_2)$ ], and p=16 (number of products or input combinations).

The truth table of this function is shown in Fig. 16(a). Supposing that a subsystem G with only two inputs is to be generated. Therefore, the new system will have r=2 [number of inputs of the subsystem G  $(x_0,x_1)$ ] and s=12 [number of outputs of G, calculated based on (7)].

The new system is shown in Fig. 17. In order to generate the truth table of G, the procedure described in the previous section should be followed. First, all of the input combinations have been generated. Therefore, in this case, the input combinations of subsystem G are 4:  $(x_0, x_1) = (00), (01), (10), (11)$ . Second, for each input combination generated, the s/m output combinations of the initial system, wherever the input

Fig. 16. (a) Truth table of the initial function F. (b) Newly generated truth table for subsystem G.

Fig. 17. Decomposed subsystems obtained using generalized decomposition strategy. G is the evolvable part, and H is the multiplexer part.

combinations of the truth table G match in sequence the input combinations of F, should be identified. Let us identify the s/m=4 output combinations for the input combination  $(x_0,x_1)=(0,0)$ . The truth table F has been examined and the output of all the s/m input combinations that include (0,0) for  $(x_0,x_1)$  have been considered as outputs for subcircuit G when  $(x_0,x_1)=(0,0)$ . Once the outputs for the input combination  $(x_0,x_1)=(0,0)$  have been generated, the input combination (0,1) is considered. The truth table generated for subsystem G is given in Fig. 16(b).

The number of logic gates required to implement the fixed part (H-system) of the new system, based on (8), is 12.

### VII. SETTING PARAMETERS

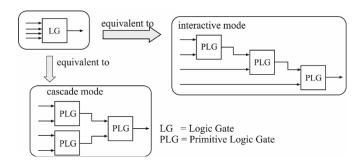

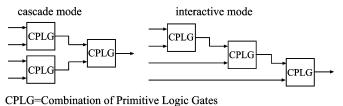

In this section, the system setup used to simulate the GDD is provided. The building blocks (a combination of primitive logic gates) that participate in evolutionary processes are AND, OR, XOR, NOT, and a multiplexer with two inputs and one control. Each logic gate has up to four inputs. The connections between building blocks inside the chromosome are interactive and in cascade mode (see Fig. 18). The mode in which they are

Fig. 18. Connections between building blocks in cascade and interactive mode. This figure explains how building blocks could be connected inside the circuit layout. The mode in which they are connected is automatically selected during the evolution.

connected is automatically selected. Furthermore, the output of a primitive logic gate of the nth columns could be connected to the input of a primitive logic gate of (n-l)th columns with l < n, where l represents the level back [34], and of (n+k)th columns, where  $k \geq 0$  and (n+k) is less than or equal to the number of columns of the circuit layout.

The truth tables used to describe the logic circuits are compatible with the Berkeley standard format for the physical description of a PLA [119].

The system used for evolving circuits with BIE is shown in Fig. 10, while for the GDD the schema is shown in Fig. 19.

In Table III, EA's parameters are given, where the number of generations refers to the number of cycles that each experiment has been evolved, population size refers to the number of different chromosomes, and gene mutation rate and elitism are the genetic operators used.

Each logic circuit has been evolved 100 times. For the given logic functions, the results are considered only if the logic circuit has a success rate of 100%. In Table IV, the features of the circuit layout used during evolution are given. The size of the chromosome (i.e., circuit layout) is chosen according with the complexity of the task being evolved. The more complex the task being evolved, the larger the circuit layout selected. Those parameters are not chosen according to previously published results; rather, they are tuned in order to obtain the best results. Definitions of the number of rows, columns, and level back have been provided in Section IV-B. The experiments are run with a

Fig. 19. System used for evolving logic circuits. The GDD is implemented into BIE.

TABLE III

INITIAL PARAMETER FOR THE EXPERIMENT CARRIED OUT

WITH BIE AND WITH THE PROPOSED APPROACH

| Termination criteria                  | 1,000,000 generations or 2000 generations without improvements of the fitness value |

|---------------------------------------|-------------------------------------------------------------------------------------|

| Population size                       | 5                                                                                   |

| Number of runs for each logic circuit | 100                                                                                 |

| Gene mutation rate                    | 0.05                                                                                |

| Elitism                               |                                                                                     |

desktop PC with a Pentium IV at 3.00 GHz and 768 MB of RAM. The software is written in C++.

## VIII. EXPERIMENTAL RESULTS

In this section, the results of the logic circuits evolved by using the GDD together with BIE are shown.

The aim of the experiments is to prove that the proposed method requires less generations and improves scalability for designing logic circuits in EHW in comparison with existing evolutionary computation methods. As the standard EHW approach, which does not use any decomposition technique, has high limitations in the evolution of relatively large logic circuits, it was decided not to compare the results of this method with the results obtained with GDD. The logic circuits analyzed in this paper have been taken from different sources: some of them were randomly generated, others were taken from MCNC benchmark [81], others describe the behavior of multipliers of different complexity, and others are even n-bit parity circuits traditionally used within the EHW community. In this section, another benefit of the use of GDD is also shown: GDD is capable of reducing the time required for a single iteration, therefore reducing the time required for the entire evolutionary process.

### A. Evolving Randomly Generated Logic Circuits

The circuits analyzed here are randomly generated. The complexity of these circuits is quite low; therefore, it is easy to evolve them. However, it has been decided to evolve those circuits in order to show how the use of GDD could bring some benefits to the evolution of small logic circuits over BIE.

TABLE IV

INITIAL DATA. DIMENSION SIZE AND CONNECTIVITY OF THE

CIRCUIT LAYOUT USED DURING SIMULATIONS

| C!!4            | Circuit la  | yout used        |                  |

|-----------------|-------------|------------------|------------------|

| Circuit<br>name | Number      | Number of        | Lavel Dools [24] |

| name            | of Rows     | Columns          | Level Back [34]  |

|                 | Logic circu | its randomly g   | enerated         |

| 6-5             | 3           | 80               | 80               |

| 6-4             | 3           | 80               | 80               |

| 6-4             | 10          | 10               | 10               |

| 6-3             | 10          | 10               | 10               |

| 6-2             | 10          | 10               | 10               |

| 6-1             | 10          | 10               | 10               |

| 6-5             | 10          | 10               | 10               |

|                 | Mu          | ltiplier circuit | s                |

| Mult3           | 10          | 10               | 10               |

| Mult4           | 10          | 10               | 10               |

| Mult5           | 3           | 80               | 80               |

| Mult6           | 3           | 80               | 80               |

|                 | Eve         | n parity circui  | ts               |

| Party13e        | 3           | 80               | 80               |

| Parity14e       | 3           | 80               | 80               |

| Parity15e       | 3           | 80               | 80               |

| Parity16e       | 3           | 80               | 80               |

| Parity17e       | 3           | 80               | 80               |

| Logic cir       | cuits taken | from MCNC b      | enchmark library |

| Majority        | 10          | 10               | 10               |

| 9sym            | 3           | 80               | 80               |

| add2_7          | 10          | 10               | 10               |

| 5xp1            | 3           | 80               | 80               |

| addm4           | 3           | 80               | 80               |

| co14            | 3           | 80               | 80               |

| con1            | 3           | 80               | 80               |

| rd84            | 3           | 80               | 80               |

| t841            | 4           | 100              | 100              |

| cm162           | 3           | 80               | 80               |

| add6            | 3           | 80               | 80               |

| alu4            | 3           | 80               | 80               |

In Table V, the experimental results are shown. The circuits evolved with the GDD are better optimized and the number of generations is significantly reduced. In that table, all the characteristics of the circuits have been given: name, number of inputs, outputs, and products. For example, by looking at the logic circuit 6–4, it has six inputs, four outputs, and 64 input–output combinations. Then, the numbers of generations (average out of 100 runs and the best run) needed for evolving the logic circuits have been reported. The next two columns give the average and best times (values are expressed in seconds) for each experiment. The next two columns provide the value of the fitness function for the final optimized solutions. For circuits 6–4, it can be observed that it is evolved using BIE (first row, six inputs and four outputs) and a different configuration (four inputs and 16 outputs) is obtained using the GDD.

# B. Evolving Multipliers

The evolution of multipliers is a quite difficult task. Several researchers have recognized the importance of the evolution of these circuits, and in the past few years this benchmark has become widely used within the EHW community. In Table VI, experimental results regarding the evolution of multipliers are given. Like BIE, GDD is not able to evolve a six-bit multiplier within the maximum number of generations set for this experiment. Therefore, the maximum number of generations for this

TABLE V

EXPERIMENTAL RESULTS FROM BIE AND GDD, WHERE IN, OUT, AND P ARE THE NUMBER OF INPUTS, OUTPUTS, AND PRODUCTS IN THE

GIVEN LOGIC FUNCTION. EACH LOGIC CIRCUIT HAS BEEN EVOLVED 100 TIMES WITH A SUCCESS RATE OF 100%

| Info cir | cuit   |    |     |    | Experimental results – Logic circuits randomly generated |            |                                  |      |             |           |  |

|----------|--------|----|-----|----|----------------------------------------------------------|------------|----------------------------------|------|-------------|-----------|--|

|          |        |    |     |    | Number of g<br>performed                                 | enerations | Total time spen<br>experiment in | -    | Final fitne | ess value |  |

| name     | method | in | out | p  | average                                                  | best       | average                          | best | average     | best      |  |

| 6-5      | BIE    | 6  | 5   | 64 | 40,425                                                   | 26,381     | 1,194                            | 624  | 13,815      | 25,088    |  |

| 0-3      | GDD    | 4  | 20  | 16 | 16,121                                                   | 9,446      | 410                              | 257  | 15,658      | 17,931    |  |

| 6-4      | BIE    | 6  | 4   | 64 | 30,095                                                   | 14,587     | 1,099                            | 442  | 11,866      | 20,456    |  |

| 0-4      | GDD    | 4  | 16  | 16 | 10,507                                                   | 6,744      | 321                              | 159  | 23,937      | 34,030    |  |

| 6-3      | BIE    | 6  | 3   | 64 | 30,754                                                   | 16,099     | 366                              | 229  | 3,498       | 6,404     |  |

| 0-3      | GDD    | 4  | 12  | 16 | 8,251                                                    | 4,489      | 129                              | 64   | 7,458       | 10,972    |  |

| 6-2      | BIE    | 6  | 2   | 64 | 12,886                                                   | 4,160      | 289                              | 94   | 1,598       | 3,486     |  |

| 0-2 GI   | GDD    | 4  | 8   | 16 | 3,500                                                    | 564        | 54                               | 12   | 2,152       | 5,614     |  |

| 6-1      | BIE    | 6  | 1   | 64 | 10,784                                                   | 4,406      | 136                              | 59   | 1,483       | 3,887     |  |

| 0-1      | GDD    | 3  | 8   | 8  | 3,684                                                    | 1,575      | 62                               | 25   | 3,049       | 5,102     |  |

TABLE VI

EXPERIMENTAL RESULTS FROM BIE AND GDD. EACH LOGIC CIRCUIT HAS BEEN EVOLVED 100 TIMES WITH A SUCCESS RATE OF 100%. FOR THE EVOLUTION OF THE SIX-BIT MULTIPLIER, THE MAXIMUM NUMBER OF GENERATIONS WAS SET TO 3 000 000 BECAUSE OF THE DIFFICULTIES TO EVOLVE IT. ONLY THREE RUNS HAVE BEEN CARRIED OUT FOR THIS MULTIPLIER AS THE AVERAGE REQUIRED EVOLUTION TIME IS 48.48 h

| Info circuit Experimental results – Multipliers |            |    |     |      |                     |             |                                 |         |             |           |

|-------------------------------------------------|------------|----|-----|------|---------------------|-------------|---------------------------------|---------|-------------|-----------|

|                                                 |            |    |     |      | Number of performed | generations | Total time spe<br>experiment in | -       | Final fitne | ess value |

| name                                            | method     | in | out | р    | average             | best        | average                         | best    | average     | Best      |

| Mult3                                           | No.142 BIE | 6  | 6   | 64   | 21,948              | 9,030       | 288                             | 126     | 4,279       | 2,373     |

| Mulis                                           | GDD        | 4  | 24  | 16   | 9,156               | 4,434       | 123                             | 67      | 8,820       | 14,219    |

| Mult4                                           | BIE        | 8  | 8   | 256  | 146,663             | 117,495     | 1,718                           | 1,468   | 13,019      | 20,592    |

| Mult4                                           | GDD        | 6  | 32  | 64   | 87,411              | 70,999      | 1,040                           | 594     | 23,554      | 30,926    |

| Mult5                                           | BIE        | 10 | 10  | 1024 | 740,164             | 685,372     | 24,088                          | 17,458  | 48,786      | 52,860    |

| GDD                                             | GDD        | 8  | 40  | 256  | 506,347             | 482,789     | 16,033                          | 15,338  | 152,372     | 171,368   |

| Mult6                                           | BIE        | 12 | 12  | 4096 | Not evolved         |             |                                 |         |             |           |

| Mulio                                           | GDD        | 10 | 48  | 1024 | 2,665,547           | 2,582,678   | 174,528                         | 156,924 | 517,667     | 578,296   |

circuit was increased to 3 000 000. In [117], it has already been proven for one run that GDD is able to solve this multiplier, but only by using a higher number of generations. The six-bit multiplier is also evolved using another configuration of GDD, with nine inputs and 96 outputs. Three experiments have been carried out with this configuration, and the average number of generations required is 2536 135 while the average time per experiment is 32.00 h; a bit less than the configuration with ten inputs.

# C. Evolving Even n-Bit Parity Function

Parity functions are often used to check the accuracy of stored or transmitted binary data in computers because a change in the value of any one of its arguments toggles the value of the function. As a result of this sensitivity to its inputs, the parity function is difficult to learn [29]. This benchmark, as with the multipliers, is popular within the evolutionary computation community. The even n-bit parity circuit produces a response equal to the sum modulo 2 of its inputs. Table VII shows the experimental results for the evolution of those circuits. From that table, it can be observed that with the use of GDD the evolution of a large circuit is feasible. GDD is able to evolve

large even parity bit circuits never evolved before. The best parity bit circuit successfully evolved previously was presented in [86], and it was a 12-bit parity circuit. It was evolved using a developmental model based on a biological map between genotype and phenotype.

### D. Evolving Logic Circuits From MCNC Benchmark

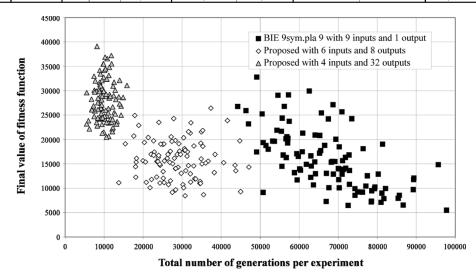

The experimental results reported in this section are those in relation to the evolution of circuits taken from the MCNC benchmark [81], [110]. This benchmark was first presented at the 1990 International Workshop on Layout Synthesis. Since then, several researchers within the GA community have used it as a test bench for floor planning [111], cell placement [112], [113], power consumption [114], etc. It is still not popular within the EHW community because of the complexities of those circuits. However, here, it has been decided to evolve those circuits in order to show that GDD has the capability to cope with these circuits. Figs. 20–23 show the relationships between the values of the fitness function, the number of generations, and the time spent for each experiment. "Reduced circuit" refers to a circuit that has been obtained by applying the proposed method to the original circuit. Each

TABLE VII

EXPERIMENTAL RESULTS FROM BIE AND GDD. THE LOGIC CIRCUITS PARITY 16E AND PARITY 17E HAVE BEEN EVOLVED TEN TIMES,

THE OTHERS 100 TIMES. ALL THE CIRCUITS HAVE BEEN EVOLVED WITH A SUCCESS RATE OF 100%

| Info circui  | t      |    |     |         | Experimental results – Parity Functions |             |                             |                          |             |           |

|--------------|--------|----|-----|---------|-----------------------------------------|-------------|-----------------------------|--------------------------|-------------|-----------|

|              |        |    |     |         | Number of g<br>performed                | generations | Total time sp<br>experiment | ent per each<br>in hours | Final fitne | ess value |

| name         | method | in | out | p       | average                                 | best        | average                     | best                     | average     | best      |

| Parity11e    | BIE    | 11 | 1   | 2,048   | 4,679                                   | 304         | 0.530                       | 0.089                    | 2,538       | 9,954     |

| GD           | GDD    | 7  | 16  | 128     | 17,509                                  | 2,313       | 0.223                       | 0.039                    | 12,613      | 36,701    |

| Parity12e    | BIE    | 12 | 1   | 4,096   | Not evolved                             |             |                             |                          |             |           |

| Parity12e    | GDD    | 8  | 16  | 256     | 17,571                                  | 2,210       | 0.374                       | 0.066                    | 13,323      | 34,727    |

| Parity13e    | BIE    | 13 | 1   | 8,192   |                                         |             | Not evo                     | lved                     |             |           |

| Parity13e    | GDD    | 9  | 16  | 512     | 7,631                                   | 2,562       | 0.270                       | 0.102                    | 9,601       | 18,021    |

| Parity14e    | BIE    | 14 | 1   | 16384   |                                         |             | Not evo                     | lved                     |             |           |

| Parity 14e   | GDD    | 10 | 16  | 1,024   | 15,526                                  | 3,753       | 0.451                       | 0.139                    | 6,375       | 22,450    |

| Domitro 15 o | BIE    | 15 | 1   | 32,768  |                                         |             | Not evo                     | lved                     |             |           |

| Parity15e    | GDD    | 10 | 32  | 1,024   | 27,422                                  | 7,147       | 1.878                       | 0.659                    | 34,143      | 76,996    |

| Parity16e    | BIE    | 16 | 1   | 65,536  | Not evolved                             |             |                             |                          |             |           |

| rainyloe     | GDD    | 10 | 64  | 1,024   | 70,100                                  | 40,912      | 4.667                       | 2.668                    | 50,412      | 87,020    |

| Parity17e    | BIE    | 17 | 1   | 131,072 |                                         |             | Not evo                     | lved                     |             |           |

| rainy1/e     | GDD    | 11 | 64  | 2,048   | 123,417                                 | 80,125      | 15.394                      | 10.6128                  | 88,568      | 117,127   |

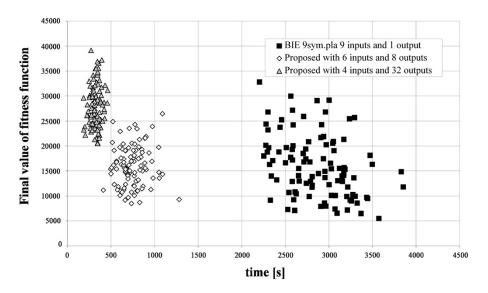

Fig. 20. Relationship between the final value of the fitness function reached at the end of each experiment and the number of generations required for evolving the circuit 9sym. The circuit has been evolved 100 times, and all the results are shown.

Fig. 21. Relationship between the final value of the fitness function reached at the end of each experiment and the CPU time required for evolving the circuit 9sym. The circuit has been evolved 100 times.

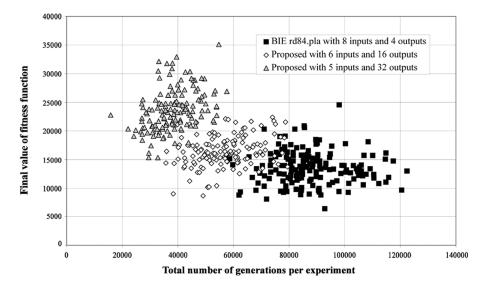

Fig. 22. Relationship between the final value of the fitness function reached at the end of each experiment and the number of generations required for evolving the circuit rd84. The circuit has been evolved 100 times.

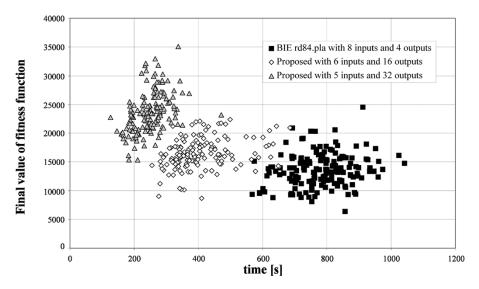

Fig. 23. Relationship between the final value of the fitness function reached at the end of each experiment and the CPU time required for evolving the circuit rd84. The circuit has been evolved 100 times.

graph compares the evolution results between the original logic circuits and two different configurations of the "reduced circuit." For all the evolved logic circuits, it has been observed that a smaller number of generations is required for the evolution of the "reduced circuits" and at the same time better values of fitness are achieved. The same results for the time required for each experiment have been found. For any of the given graphs, it can be seen that when the number of inputs is reduced the fitness value for each experiment is increased and the time and number of generations are reduced. In Table VIII, all the experimental results obtained by using BIE and GDD are shown. It should be noted that for the evolution of the circuit alu4, only five runs are analyzed and the maximum number of generations for those experiments was set at 2 000 000; this was done because of the high computational time required for the simulations. Even with this initial set up, BIE was not able to completely solve the task.

# E. Reduction of Time Required for a Single Iteration

Another benefit of GDD is that it is able to reduce the time required for a single iteration  $\mu$  [see (1)]. This leads to a reduction of the total time required for the entire evolutionary process.

To illustrate this advantage, the time required for a single iteration for circuits with different numbers of inputs has been calculated. The system set up for those simulations is a circuit layout with three rows and 80 columns and level back equal to the number of columns.

The logic circuit in examination was the 17-bit even parity. Using GDD, circuits with 16 inputs and two outputs, with 15 inputs and four outputs, and so on, down to a circuit with two inputs, were created, and those circuits were used as a test bench for this experiment. As can be observed from the results shown in Fig. 24, the required time for a single iteration increases with the number of inputs: going from 16.172 ms for a circuit with two inputs to 35.79 s for a circuit with 17 inputs.

TABLE VIII

EXPERIMENTAL RESULTS FROM BIE AND GDD. EACH LOGIC CIRCUIT HAS BEEN EVOLVED 100 TIMES, WITH THE EXCEPTION OF alu4,

WHICH HAS BEEN EVOLVED FIVE TIMES. ALL EXPERIMENTS HAVE REACHED A SUCCESS RATE OF 100%

| Info circ | uit               |    |     |                                 | Experimental results - Logic circuits from MCNC benchmark |                                                 |         |                     |         |         |  |

|-----------|-------------------|----|-----|---------------------------------|-----------------------------------------------------------|-------------------------------------------------|---------|---------------------|---------|---------|--|

|           |                   |    |     | Number of generations performed |                                                           | Total time spent per each experiment in seconds |         | Final fitness value |         |         |  |

| name      | method            | in | out | р                               | average                                                   | best                                            | average | best                | average | best    |  |

|           | BIE               | 9  | 1   | 512                             | 67,041                                                    | 44,261                                          | 2,852   | 2,204               | 15,976  | 32,790  |  |

| 9sym      | GDD               | 6  | 8   | 64                              | 28,741                                                    | 13,771                                          | 745     | 412                 | 15,971  | 26,448  |  |

|           | מעט               | 4  | 32  | 16                              | 10,142                                                    | 5,540                                           | 323     | 185                 | 28,034  | 39,128  |  |

|           | BIE               | 7  | 4   | 128                             | 28,121                                                    | 10,535                                          | 269     | 112                 | 3,036   | 5,268   |  |

| add2_7    | CDD               | 5  | 16  | 32                              | 11,665                                                    | 4,358                                           | 90      | 29                  | 7,465   | 14,190  |  |

|           | GDD $\frac{3}{4}$ | 4  | 32  | 16                              | 7,448                                                     | 4,541                                           | 52      | 32                  | 13,248  | 20,455  |  |

| 5 1       | BIE               | 7  | 10  | 128                             | 43,643                                                    | 22,623                                          | 1,878   | 1,003               | 16,994  | 30,008  |  |

| 5xp1      | GDD               | 5  | 40  | 32                              | 24,560                                                    | 13116                                           | 884     | 518                 | 51,659  | 77,001  |  |

| addm4     | BIE               | 9  | 8   | 512                             | 168,053                                                   | 127206                                          | 10,713  | 8,039               | 40,847  | 68,204  |  |

| addm4     | GDD               | 7  | 32  | 128                             | 132,414                                                   | 103563                                          | 4,908   | 3,753               | 73,027  | 94,339  |  |

| 14        | BIE               | 14 | 1   | 16,384                          | 184,476                                                   | 150,838                                         | 70,877  | 64,222              | 5,024   | 7,531   |  |

| co14      | GDD               | 10 | 16  | 1,024                           | 50,733                                                    | 14,139                                          | 6,240   | 3479                | 13,179  | 33,075  |  |

|           | BIE               | 7  | 2   | 128                             | 6,584                                                     | 2,177                                           | 286     | 126                 | 3,015   | 8,881   |  |

| con1      | GDD               | 5  | 8   | 32                              | 7,092                                                     | 2,307                                           | 212     | 79                  | 10,036  | 17,760  |  |

|           | עשט               | 3  | 32  | 8                               | 4,893                                                     | 2,553                                           | 136     | 71                  | 22,358  | 30,441  |  |

|           | BIE               | 8  | 4   | 256                             | 87,752                                                    | 58,640                                          | 781     | 568                 | 13,571  | 24,545  |  |

| rd84      | GDD               | 6  | 16  | 64                              | 56,764                                                    | 35,698                                          | 410     | 256                 | 16,473  | 22,388  |  |

|           | מעט               | 5  | 32  | 32                              | 38,533                                                    | 15,808                                          | 250     | 126                 | 23,701  | 35,104  |  |

| t841      | BIE               | 16 | 1   | 65,536                          |                                                           |                                                 | Not evo | lved                |         | •       |  |

| 1841      | GDD               | 9  | 128 | 512                             | 59,7469                                                   | 463,396                                         | 20,250  | 13,482              | 396,399 | 445,554 |  |

| cm162     | BIE               | 14 | 5   | 16,384                          |                                                           |                                                 | Not evo | lved                | •       |         |  |

| CIII 102  | GDD               | 10 | 80  | 1,024                           | 136,421                                                   | 103,305                                         | 12,167  | 9,060               | 54,913  | 71,887  |  |

| add6      | BIE               | 12 | 7   | 4,096                           |                                                           |                                                 | Not evo | lved                |         |         |  |

| audo      | GDD               | 9  | 56  | 512                             | 352,361                                                   | 270,375                                         | 21,652  | 17,278              | 76,360  | 85,417  |  |

| -1.4      | BIE               | 14 | 8   | 16,384                          |                                                           |                                                 | Not evo | lved                |         |         |  |

| alu4      | GDD               | 10 | 128 | 1,024                           | 1,369,394                                                 | 1,309,923                                       | 128,386 | 115,142             | 198,294 | 200,169 |  |

Fig. 24. Time per iteration for circuits with different numbers of inputs.

These experiments were performed with a personal computer with 768 MB of RAM and a Pentium IV processor at 3.00 GHz.

# F. Analysis of Results and Comparison to Techniques

In this section, an analysis of the obtained results is outlined. The experimental results have shown a reduction of the number

TABLE IX

REDUCTIONS, EXPRESSED IN PERCENTAGE, OF THE NUMBER OF

GENERATIONS, THE TIME SPENT, AND THE IMPROVEMENTS OF

THE FITNESS VALUE BY USING THE PROPOSED METHOD

COMPARED WITH BIE SOLUTIONS

|          |          |         | Improvements          | in percentages<br>BIE | of GDD over                    |

|----------|----------|---------|-----------------------|-----------------------|--------------------------------|

| Name     | in       | out     | Number of generations | Time                  | Fitness<br>function's<br>value |

|          |          | Logic   | circuits randomly     | generated             |                                |

| 6-5      | 6        | 5       | 60.12%                | 65.66%                | 13.34%                         |

| 6-4      | 6        | 4       | 65.09%                | 70.79%                | 101.73%                        |

| 6-3      | 6        | 3       | 73.17%                | 64.75%                | 113.21%                        |

| 6-2      | 6        | 2       | 72.84%                | 81.31%                | 34.67%                         |

| 6-1      | 6        | 1       | 65.84%                | 54.41%                | 105.60%                        |

| Lo       | ogic cir | cuits t | aken from MCNC        | benchmark li          | brary                          |

| Majority | 5        | 1       | 82.09%                | 52.94%                | 87.34%                         |

| 9sym     | 9        | 1       | 84.87%                | 88.67%                | 75.48%                         |

| add2_7   | 7        | 4       | 73.51%                | 80.67%                | 336.36%                        |

| 5xp1     | 7        | 10      | 43.73%                | 52.93%                | 203.98%                        |

| addm4    | 9        | 8       | 21.21%                | 54.19%                | 78.78%                         |

| co14     | 14       | 1       | 72.50%                | 91.20%                | 162.32%                        |

| con1     | 7        | 2       | 25.68%                | 52.45%                | 641.56%                        |

| rd84     | 8        | 4       | 56.09%                | 67.99%                | 74.64%                         |

|          |          |         | Multiplier circu      | ıits                  |                                |

| Mult3    | 6        | 6       | 58.28%                | 57.29%                | 106.12%                        |

| Mult4    | 8        | 8       | 40.40%                | 39.46%                | 80.92%                         |

| Mult5    | 10       | 10      | 31.59%                | 33.44%                | 212.33%                        |

of generations required to fully evolve combinational circuits for all the benchmarks used following a reduction in time spent performing the evolution.