School of Engineering & Design Electronic and Computer Engineering

# Power Line Network Automation Over IP

A thesis submitted for the degree of Master of Philosophy

**Dimosthenis** Trichakis

Brunel University January 2011

# Declaration

I declare that this thesis is my own work and has not been submitted in any form for another degree or diploma at any university or other institution of tertiary education. Information derived from the published work of others has been acknowledged in the text and a list of references is given.

(Date)

(Signature)

## Abstract

A smart home contains many kinds of devices, sensors and user interfaces. In order for these to communicate with each other and share information and processing power they need to be connected together. Thus, seamless networking and device interconnectivity is a fundamental requirement for a smart home.

Unfortunately, this requirement for compliance and compatibility still presents a difficult obstacle as there are numerous competing standards and technologies available today and some devices are completely without communication interface.

Current state-of-the-art smart homes are implemented with home based on Web servers in order to surpass the difficulties. Also, a more sophisticated implementation is based on middleware. These two methodologies are expensive to implement.

Our proposed system is cost-effective and does not require Web servers or any special hardware and has low complexity.

The novelty and the achievement of the thesis is the integration of homogeneous networks through IP. In addition, the system was built-in terms of software and hardware based on a new protocol.

# Acknowledgements

First I wish to thank my supervisor Dr Marios Hadjinicolaou and I am grateful to him for his expert help and support.

I wish to give many thanks to Dr. Manolis Antonidakis for his support and recommendations.

I wish to thank Mr. Iraklis Rigakis for his support.

I also thank Mr. P.Stivaris, my friend Mr. Christos Chousidis and colleague Mr. Vasilis Stauropoulos for their help and support.

I am also thankful to my family and relatives for their enduring support, especially to my love, Apostolia, for being that special one for me.

Finally, I would like to thanks all the staff of the Department of Electronic & Computer Engineering at Brunel University for their kind help.

To The Man,

before He becomes a Slave or a Master...

| Abstract                                      | II  |

|-----------------------------------------------|-----|

| Acknowledgements                              | III |

| Acronyms                                      | XII |

| Chapter 1 Introduction                        | 1   |

| 1.1 Overview                                  |     |

| 1.2 Scope of the Thesis                       |     |

| 1.3 State of the Art                          | 3   |

| 1.4 Contributions                             | 4   |

| 1.5 Organization of the Thesis                | 6   |

| Chapter 2 Internet Protocol Suite             | 7   |

| 2.1 Introduction                              | 7   |

| 2.2 ISO/OSI Network Model                     | 7   |

| 2.2.1 Physical Layer                          | 8   |

| 2.2.2 Data Link Layer                         | 8   |

| 2.2.3 Network Layer                           | 8   |

| 2.2.4 Transport Layer                         | 9   |

| 2.2.5 Session Layer                           | 9   |

| 2.2.6 Presentation Layer                      | 9   |

| 2.2.7 Application Layer                       | 9   |

| 2.3 TCP/IP Network Model                      | 9   |

| 2.3.1 IP                                      |     |

| 2.3.2 TCP                                     | 13  |

| 2.3.3 UDP                                     | 16  |

| Chapter 3 Description of Open Power Line HAPs |     |

| 3.1 Introduction                              |     |

| 3.2 ISO/OSI Network Model in Smart Homes      |     |

| 3.3 European Regulation Basics in PLCs        | 19  |

| 3.4 Description of X10 Power Line Protocol    | 20  |

| 3.4.1 Media Layer                             |     |

| 3.4.2 Physical Layer                          | 21  |

| 3.4.3 Data Link Layer                         |     |

# **Table of Contents**

| 3.5 Description of INSTEON                       | 24 |

|--------------------------------------------------|----|

| 3.5.1 Media Layer                                | 25 |

| 3.5.2 Physical Layer                             | 26 |

| 3.5.3 Data Link Layer                            |    |

| 3.6 Universal Powerline Bus(UPB)                 | 30 |

| 3.6.1 Media Layer                                | 30 |

| 3.6.2 Physical Layer                             | 30 |

| 3.6.3 Data Link Layer                            | 31 |

| 3.7 EIB/KNX                                      |    |

| 3.7.1 Media Layer                                | 34 |

| 3.7.2 Physical Layer                             | 34 |

| 3.7.3 Data Link Layer Type PL110 & Network Layer |    |

| 3.7.4 Transport Layer                            |    |

| 3.7.5 Application Layer                          |    |

| 3.8 LonTalk                                      |    |

| 3.8.1 Media Layer                                |    |

| 3.8.2 Physical Layer                             |    |

| 3.8.3 Data Link Layer                            | 40 |

| 3.8.4 Network Layer                              | 41 |

| 3.8.5 Transport Layer                            | 41 |

| 3.8.6 Session Layer                              | 42 |

| 3.8.7 Application and Presentation Layers        | 42 |

| Chapter 4 IP Convergence of PLN's HAPs           | 43 |

| 4.1 Introduction                                 | 43 |

| 4.2 The Transport Mechanism                      | 43 |

| 4.3 HAPoIP Layer                                 | 44 |

| 4.3.1 KNXnet/IP and LON/IP                       | 45 |

| 4.3.2 X10/IP, INSTEON/IP and UPB/IP              | 45 |

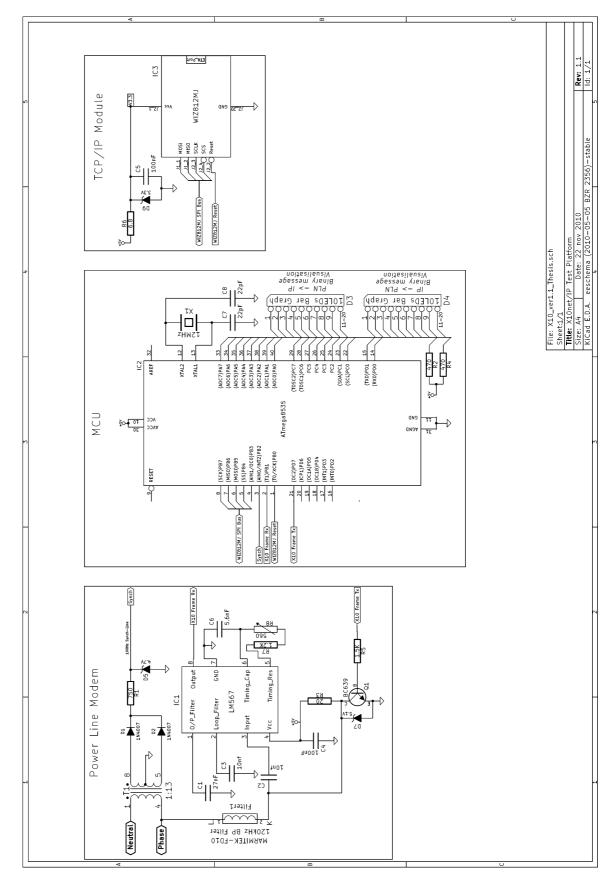

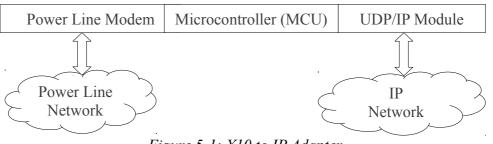

| Chapter 5 Hardware Design of the Test Platform   | 50 |

| 5.1 Introduction                                 | 50 |

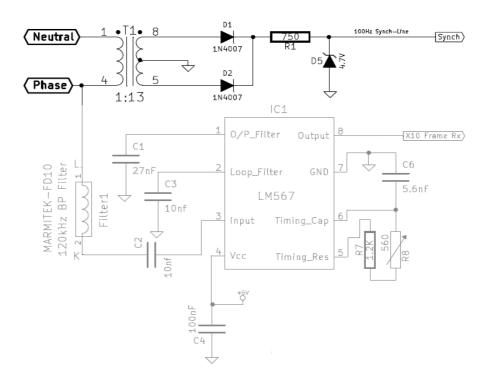

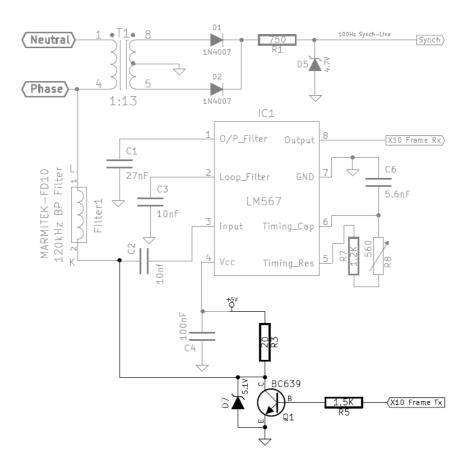

| 5.2 Power Line Modem                             | 50 |

| 5.2.1 Carrier Band Pass Filter                   | 51 |

| 5.2.2 120 kHz Frequency Decoder                  | 51 |

| 5.2.3 Mains Zero Crossing Detector                  |      |

|-----------------------------------------------------|------|

| 5.2.4 X10 Transmission Amplifier and Surge Protecti | on55 |

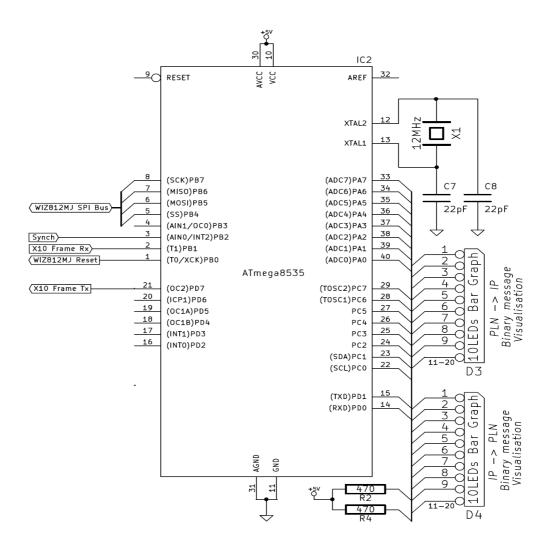

| 5.2 MCU                                             |      |

| 5.4 UDP/IP Module                                   | 61   |

| Chapter 6 Software Design of the Test Platform      | n66  |

| 6.1 Introduction                                    |      |

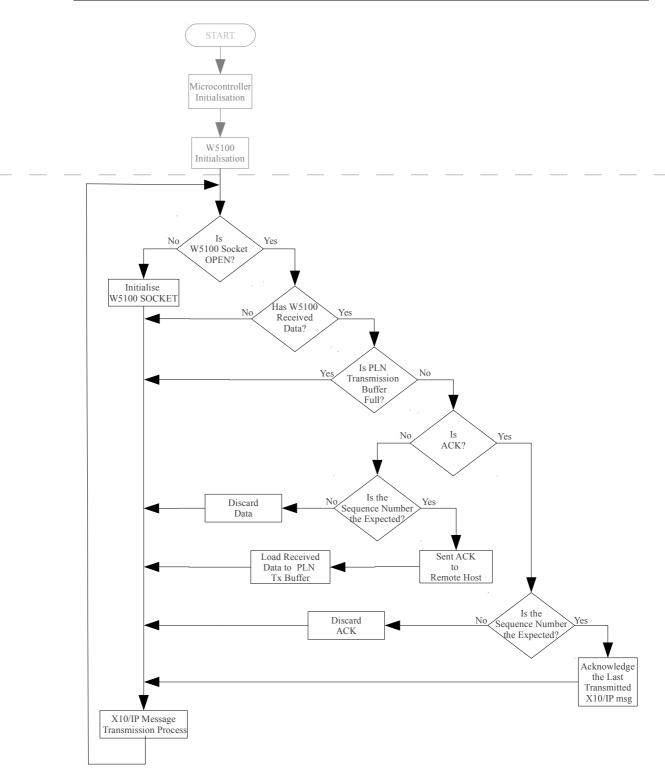

| 6.2 Platform Initialisation                         |      |

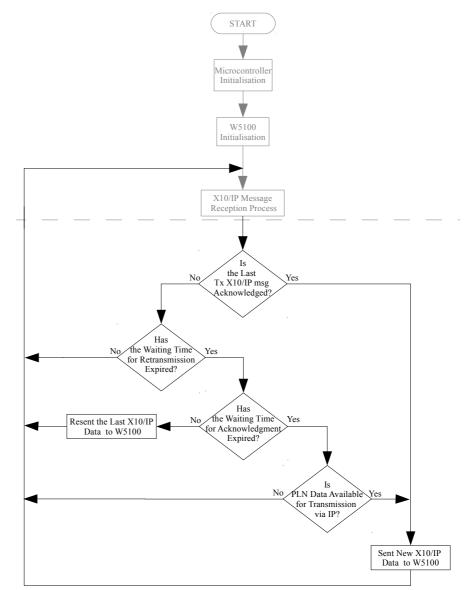

| 6.3 X10/IP Message Reception Process                |      |

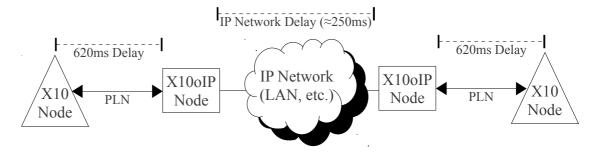

| 6.4 X10/IP Message Transmission Process             | 69   |

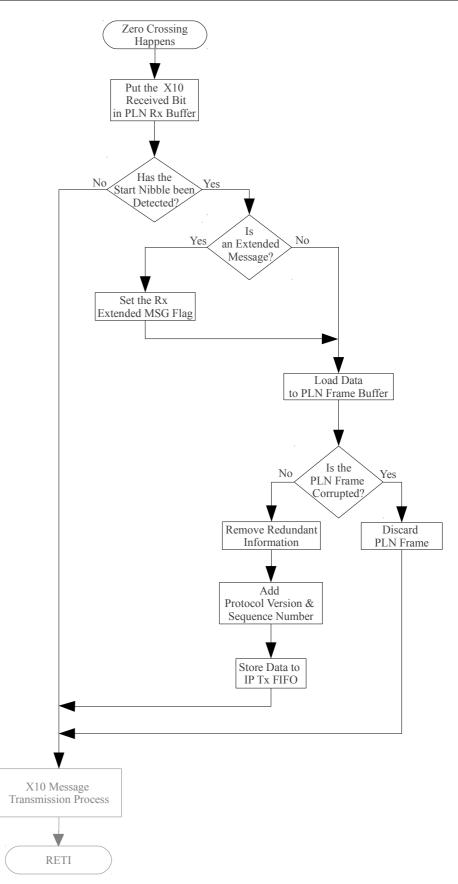

| 6.5 X10 Message Reception Process                   | 71   |

| 6.6 X10 Message Transmission Process                |      |

| 6.7 PLN Access Protocol                             | 74   |

| Chapter 7 Test and Validation                       | 75   |

| 7.1 Introduction                                    | 75   |

| 7.2 Software Tools and Devices                      |      |

| 7.2.1 CM15Pro <sup>тм</sup>                         |      |

| 7.2.2 LM12 <sup>TM</sup> and AM12 <sup>TM</sup>     |      |

| 7.2.3 ActiveHome Pro <sup>™</sup>                   |      |

| 7.2.4 Ostinato                                      |      |

| 7.2.5 Wireshark                                     |      |

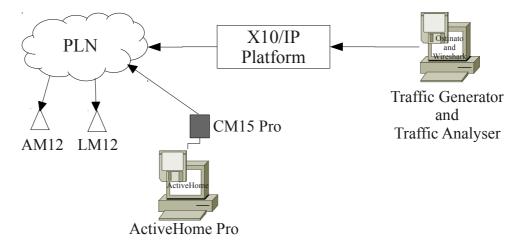

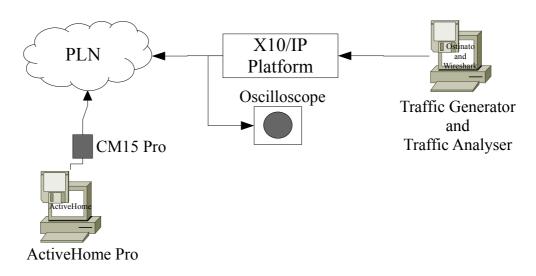

| 7.3 Validation of the Platform                      |      |

| 7.3.1 X10 Interface Tests                           |      |

| 7.3.2 X10/IP Layer Operation Tests                  |      |

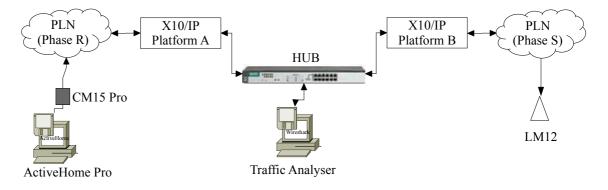

| 7.4 Platform Integration to IP Network              |      |

| Chapter 8 Conclusions and Further Work              | 84   |

| 8.1 Conclusions                                     |      |

| 8.2 Further Work                                    |      |

| References                                          | 86   |

| APPENDIX A                                          |      |

| APPENDIX B                                          |      |

|                                                     |      |

| APPENDIX C                                          |      |

# **List of Figures**

| Figure 1-1: A schematic overview of the smart home technical system infrastructure | 1  |

|------------------------------------------------------------------------------------|----|

| Figure 1-2: Power Line Automation over IP                                          | 2  |

| Figure 1-3: Web Server Solution                                                    | 3  |

| Figure 1-4: Example of Middleware Solution                                         | 4  |

| Figure 1-5: PLN and IP planes                                                      | 5  |

| Figure 1-6: Far-End Communication                                                  | 5  |

| Figure 2-1: TCP/IP model versus OSI model                                          | 10 |

| Figure 2-2: IP Datagram Encapsulation.                                             | 10 |

| Figure 2-3: TCP Header                                                             | 15 |

| Figure 3-1: X10 Transmission (bits: 110)                                           | 21 |

| Figure 3-2: X10 Standard Frame                                                     | 22 |

| Figure 3-3: X10 Standard Message and Standard Frame Transmission                   | 23 |

| Figure 3-4: Extended Message Format                                                | 24 |

| Figure 3-5: INSTEON Network Implementation Example                                 |    |

| Figure 3-6: INSTEON frames over 60 Hz PLN.                                         | 26 |

| Figure 3-7: INSTEON's Messages                                                     | 27 |

| Figure 3-8: INSTEON messages Fragmentation                                         | 29 |

| Figure 3-9: Start and Body Frame Structures                                        | 29 |

| Figure 3-10: Frames Group Transmission                                             | 29 |

| Figure 3-11: UPB Pulse Position(60 Hz)                                             | 31 |

| Figure 3-12: UPB Frame                                                             | 31 |

| Figure 3-13: UPB Frame Header                                                      | 32 |

| Figure 3-14: PL110 Frame                                                           | 36 |

| Figure 3-15: LPDU in Standard Frame                                                | 37 |

| Figure 3-16: LPDU in Extended Frame                                                | 37 |

| Figure 3-17: Acknowledgment Frame                                                  | 37 |

| Figure 3-18: TPDU                                                                  | 38 |

| Figure 3-19: LonTalk Protocol Stack                                                | 39 |

| Figure 3-20: Power Line Frame                                                      | 40 |

| Figure 3-21: Encoded LPDU                                                          | 40 |

| Figure 3-22: LPDU                                                                  | 41 |

| Figure 3-23: NPDU                                                                  | 41 |

| Figure 4-1: HAPoIP Adaptation Layer                                          | 44 |

|------------------------------------------------------------------------------|----|

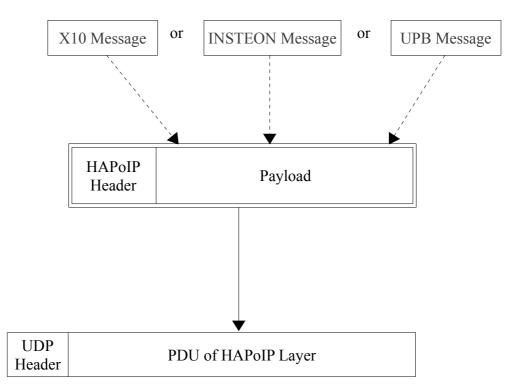

| Figure 4-2: HAPoIP Packet                                                    | 46 |

| Figure 4-3: HAPoIP Encapsulation Method                                      | 46 |

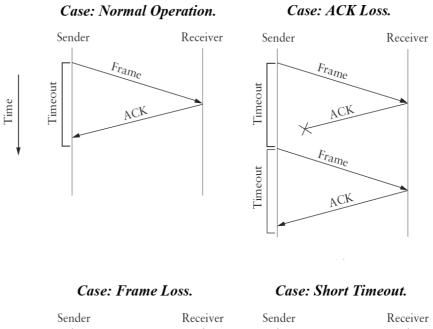

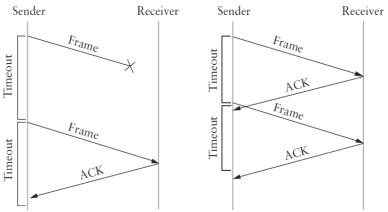

| Figure 4-4: Stop and Wait ARQ Protocol Timeline for Four Different Scenarios | 47 |

| Figure 4-5: Timeline for Stop and Wait Protocol with 1-bit Sequence Number   | 48 |

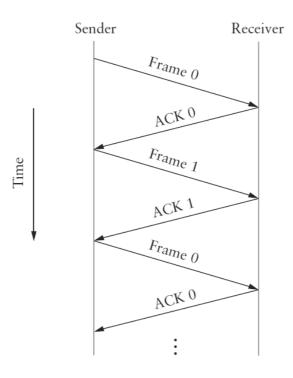

| Figure 4-6: End-to-End Delay and ARQ Implementation                          | 49 |

| Figure 4-7: Packet Structure                                                 | 49 |

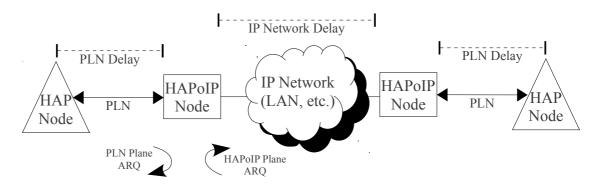

| Figure 5-1: X10 to IP Adapter                                                | 50 |

| Figure 5-2: Mains Coupler                                                    | 51 |

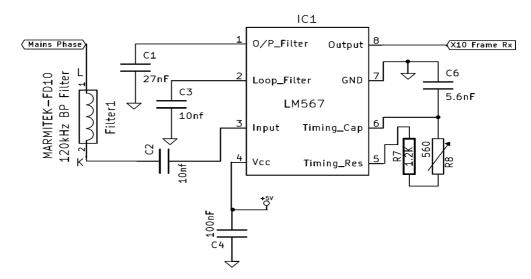

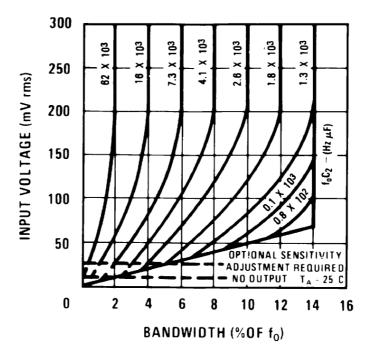

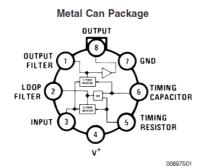

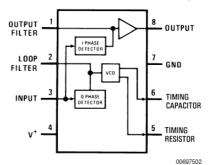

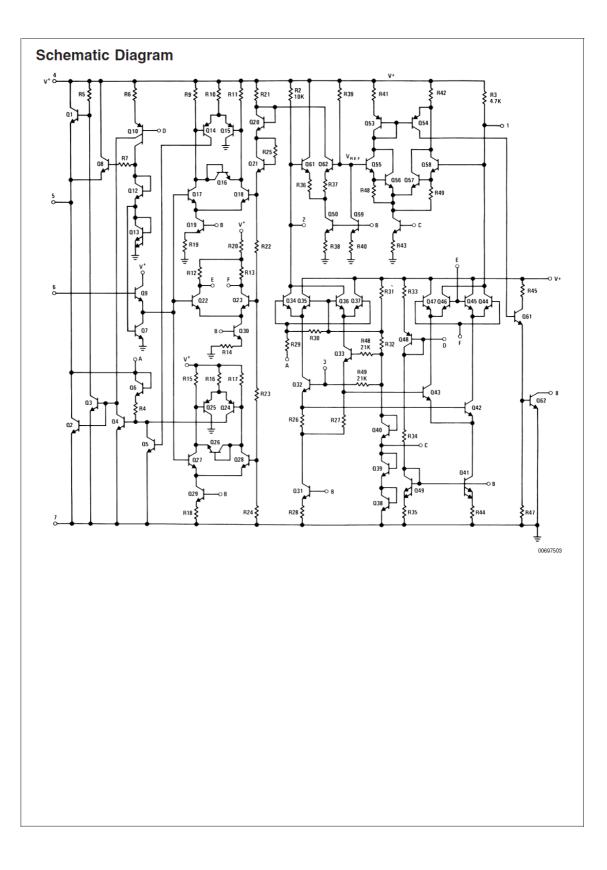

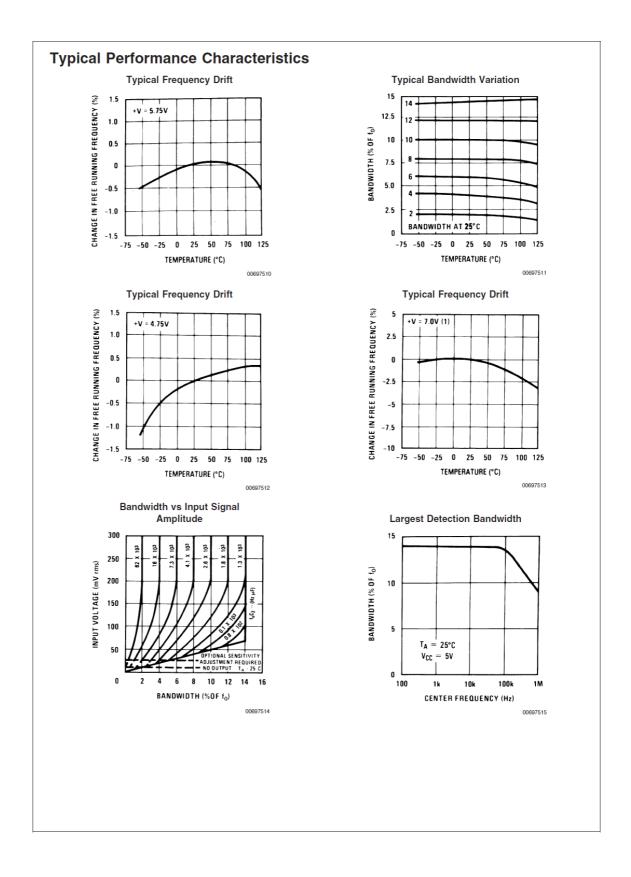

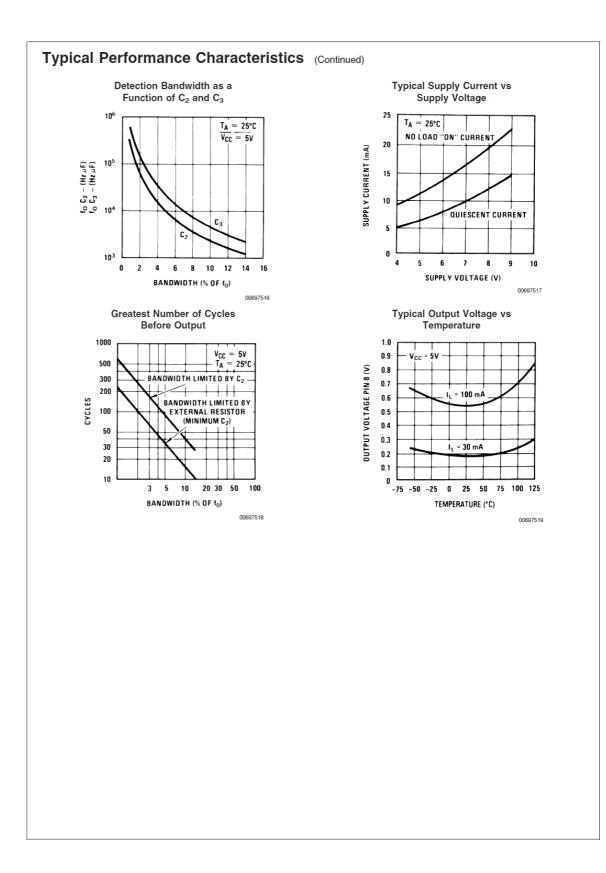

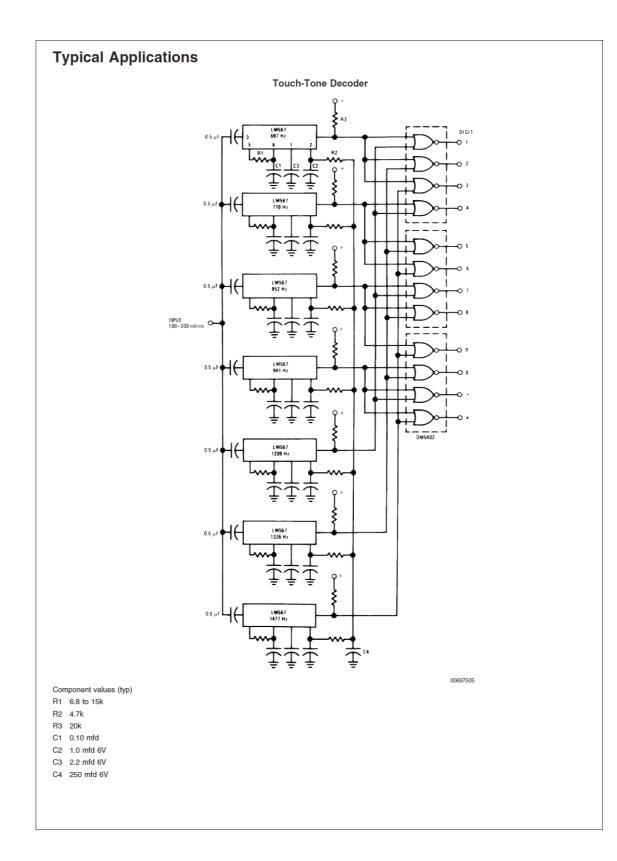

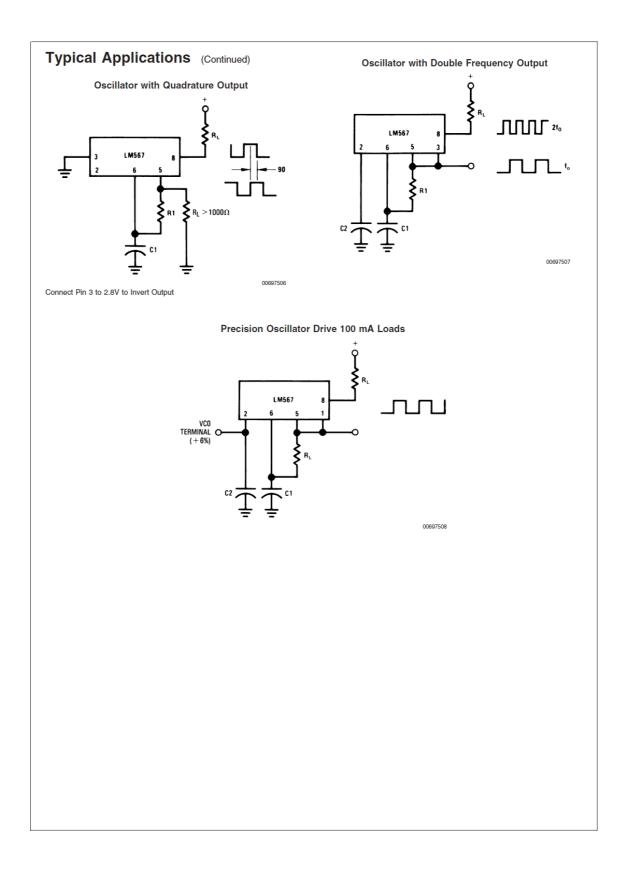

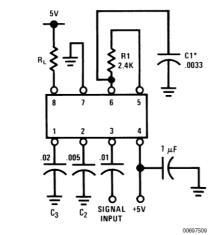

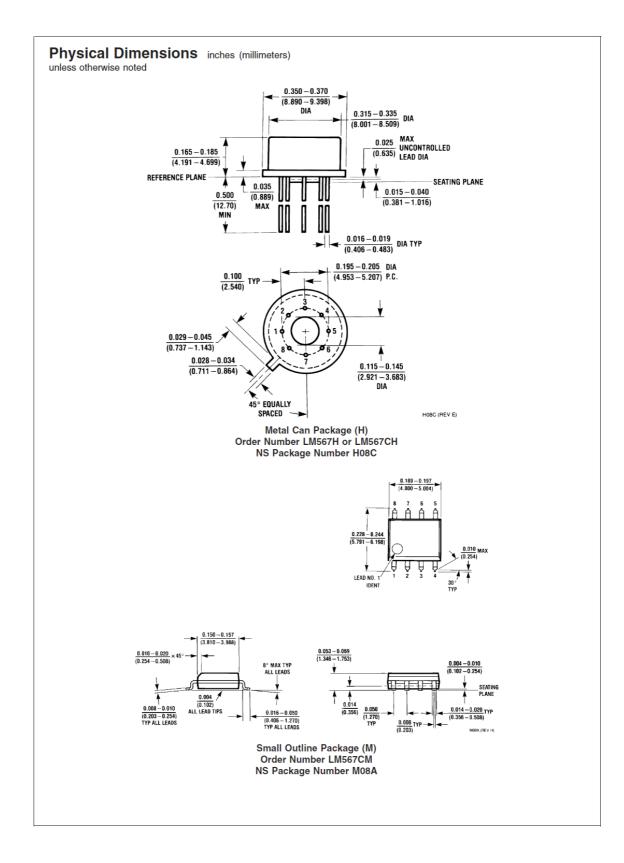

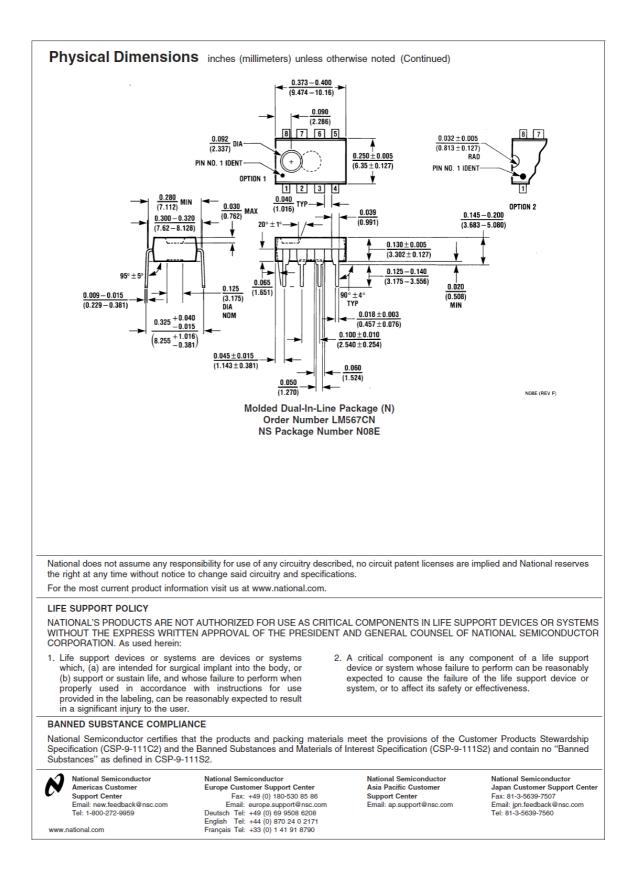

| Figure 5-3: LM567 Circuit                                                    | 51 |

| Figure 5-4: Bandwidth vs Input Signal Amplitude                              | 52 |

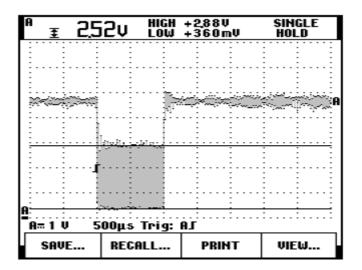

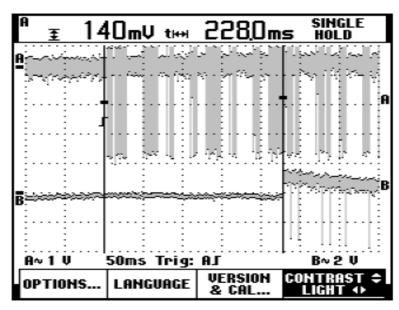

| Figure 5-5: LM567 Output                                                     | 53 |

| Figure 5-6: Mains Zero Crossing Detector                                     | 54 |

| Figure 5-7: Tx Amplifier and Surge Protection                                | 56 |

| Figure 5-8: Transmission Amplifier Output                                    | 57 |

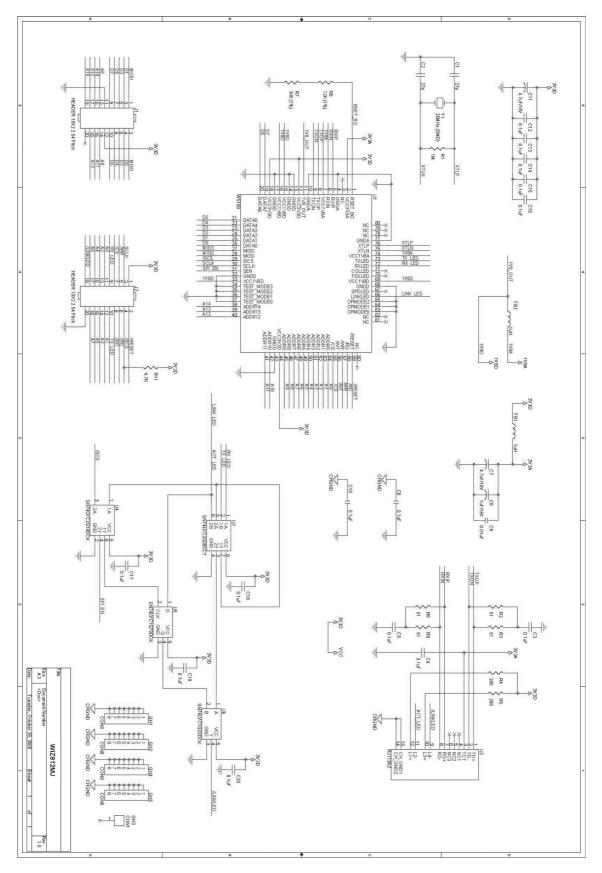

| Figure 5-9: MCU Schematic Diagram                                            | 61 |

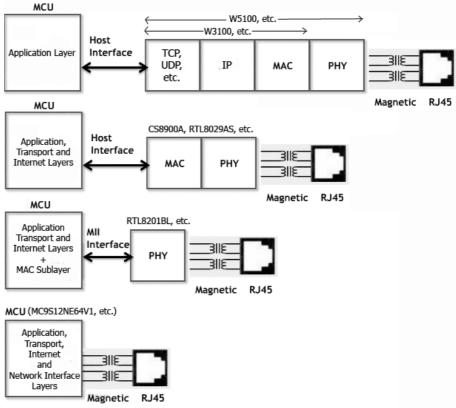

| Figure 5-10: Embedded Ethernet Solutions                                     | 62 |

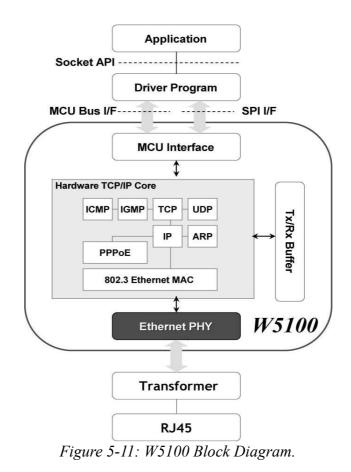

| Figure 5-11: W5100 Block Diagram                                             | 63 |

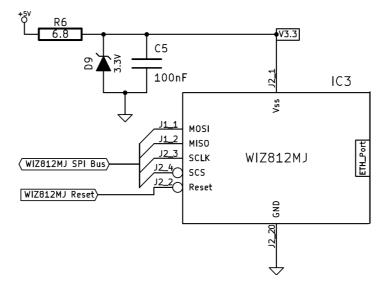

| Figure 5-12: WIZ812MJ Module Connectivity                                    | 64 |

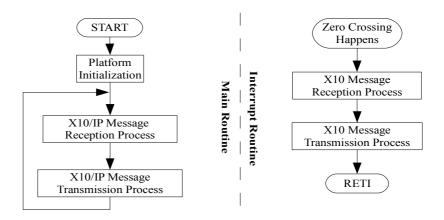

| Figure 6-1: Basic Microcontroller Operations                                 | 66 |

| Figure 6-2: X10/IP Message Reception Procedure                               | 68 |

| Figure 6-3: X10/IP Message Transmission Procedure                            | 69 |

| Figure 6-4: End-to-End Delay                                                 | 71 |

| Figure 6-5: X10 Message Reception Procedure                                  | 72 |

| Figure 6-6: X10 Message Transmission Procedure                               | 73 |

| Figure 6-7: FSM Diagram of the PLN Access Protocol                           | 74 |

| Figure 7-1: ActiveHome Pro <sup>TM</sup>                                     | 76 |

| Figure 7-2: Ostinato                                                         | 77 |

| Figure 7-3: Wireshark Analyser                                               | 78 |

| Figure 7-4: Connectivity Diagram for Timing Test                             | 80 |

| Figure 7-5: Transmission Amplifier Output.                                   | 80 |

| Figure 7-6: Connectivity Diagram for CSMA Algorithm Test                     | 81 |

| Figure 7-7: Connectivity Diagram for X10/IP Layer Operation Test             | 82 |

| Figure 7-8: Connectivity Diagram for Platform Integration to LAN             | 82 |

| Figure 7-9: Propagation Delay of X10 Signals between R and S Phase     | 83 |

|------------------------------------------------------------------------|----|

| Figure 7-10: Connectivity Diagram for Platform Integration to Internet | 83 |

# List of Tables

| Table 2-1: ISO/OSI Model Layers                                | 7  |

|----------------------------------------------------------------|----|

| Table 2-2: IPv4 Packet Structure                               | 11 |

| Table 2-3: UDP Header                                          | 17 |

| Table 3-1: The Modified OSI model according to CENELEC         | 19 |

| Table 3-2: Summary of maximum transmission levels (EN 50065-1) | 20 |

| Table 3-3: X10 Codes                                           | 23 |

| Table 3-4: Flags Field of INSTEON Message                      | 27 |

| Table 3-5: General Requirements for Physical Layer PL110       | 35 |

| Table 5-1: Hardware vs Software TCP/IP Stack                   | 62 |

| Table 6-1: Worldwide Ping Measurements                         | 70 |

# Acronyms

| ACK      | ACKnowledgment                                                  |

|----------|-----------------------------------------------------------------|

| ARP      | Address Resolution Protocol                                     |

| ARQ      | Automatic Repeat reQuest                                        |

| ATM      | Asynchronous Transfer Mode                                      |

| BPSK     | Binary Phase-Shift Keying                                       |

| BW       | BandWidth                                                       |

| CENELEC  | Comité Européen de Normalisation Électrotechnique               |

| CISPR    | Comité International Spécial des Perturbations Radioélectriques |

| CPU      | Central Processing Unit                                         |

| CSMA     | Carrier Sense Multiple Access                                   |

| CSMA/CA  | Carrier Sense Multiple Access with Collision Avoidance          |

| СТС      | Clear Timer on Compare match mode                               |

| DHCP     | Dynamic Host Configuration Protocol                             |

| DiffServ | Differentiated Services                                         |

| DoD      | United States Department of Defence                             |

| EoF      | End of Frame                                                    |

| EHSA     | European Home Systems Association                               |

| EHS      | European Home System protocol                                   |

| EIB      | European Installation Bus protocol                              |

| FDDI     | Fiber Distributed Data Interface                                |

| FSK      | Frequency Shift Keying                                          |

| FSM      | Finite-State Machine                                            |

| HAP     | Home Automation Protocol                                       |

|---------|----------------------------------------------------------------|

| HAoIP   | Home Automation protocols over IP                              |

| HSSI    | High-Speed Serial Interface                                    |

| HTTP    | HyperText Transfer Protocol                                    |

| HVAC    | Heating, Ventilating and Air Conditioning                      |

| IANA    | Internet Assigned Numbers Authority                            |

| ICMP    | Internet Control Message Protocol                              |

| IP      | Internet Protocol                                              |

| IPDV    | IP Packet Delay Variation                                      |

| IETF    | Internet Engineering Task Force                                |

| IPv4    | Internet Protocol version 4                                    |

| IPv6    | Internet Protocol version 6                                    |

| ISO/OSI | International Standard Organization's Open System Interconnect |

| LAN     | Local Area Network                                             |

| LLC     | Logical Link Control                                           |

| LPDU    | Link layer Protocol Data Unit                                  |

| MAC     | Media Access Control                                           |

| MCU     | Microcontroller Unit                                           |

| MII     | Medium Interdependent Interface                                |

| MIPS    | Million Instructions Per Second                                |

| MSK     | Minimum Shift Keying                                           |

| NACK    | Negative ACKnowledgment                                        |

| NetBIOS | Network Basic Input/Output System                              |

| NPDU    | Network layer Protocol Data Unit                               |

| NRZ     | Non-Return to Zero code                                        |

| OOK     | On/Off Keying modulation                                       |

|         |                                                                |

OS **Operating System** PC Personal Computer PDU Protocol Data Unit PLC Power Line Communication or Power Line Carrier PLN Power Line Network POP3 Post Office Protocol version 3 PPM **Pulse Position Modulation** RFC **Requests For Comments** SDU Service Data Unit SFSK Spread Frequency Shift Keying SIP Session Initiation Protocol SMB Server Message Block SPI Serial Peripheral Interface Transmission Control Protocol TCP TPDU Transport layer Protocol Data Unit TTL Transistor-Transistor Logic TtL Time to Live UDP User Datagram Protocol UPB Universal Powerline Bus WiFi Wireless Fidelity X10/IP X10 power line protocol over IP

# Chapter 1 Introduction

## 1.1 Overview

Personal computers, wireless networks, home gateways, Internet connections and device convergence have all opened up new possibilities and we can now perform computing in various locations and forms.

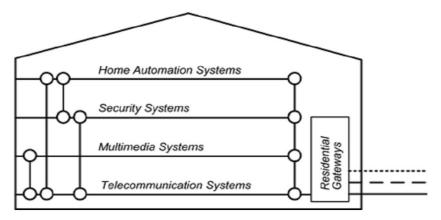

Smart homes are homes with integrated technological systems and appliances able to offer remotely and/or centralised controlled functionality and services (Figure 1-1).

Figure 1-1: A schematic overview of the smart home technical system infrastructure [1].

The technological infrastructure is based upon:

• <u>Home automation systems</u><sup>1</sup> including the control (on/off, open/close and regulation) of systems and functions for lighting, climate control (HVAC), blinds, doors, windows, locks, watering, white goods as well as the supply of water, gas and electricity.

• <u>Security systems</u> referring to alarms for intrusion (movement detectors, door and window detectors, glass break detectors), personal alarms (key fobs, wireless wristband transmitters and pendant transmitters), technical alarms (fire, smoke, gas, water leakage, and failure of electrical supply and telephone line) and remote video control for the protection of property, possessions and persons.

<sup>1</sup> Also called **domotics**.

• <u>Multimedia systems</u> including the capture, treatment and distribution of audio and video within, from and to the home, such as audio/video multi-room, home cinema and PC media servers.

• <u>Telecommunication systems</u> encompassing the distribution and sharing of files and data amongst machines and humans through cabled and wireless local area networks, IP telephony, telephony, broadband access, routers, etc.

• **<u>Residential gateways or home gateways</u>** having two main functions, one is to connect various home networks<sup>2</sup> together and/or to the Internet, while offering diagnostics, remote control facilities and user interfaces. The other is to be an enabling platform for new digital residential services [2, 3, 4, 5].

All the above mentioned systems, except the home automation systems, have been already migrated to Internet protocol suite. Thus, the convergence of home automation protocols (HAPs) to Internet protocol (IP) will simplify not only the residential gateway tasks, but also the integration of different systems.

## 1.2 Scope of the Thesis

Traditionally, homes have been wired for electricity, telephony and television services only. Therefore, as the installation of a dedicated wired bus for automation usage is expensive, there are two cost effective possibilities for home automation media. One is the power line and the other is some type of radio signal (wireless).

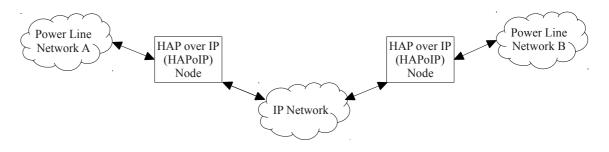

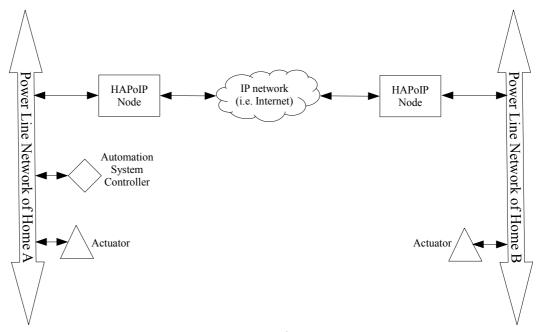

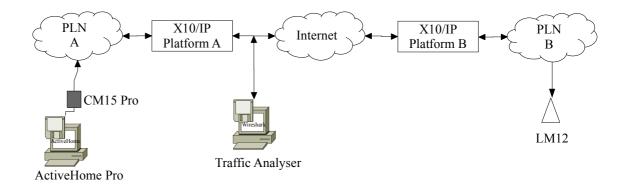

The scope of this thesis is to propose a mechanism for IP convergence of the open automation protocols of power line network that have not already migrated to IP. As (Figure 1-2) shows a special node is introduced as gateway between the two networks.

Figure 1-2: Power Line Automation over IP.

<sup>2</sup> Home networks can consist of many different kinds of networks and have incompatible physical interfaces, a gateway can bridge all these together.

## 1.3 State of the Art

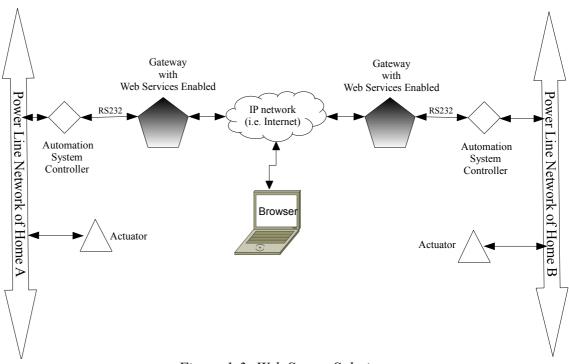

There are different approaches for home automation systems convergence to IP network. In most cases the home gateway or a computer in the home's local area network (LAN), which is connected to the controller of the home automation system via a serial interface, accommodates a web server and the HTTP protocol is used for the communication with the other IP nodes and/or user interfaces (Figure 1-3) [2, 6].

Figure 1-3: Web Server Solution.

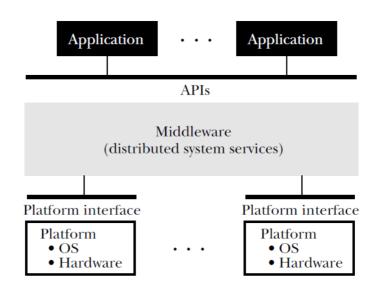

Another, more sophisticated, approach uses middleware that connects devices, network, software and services together in a smart environment. A home server with appropriate middleware could offer services such as timers, logging functions, preset modes with distributed user interfaces and group control (Figure 1-4) [3, 7, 8].

The disadvantages of the above mentioned approaches are the following:

- Not seamless solutions

- Complexity

- High cost

Figure 1-4: Example of Middleware Solution [9].

## 1.4 Contributions

This thesis will offer a wide range of contributions to the field of home automation systems as well as smart homes.

The main objective of this research was to design an application sub-layer in Internet protocol suite that gives the ability to open automation protocols of power line network to overcomes power line network barriers.

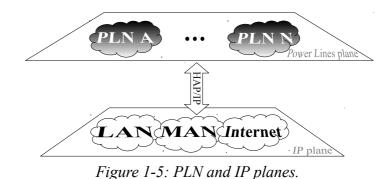

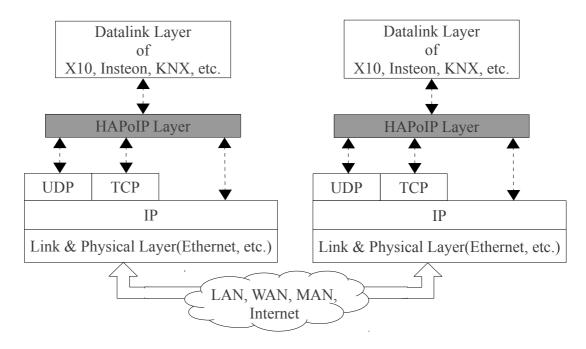

This achievement gives us the ability to connect transparently two or more separated and isolated power line networks via LAN and WAN with the help of HAPoIP protocol (Figure 1-5) and to have all the advantages of the services that have been developed in IP networks. Thus, widespread deployment of HAoIP solution presents an opportunity to expand building control communication beyond the local home power line bus providing:

- Remote configuration

- Remote operation

- Fast interface from LAN to power line protocol implementations and vice versa. The IP network acts as a fast backbone between HAPs nodes

- WAN connection between HAP networks

Therefore, we have the ability to control any distributed node (actuators, sensors and controllers) from any location around the world, and to have the control of the power line automation system in any place, in any time and in any way without the need of web servers and distributed controllers (Figure 1-3), (Figure 1-6).

Figure 1-6: Far-End Communication.

In addition, it will help in cost reduction of residential gateways as the Ethernet can be the only communication interface in use. Thus, as all power line communication  $(PLC)^3$  data will be over IP, the gateway can serve only its basic role, which is the interconnection of two different networks, namely a network outside the home (WAN) with a network inside the home (LAN) [10]. All the other gateway services can be

<sup>3</sup> Also known as Mains Communication(MC) or Power Line Networking(PLN).

optional and in dependence to gateway platform hardware and software resources. Furthermore, the interaction and cooperation between different systems in smart home environment will be simple and robust.

Also, a low cost and easy to develop platform for HAPoIP node is presented, where common hardware parts and the powerful and portable C programming language gives us maximum flexibility in design and operation.

### 1.5 Organization of the Thesis

This thesis is organized into eight chapters.

Chapter two provides an overview on Internet protocol suite. It will be an overview of the OSI and TCP/IP architecture and protocols stack.

Chapter three presents the open power line automation protocols. This chapter is a brief description of X10, INSTEON, UPB, EIB/KNX and LonTalk protocols.

Chapter four analyses the IP convergence of the above mentioned protocols. This chapter describes how the HAPoIP layer is implemented in the protocols that have not converged to IP yet.

Chapter five presents the hardware implementation of X10/IP platform. As the UPB and INSTEON protocols have not developed for 50Hz power lines yet, our implementation took place in X10 protocol.

Chapter six analyses the developed software.

Chapter seven describes the tests that took place and experimental results are presented.

Finally, chapter eight draws the conclusions of the thesis and discusses possible directions for future research.

# **Chapter 2** Internet Protocol Suite

## 2.1 Introduction

The Internet protocol suite<sup>4</sup> is the set of communications protocols that implement the protocol stack on which the Internet runs.

A protocol stack is a complete set of protocol layers that work together to provide networking capabilities. It is called a stack because it is typically designed as a hierarchy of layers, each supporting the one above it and using those below it.

The purpose of this chapter is to provide a brief description of the International Standard Organization's Open System Interconnect (ISO/OSI) model and Internet protocol suite focusing on the three most important protocols in it:

- I. Transmission control protocol (TCP)

- II. User Datagram Protocol (UDP)

- III. Internet protocol version 4

# 2.2 ISO/OSI Network Model

The ISO/OSI model is widely used for describing layered network communications and network protocols (Table 2-1).

| Layer<br>Number | Layer Name         | Data Unit | Protocols                     |  |

|-----------------|--------------------|-----------|-------------------------------|--|

| 7               | Application Layer  |           | HTTP, POP3, SIP, etc.         |  |

| 6               | Presentation Layer | Data      | SMB, etc.                     |  |

| 5               | Session Layer      |           | NetBIOS, etc.                 |  |

| 4               | Transport Layer    | Segment   | TCP, UDP, etc.                |  |

| 3               | Network Layer      | Packet    | IP, ICMP, ARP, etc.           |  |

| 2               | Data Link Layer    | Frame     | Ethernet, 802.11 (WiFi), etc. |  |

| 1               | Physical Layer     | Bit       | Wire, Radio Waves, etc.       |  |

Table 2-1: ISO/OSI Model Layers [11].

<sup>4</sup> Also called TCP/IP stack/model or DoD model.

The OSI model describes how data is moved between the independent layers and is divided into tasks that the seven layers perform. The purpose of a layer is to provide services to a layer above it and to receive services from the layer below it. Layers are transparent, so that the network layer of a device is able to communicate directly with the network layer of another device.

### 2.2.1 Physical Layer

The physical layer conveys the bit stream through the network at the electrical and mechanical level. The physical layer specifications also define characteristics, such as voltage levels, timing of impulses, physical data rates, maximum transmission distance, what modulation is used and physical connectors.

#### 2.2.2 Data Link Layer

The data link layer defines the format of the network data (checksum, addresses etc.) and divides data received from the physical layer into frames. It is also responsible for flow control and checking for errors during the transmission.

Ethernet data link layer contains two sublayers, the Media Access Control (MAC), and the Logical Link Control (LLC).

The IEEE 802.3 specification defines MAC addresses, which enable multiple devices to uniquely identify each other at the data link layer. The MAC sublayer manages protocol access to the physical network medium. It controls how a network device gains access to, and permission to transmit data.

LLC manages communications between devices over a single link of a network. It controls frame synchronization, flow control and error checking.

#### 2.2.3 Network Layer

The network layer is responsible for wrapping data received from the data link layer into packets and relaying them to the appropriate recipient. It also has to manage routing, i.e. choose the best path (shortest or the one with the smallest delay, for example) to the destination.

#### 2.2.4 Transport Layer

The transport layer receives data from the session layer, divides it into blocks and ensures these arrive at their destination in the correct order. It also adjusts the transmission speed so that the recipient is not overwhelmed with data.

#### 2.2.5 Session Layer

The session layer creates a session between two participants. It controls opening, maintaining and closing the session, and also resuming it after an interruption.

#### **2.2.6 Presentation Layer**

The presentation layer is not concerned with data transfer any more, its primary task is responsible for encryption/decryption and, as the name implies, the presentation of data (semantics, format, character sets etc.).

#### **2.2.7 Application Layer**

The uppermost layer is the application layer, which is the layer that is visible to the user. This provides different kinds of protocols for applications.

#### 2.3 TCP/IP Network Model

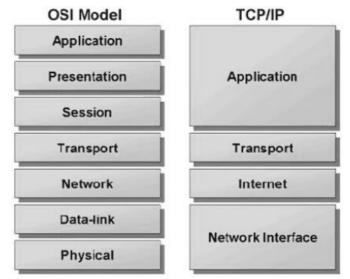

With the growth of the Internet, the TCP/IP network model has taken ground as the dominant representation for network design. OSI model is actually more robust, but TCP/IP is the primary model used in common practice today.

Figure 2-1 depicts difference between the two models. Instead of OSI's seven layers TCP/IP deployment has only five layers. The TCP/IP model layers perform the same duties as in OSI model. However, the Application Layer in TCP/IP groups the functions of OSI's Application, Presentation and Session Layers. Therefore any process above the transport layer is called an Application in the TCP/IP architecture. In TCP/IP stack socket and port are used to describe the path over which applications communicate. Most application level protocols are associated with one or more port number.

In addition, the Data Link Layer and Physical Layer are grouped together to become the Network Access layer. TCP/IP architecture makes use of existing Data Link and Physical Layer standards, rather than defining its own. Many RFCs describe how IP utilizes and interfaces with the existing data link protocols such as Ethernet, Token Ring, FDDI, HSSI, and ATM.

Figure 2-1: TCP/IP model versus OSI model.

In TCP/IP architecture, there are two Transport layer protocols the TCP and the UDP. Both protocols are useful for different applications.

The IP is the primary protocol in the TCP/IP Network/Internet Layer. All upper and lower layer communications must travel through IP as they are passed through the TCP/IP protocol stack. Moreover, there are many supporting protocols in the Internet Layer, such as ICMP, to facilitate and manage the routing process.

## 2.3.1 IP

As the previous section has already mentioned, IP is the primary protocol in the Internet Layer of the Internet Protocol Suite and has the task of delivering datagrams from the source host to the destination host solely based on their addresses. For this purpose, IP defines addressing methods and structures for datagram encapsulation (Figure 2-2).

| IP Header                              | Upper Layer Data |  |  |  |

|----------------------------------------|------------------|--|--|--|

| Figure 2-2: IP Datagram Encapsulation. |                  |  |  |  |

The first major version of IP, now referred to as Internet Protocol Version 4 (IPv4) is the dominant protocol of the Internet, although the successor, Internet Protocol Version 6 (IPv6) is in active, growing deployment worldwide. IPv4 is defined in RFC 791 (September 1981), which has been republished as STD 5. However, RFC 791 contained some vagaries that were clarified in RFC 1122. As such, IP implementations need to incorporate both RFC 791 and RFC 1122 in order to work reliably and consistently with other implementations [12].

IPv4 uses 32-bit (four-byte) addresses, which limits the address space to 4,294,967,296 possible unique addresses. However, some are reserved for special purposes such as private networks or multicast addresses. This reduces the number of addresses that can potentially be allocated for routing on the public Internet<sup>5</sup>. As addresses are being incrementally delegated to end users, an IPv4 address shortage has been developed.

The IPv4 packet header (Table 2-2) consists of 14 fields, of which the 14<sup>th</sup> field is optional (Options field).

| Bit Offset                                         | 0 - 3 <sup>th</sup> bit       | 4 <sup>th</sup> - 7 <sup>th</sup> bit | 8 <sup>th</sup> - 13 <sup>th</sup> bit   | 14 <sup>th</sup> - 15 <sup>th</sup> bit | 16 <sup>th</sup> - 18 <sup>th</sup> bit | 19 <sup>th</sup> - 31 <sup>th</sup> bit |

|----------------------------------------------------|-------------------------------|---------------------------------------|------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| 0 bit                                              | Version                       | Internet<br>Header<br>Length          | Differentiated<br>Services<br>Code Point | Explicit<br>Congestion<br>Notification  | Total Length                            |                                         |

| 32 <sup>th</sup> bit                               |                               | Identif                               | Flags                                    | Fragment<br>Offset                      |                                         |                                         |

| 64 <sup>th</sup> bit                               | Time to Live Protocol         |                                       |                                          | Header C                                | Checksum                                |                                         |

| 96 <sup>th</sup> bit                               | Source IP Address             |                                       |                                          |                                         |                                         |                                         |

| 128 <sup>th</sup> bit                              | Destination IP Address        |                                       |                                          |                                         |                                         |                                         |

| 160 <sup>th</sup> bit                              | Options(if Header Length > 5) |                                       |                                          |                                         |                                         |                                         |

| 160 <sup>th</sup><br>or<br>192 <sup>th</sup> + bit | Data                          |                                       |                                          |                                         |                                         |                                         |

Table 2-2: IPv4 Packet Structure [13].

A brief description of IPv4 header's fields are the followings:

- 1. Version: For IPv4, this has a value of 4 (hence the name IPv4)

- 2. Internet Header Length: Since an IPv4 header may contain a variable number of options, this field specifies the size of the header

<sup>5</sup> Internet Assigned Numbers Authority (IANA) controls IP address allocation in Internet (public IPs).

- **3. Differentiated Services Code Point:** Originally defined as the Type of Service field, this field is now defined by RFC 2474 for Differentiated Services (DiffServ)

- 4. Explicit Congestion Notification: Defined in RFC 3168 and allows end-toend notification of network congestion without dropping packets. It is an optional feature that is only used when both endpoints support it and are willing to use it

- 5. Total Length: This 16-bit field defines the entire datagram size, including header and data, in bytes. Sometimes subnetworks impose restrictions on the size, in which case datagrams must be fragmented

- **6. Identification:** This field is an identification field and is primarily used for uniquely identifying fragments of an original IP datagram

- 7. Flags: A three bit field follows and is used to control or identify fragments

- 8. Fragment Offset: The fragment offset field, measured in units of eight byte blocks, is 13 bits long and specifies the offset of a particular fragment relative to the beginning of the original unfragmented IP datagram

- **9.** Time to Live (TtL): This field helps prevent datagrams from persisting (e.g. going in circles) on the Internet. This field limits a datagram's lifetime. Each router that a datagram crosses decrements the TtL field by one. When the TtL field hits zero, the packet is no longer forwarded and is discarded

- 10. Protocol: This field defines the protocol used in the data portion of the IP datagram. IANA maintains a list of IP protocol numbers, which was originally defined in RFC 790

- **11. Header Checksum:** It is used for error-checking of the header. At each hop, the checksum of the header must be compared to the value of this field. If a header checksum is found to be mismatched, then the packet is discarded. The method used to compute the checksum is defined within RFC 1071

- **12. Source address:** An IPv4 address is a group of four octets for a total of 32 bits. This address is the address of the sender of the packet

- **13. Destination address:** Identical to the source address field but indicates the receiver of the packet

- **14. Options:** Additional header fields may follow the destination address field, but these are not often used

IPv6 is a version of the Internet Protocol that is designed to succeed Internet protocol IPv4. It was developed by Internet Engineering Task Force (IETF), and is described in Internet standard document RFC 2460, published in December 1998.

The main driving force for the redesign of Internet protocol was the foreseeable IPv4 address exhaustion. Also, version 6 adapts in IP protocol some important features, such as QoS and network security and simplifies aspects of address assignment and network renumbering when changing Internet connectivity providers.

### 2.3.2 TCP

Transmission Control Protocol is defined in RFC 793, which has been republished as STD 7. However, RFC 793 contained some vagaries which were clarified in RFC 1122. In addition, RFC 2001 introduced a variety of congestion related elements to TCP, which have been included into the standard specification, although this RFC was superseded by RFC 2581. Finally, extensions are given in RFC 1323. As such, TCP implementations need to incorporate RFC 793, RFC 1122, RFC 1323 and RFC 2581 in order to work reliably and consistently with other implementations [12, 14].

TCP is a connection-oriented protocol that is responsible for reliable communication between two end processes. The unit of data transferred is called a stream, which is simply a sequence of bytes.

Among the services TCP provides are stream data transfer, reliability, efficient flow control, full-duplex operation, and multiplexing.

With stream data transfer, TCP delivers an unstructured stream of bytes identified by sequence numbers. This service benefits applications because the application does not have to chop data into blocks before handing it off to TCP. Also, TCP can group bytes into segments and pass them to IP for delivery.

By providing connection-oriented end-to-end reliable packet delivery, TCP offers

reliability. It does so by sequencing bytes with a forwarding acknowledgment number that indicates to the destination the next byte the source expects to receive. Bytes not acknowledged within a specified time period are retransmitted. The reliability mechanism of TCP allows devices to deal with lost, delayed, duplicate, or misread packets. A time-out mechanism allows devices to detect lost packets and request retransmission.

TCP uses a sliding window flow control mechanism. In each TCP segment, the receiver specifies in the receive window field the amount of additional received data that is willing to buffer for the connection. The sending host can send only up to that amount of data before it must wait for an acknowledgment and window update from the receiving host [14].

Since many network applications may be running on the same machine, computers need something to make sure the correct software application on the destination computer gets the data packets from the source machine, and some way to make sure replies get routed to the correct application on the source computer. This is accomplished through the use of the TCP "port numbers". The combination of IP address of a network node and its port number is known as a "socket" or an "endpoint". TCP establishes connections or virtual circuits between two "endpoints" for multiplexing and reliable communications.

The port numbers are divided into three ranges<sup>6</sup>:

- I. The Well Known Ports are those in the range 0 1023.

- II. The *Registered Ports* are those in the range 1024 49151.

- III. The Private Ports are those in the range 49152 65535.

The TCP header (Figure 2-3) consists of 16 fields. The  $16^{\text{th}}$  field is optional (Option + Padding).

A brief description of TCP header's fields are the followings:

**1. Source Port:** Identifies the port number in use by the application that is sending the data

<sup>6</sup> Both Well Known and Registered Ports are assigned by the IANA for major protocols.

2. Destination Port: Identifies the 16 bits target port number of the application that is to receive this data

| 1 <sup>st</sup> - 16 <sup>th</sup> bit |               |       |     |             |             |             |       | 17 <sup>th</sup> - 32 <sup>th</sup> bit |  |  |

|----------------------------------------|---------------|-------|-----|-------------|-------------|-------------|-------|-----------------------------------------|--|--|

| Source port                            |               |       |     |             |             |             |       | Destination port                        |  |  |

| Sequence number                        |               |       |     |             |             |             |       |                                         |  |  |

| Acknowledgement number                 |               |       |     |             |             |             |       |                                         |  |  |

| Offset                                 | Re-<br>served | U R G | ACK | P<br>S<br>H | R<br>S<br>T | S<br>Y<br>N | F I N | Window                                  |  |  |

| Checksum                               |               |       |     |             |             |             |       | Urgent pointer                          |  |  |

| Option + Padding                       |               |       |     |             |             |             |       |                                         |  |  |

| Data                                   |               |       |     |             |             |             |       |                                         |  |  |

Figure 2-3: TCP Header [15].

- **3. Sequence number:** Each byte of data sent across a virtual circuit is assigned a somewhat unique number. The Sequence number field is used to identify the number associated with the first byte of data in this segment

- **4.** Acknowledgement number: Identifies the next byte of data that a recipient is expecting to receive

- 5. Offset: Indicates where the data begins

- 6. **Reserved:** This field is for future use

- **7. Control Flags:** Carry a variety of control information. The control bits may be:

- I. URG: Urgent pointer field in use

- II. ACK: Indicates whether frame contains acknowledgement

- III. *PSH:* Data has been "pushed". It should be delivered to application right away

- IV. RST: Indicates that the connection should be reset

- V. SYN: Synchronize sequence numbers

- VI. FIN: Used to release a connection

- **8. Window:** Specifies the size of the sender's receive window, that is, the buffer space available in octets for incoming data

- **9.** Checksum: Used to store a checksum of the entire TCP segment for error detection

- **10. Urgent Pointer:** Communicates the current value of the urgent pointer as a positive offset from the sequence number in this segment. It points to the sequence number of the octet following the urgent data

- 11. Option + Padding: Provides a way to add extra facilities not covered by the regular header. The most important option is the one that allows each host to specify the maximum TCP payload it is willing to accept. A TCP segment's header length must be a multiple of 32 bits. If any options have been introduced to the header, the header must be padded

### 2.3.3 UDP

UDP is defined in RFC 768, which has been republished as STD 6. However, RFC 768 contained some vagaries that were clarified in RFC 1122. As such, UDP implementations need to incorporate both RFC 768 and RFC 1122 in order to work reliably and consistently with other implementations.

UDP is a connectionless, stateless transport layer protocol in the which provides a simple and unreliable message service for transaction oriented services. UDP is basically an interface between IP and upper layer processes. UDP protocol ports, which are common with TCP ports, distinguish multiple applications running on a single device from one another.

Unlike TCP, UDP adds no reliability, flow control, or error recovery functions to IP. Because of UDP's simplicity, UDP headers contain fewer bytes and consume less network overhead than TCP (Table 2-3). It is often used by applications that need multicast or broadcast delivery, services not offered by TCP.

| 1 <sup>st</sup> - 16 <sup>th</sup> bit | 17 <sup>th</sup> - 32 <sup>th</sup> bit |  |  |  |  |  |

|----------------------------------------|-----------------------------------------|--|--|--|--|--|

| Source Port                            | Destination Ports                       |  |  |  |  |  |

| Length                                 | Checksum                                |  |  |  |  |  |

|                                        |                                         |  |  |  |  |  |

| Data                                   |                                         |  |  |  |  |  |

|                                        |                                         |  |  |  |  |  |

|                                        | Source Port<br>Length                   |  |  |  |  |  |

Table 2-3: UDP Header [16].

A brief description of UDP header's fields are the followings:

- 1. Source Port: It is an optional field. When used, it indicates the port of the sending process and may be assumed to be the port to which a reply should be addressed in the absence of any other information.

- **2. Destination Port:** It has a meaning within the context of a particular Internet destination address.

- **3. Length:** Specifies the size of the total UDP message, including both the header and data segments.

- **4.** Checksum: Used to store a checksum of the entire UDP message for error detection.

# **Chapter 3 Description of Open Power Line HAPs**

## 3.1 Introduction

This chapter presents the open HAPs that use the common power lines of a building as communication medium. We use the term open as in market there are a lot of product using proprietary power line communication techniques, which are out of the scope of this research ("IN ONE" by Legrand S.A., etc).

The advantages of using the already existed electrical wiring of a house is first of all the compatibility with legacy home infrastructure and the availability of transmission signal in any electrical outlet and switch throughout the home.

However, because power line cables are not designed for communication, they provide some challenges for home networking. Frequency selectivity and time variation of the channel frequency, high levels of noise and country-by-country regulatory issues are some of the main considerations [17, 18].

### 3.2 ISO/OSI Network Model in Smart Homes

A good way of describing where protocols lay in home automation systems is to use OSI model.

In addition, Comité Européen de Normalisation Électrotechnique (CENELEC)<sup>7</sup> has introduced two additional layers at the bottom of standard OSI model for the smart home implementation (Table 3-1). These new layers are "Media" and "Pathways and Spaces".

Pathways is a facility for the installation and placement of cables from the outlets and switches to the main distribution box/es. A pathway can be composed of several components including wall tube, cable tray, conduit, underfloor, access floor, noncontinuous fasteners, and perimeter systems, according to specific country regulations.

Space is an area used for housing the installation and termination of equipment, interconnections and cable, e.g., equipment room, closets, distributors and maintenance boxes/handholes.

<sup>7</sup> CENELEC is responsible for European Standardization in the area of electrical engineering.

| Layer<br>Number | Layer Name          | Normative References<br>for PLC                    |  |  |

|-----------------|---------------------|----------------------------------------------------|--|--|

| 7               | Application Layer   | N/A                                                |  |  |

| 6               | Presentation Layer  |                                                    |  |  |

| 5               | Session Layer       |                                                    |  |  |

| 4               | Transport Layer     |                                                    |  |  |

| 3               | Network Layer       | EN 50090-4-2, etc.                                 |  |  |

| 2               | Link Layer          |                                                    |  |  |

| 1               | Physical Layer      | EN 50065-1,<br>EN 50065-2-1,<br>EN 50090-5-1, etc. |  |  |

| 0               | Media               |                                                    |  |  |

| -1              | Pathways and spaces | CWA 50487,<br>EN 50173-4,<br>ISO/IEC 15018         |  |  |

Table 3-1: The Modified OSI model according to CENELEC [19].

During the building or refurbishing phase of a home the installation of a cabling system causes such little trouble and cost that such a system always shall be installed. In case the use of cables is excluded for a reasonable number of years, at least, the pathways and spaces that would support such a cabling system shall be installed.

The Media layer accommodates a wide range of materials that can be used for signal transmission, e.g., copper cables and fibers. In this research we will examine the HAPs that use the power lines in Media layer.

## 3.3 European Regulation Basics in PLCs

The European PLC regulation norm is called EN 50065-1:"Signalling on low-voltage electrical installations in the frequency range 3 kHz to 148.5 kHz". It defines the allowed frequency ranges of power line communication, maximum signal amplitudes, as well as the limits of the interference to the surrounding frequency bands.

The defined sub-bands are the followings:

- I. 3 kHz 95 kHz: Restricted to electricity suppliers and their licensees

- II. 95 kHz 125 kHz<sup>8</sup>: Available for consumers with no restriction

<sup>8</sup> Equipment for use in this frequency band is designated as either Class 122 or as Class 134 equipment.

III. *125 kHz - 140 kHz*: Available for consumers only with carrier-sense multiple access (CSMA) protocol

IV. 140 kHz - 148.5 kHz: Available for consumers with no restriction

Maximum output levels (Vpeak) for all sub-bands shown in Table 3-2. Measurements have to be done according to the CISPR 16-1 publication.

|                                                                                      |                         | Three-phase devices                           |                                           |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------|-------------------------------------------|--|--|--|

| Frequency<br>sub-band                                                                | Single-phase<br>devices | Simultaneous<br>transmission<br>on all phases | Transmission<br>on a single<br>phase only |  |  |  |

| 3 kHz to 9 kHz                                                                       | 134                     | 128                                           | 134                                       |  |  |  |

| 9 kHz to 95 kHz<br>(Narrow-band)                                                     | 134 to 120*             | 128 to 114*                                   | 134 to 120*                               |  |  |  |

| 9 kHz to 95 kHz<br>(Wide-band)                                                       | 134                     | 128                                           | 134                                       |  |  |  |

| 95 kHz to 148,5 kHz<br>(Class 122)                                                   | 122                     | 116                                           | 122                                       |  |  |  |

| 95 kHz to 148,5 kHz<br>(Class 134)                                                   | 134                     | 128                                           | 134                                       |  |  |  |

| All limit values in dB (μV)<br>* Decreasing linearly with the logarithm of frequency |                         |                                               |                                           |  |  |  |

Table 3-2: Summary of maximum transmission levels (EN 50065-1).

The EN 50065-1 norm defines neither a data rate nor a modulation scheme, but because of the quite narrow frequency range of each band, only relatively low data rates are possible.

### 3.4 Description of X10 Power Line Protocol

X10 is an international industry standard that is used for communicating electronic appliance via electrical power network. A radio based transport is also defined.

X10 was developed in 1975 by Pico Electronics (PICO) of Glenrothes, Scotland, UK in order to allow remote control of home devices and appliances. The PICO engineers subsequently relocated to Hicksville, New York and continued with their efforts. It was their 10th project, hence the term X10, which has been used to describe the signalling technique. The X10 team subsequently named their new home automation company X10 Ltd., and relocated to Closter, New Jersey. Later X10 Wireless Technology Inc., a branch

of the original company was established whose purpose was to broaden the market by wireless devices.

Today, several companies in addition to X10 Ltd produce X10 compatible devices for home automation. They are SmartLinc, Powerline Carrier Systems (PCS), Leviton, Monterey, Marmitek and others.

### 3.4.1 Media Layer

The X10 protocol uses mainly electrical power lines as transmission media but in order to allow the operation of wireless keypads, remote switches, and the like, a radio wave media is also defined.

### 3.4.2 Physical Layer

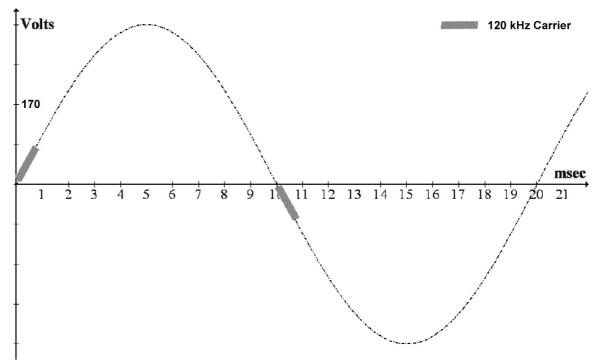

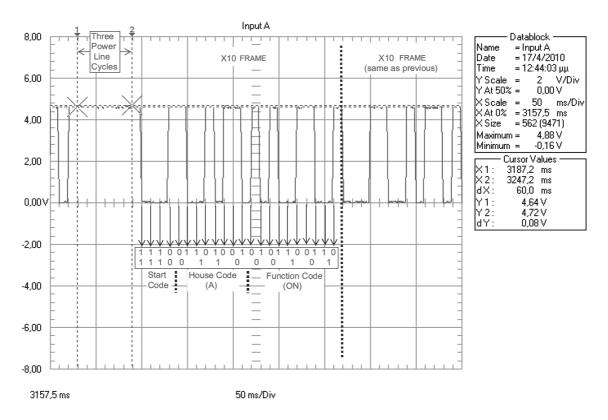

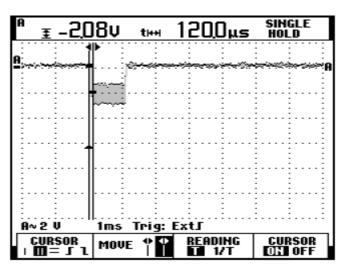

X10 transmissions are synchronised to the zero crossing point of the AC power line (Figure 3-1).

Figure 3-1: X10 Transmission (bits: 110).

X10 receivers detect the presence of 120 kHz signal in X10 information window just after each zero crossing point of the power line voltage. The X10 receiving window begins approximately 250 µs and ends 900 µs after a zero crossing. In this window 48 or

more cycles of 120 kHz carrier are accepted as high data logic and fewer than 48 as a low data logic<sup>9</sup> [20]. Since two bits of X10 frame is transmitted per 50 Hz power line period, the protocol has a raw speed of 100 bps.

For most X10 receivers, the 120 kHz signal must have a minimum amplitude of 50 millivolts peak to be detected reliably.

X10 wireless devices operate at a frequency of 433 MHz in Europe and a different frequency in the rest of the world. These wireless devices send X10 frames in the same way as in power lines (OOK modulation). An X10 controller then provides a bridge between radio frequency carrier and power line media.

#### 3.4.3 Data Link Layer

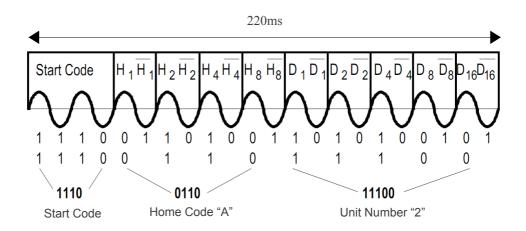

In order to provide a predictable starting point, every X10 frame always begins with the alignment/start code "1110" (Figure 3-2). The start code nibble is unique and can be found only at the start of the X10 frame. Immediately after the start code, a house code (A–P) is sent and after the house code, comes a function code. Except for start code nibble the bits of both house and function code should be transmitted in true and complement form on alternate half cycles of the power line.

Figure 3-2: X10 Standard Frame [20].

Function codes may specify a unit number code (1-16) or an actual command code, the selection between the two modes being determined by the last bit, where zero means unit number and one means command (Table 3-3).

<sup>9</sup> On/Off Keying modulation(OOK).

| House<br>Code | H8 | H4 | H2 | H1 | Unit<br>Number | D8 | D4 | D2 | D1 | D16 | Command Code    | D8 | D4 | D2 | D1 | D16 |

|---------------|----|----|----|----|----------------|----|----|----|----|-----|-----------------|----|----|----|----|-----|

| A             | 0  | 1  | 1  | 0  | 1              | 0  | 1  | 1  | 0  |     | ON              | 0  | 0  | 1  | 0  |     |

| В             | 1  | 1  | 1  | 0  | 2              | 1  | 1  | 1  | 0  |     | OFF             | 0  | 0  | 1  | 1  |     |

| C             | 0  | 0  | 1  | 0  | 3              | 0  | 0  | 1  | 0  |     | DIM             | 0  | 1  | 0  | 0  |     |

| D             | 1  | 0  | 1  | 0  | 4              | 1  | 0  | 1  | 0  |     | BRIGHT          | 0  | 1  | 0  | 1  |     |

| E             | 0  | 0  | 0  | 1  | 5              | 0  | 0  | 0  | 1  |     | ALL LIGHTS ON   | 0  | 0  | 0  | 1  |     |

| F             | 1  | 0  | 0  | 1  | 6              | 1  | 0  | 0  | 1  |     | ALL UNITS OFF   | 0  | 0  | 0  | 0  |     |

| G             | 0  | 1  | 0  | 1  | 7              | 0  | 1  | 0  | 1  |     | ALL LIGHTS OFF  | 0  | 1  | 1  | 0  |     |

| Н             | 1  | 1  | 0  | 1  | 8              | 1  | 1  | 0  | 1  | 0   | EXTENDED CODE 1 | 0  | 1  | 1  | 1  | 1   |

| Ι             | 0  | 1  | 1  | 1  | 9              | 0  | 1  | 1  | 1  | 0   | HAIL REQUEST    | 1  | 0  | 0  | 0  |     |

| J             | 1  | 1  | 1  | 1  | 10             | 1  | 1  | 1  | 1  |     | HAIL ACK.       | 1  | 0  | 0  | 1  |     |

| K             | 0  | 0  | 1  | 1  | 11             | 0  | 0  | 1  | 1  |     | EXTENDED CODE 3 | 1  | 0  | 1  | 0  |     |

| L             | 1  | 0  | 1  | 1  | 12             | 1  | 0  | 1  | 1  |     | UNUSED          | 1  | 0  | 1  | 1  |     |

| M             | 0  | 0  | 0  | 0  | 13             | 0  | 0  | 0  | 0  |     | EXTENDED CODE 2 | 1  | 1  | 0  | 0  |     |

| N             | 1  | 0  | 0  | 0  | 14             | 1  | 0  | 0  | 0  |     | STATUS "ON"     | 1  | 1  | 0  | 1  |     |

| 0             | 0  | 1  | 0  | 0  | 15             | 0  | 1  | 0  | 0  |     | STATUS "OFF"    | 1  | 1  | 1  | 0  |     |

| Р             | 1  | 1  | 0  | 0  | 16             | 1  | 1  | 0  | 0  |     | STATUS REQUEST  | 1  | 1  | 1  | 1  |     |

Table 3-3: X10 Codes [20].

Every X10 frame is sent twice without a gap. After transmission of the group of twin frames, must be at least a tree power line cycles silence before the next frame transmission (Figure 3-3). The one exception to above rules is the frames that carry "BRIGHT" and DIM" command codes. These should be transmitted continuously (singles) with no gaps between frames.

Figure 3-3: X10 Standard Message and Standard Frame Transmission [20].

X10 standard messages do not support more advanced control over the dimming speed, direct dim level setting and group control (scene settings). This is done via extended message set. However support for all extended messages is not mandatory, and a lot of modules implement only the standard message set.

In extended X10 frames, the extended message code is followed by extra bits which can represent sensors value, extra commands, etc. There should be no gaps between the extended message code and the actual data, and no gaps between data bytes (Figure 3-4). 29 Mains Cycles

| 4 bits        | 5 bits           | 4 bits       | 8 bits    | 8 bits            |

|---------------|------------------|--------------|-----------|-------------------|

| House<br>Code | Extended<br>Code | Unit<br>Code | Data Byte | Type &<br>Command |

Figure 3-4: Extended Message Format [20].

As the power lines are the media for both transmission and reception, it is required that transmitters avoid message collisions mechanism where possible, and also that, when a collision does occur, it can be detected and the conflict resolved. In order to do this, the Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA) protocol. should be adopted.

When a transmitter has a message it wishes to transmit, it must wait for access to the power line for either 8, 9, or 10 half mains cycles during which the power line must have been continuously clear of 120 kHz carrier<sup>10</sup>. If a carrier is detected, it must restart its access timing and wait for another 8, 9, or 10 cycles.

After power line access has been achieved, the transmitter must check the line during the transmission of '0' bits (no carrier) to see that no other transmitter is transmitting. If a collision occurs, the transmitter must abort its transmission immediately and again go though the power line access procedure.

The choice of 8, 9, or 10 half cycles is chosen randomly for each power line access attempt.

#### 3.5 Description of INSTEON

INSTEON is a cost effective, robust and reliable dual media home automation protocol. It is enabling peer-to-peer technology, meaning that any device can transmit, receive, or repeat other messages, without requiring a master controller or complex routing software.

INSTEON was designed in order to overcome the poor performance of X10 protocol keeping the cost of implementation as low as possible. INSTEON and X10 protocol can coexist with each other on power lines without mutual interference.

<sup>10</sup> All messages are assumed to have equal priority.

SmartLabs Technology, a division of SmartLabs, Inc. developed INSTEON since 2001. SmartLabs is organized into three companies: Smarthome Direct, which includes Smarthome.com, the SmartLabs Design, creators of home control products and the SmartLabs Technology, the pioneering architects of INSTEON.

Despite the ease of implementation, INSTEON has not been developed for 50 Hz power lines yet<sup>11</sup>.

## 3.5.1 Media Layer

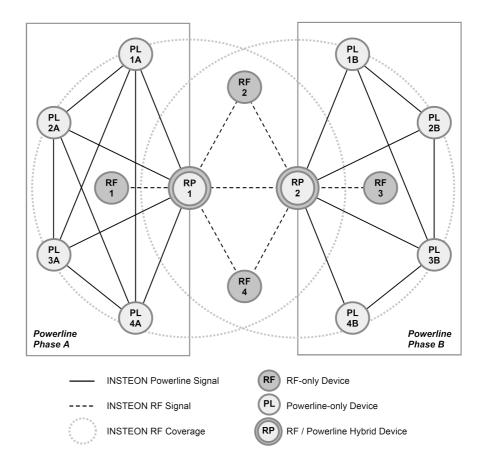

INSTEON's nodes communicates with each other using the INSTEON protocol over power lines or radio waves.

The Figure 3-5 shows INSTEON devices that communicate by power line only (PL), radio waves only (RF), and both (RP).

Figure 3-5: INSTEON Network Implementation Example [21].

<sup>11</sup> http://www.insteon.net/faq-home.html#12

## 3.5.2 Physical Layer

There is no specification for physical layer in both power line and radio waves for Europe.

In USA, INSTEON uses a Frequency-Shift Keying (FSK) modulated carrier in 900 Mhz band for wireless operation, which is permitted for unlicensed operation.

Also, for power line communication INSTEON uses a 131.65 kHz carrier signal with 4.64 Vp-p amplitude in 5 ohm load. The carrier is modulated with alternating Binary Phase-Shift Keying (BPSK) bit modulation and the bit-stream has encoded with Non-Return to Zero code (NRZ).

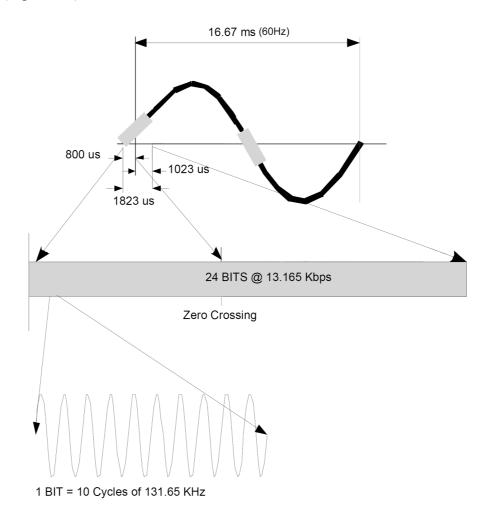

INSTEON frames are transmitted during the zero crossing quiet time and begin 800 microseconds before a zero crossing and last until 1023 microseconds after the zero crossing (Figure 3-6).

Figure 3-6: INSTEON frames over 60Hz PLN [21].

# 3.5.3 Data Link Layer

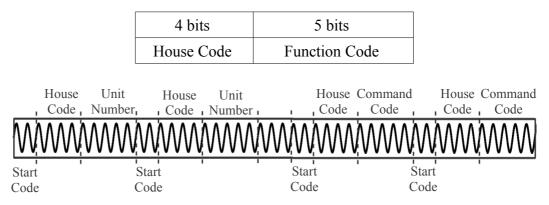

As X10 protocol, INSTEON has two types of messages, 10-byte standard length message and 24-byte extended length message (Figure 3-7).

| Π                 | <b>INSTEON Standard Message</b> |        |               |        |  |  |  |  |  |  |  |  |  |  |

|-------------------|---------------------------------|--------|---------------|--------|--|--|--|--|--|--|--|--|--|--|

| 3 Bytes           | 3 Bytes                         | 1 Byte | 2Bytes        | 1 Byte |  |  |  |  |  |  |  |  |  |  |

| Source<br>Address | Destination<br>Address          | Flags  | Commands 1, 2 | CRC    |  |  |  |  |  |  |  |  |  |  |

|                   | INSTEON Extended Message |        |               |           |        |  |  |  |  |  |  |  |  |  |

|-------------------|--------------------------|--------|---------------|-----------|--------|--|--|--|--|--|--|--|--|--|

| 3 Bytes           | 3 Bytes                  | 1 Byte | 2 Bytes       | 14 Bytes  | 1 Byte |  |  |  |  |  |  |  |  |  |

| Source<br>Address | Destination<br>Address   | Flags  | Commands 1, 2 | User Data | CRC    |  |  |  |  |  |  |  |  |  |

Figure 3-7: INSTEON's Messages [21].

The only difference between the two is that the extended message contains 14 user data bytes not found in standard message.

The source address is the 24-bit number that uniquely identifies the INSTEON device originating the frame being sent. This is the address or ID code of the INSTEON device. During manufacture, this unique ID code is stored in each device in non volatile memory.

The Table 3-4 enumerates the meaning of the bit fields in the Flags byte.

| Bit | Meaning                                                                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | 000 : Direct Message<br>001 : Acknowledgment(ACK) of Direct Message                                                                                  |

| 7   | <ul><li>101 : Negative ACK(NACK) of Direct Message</li><li>110 : Group Broadcast Message</li><li>011 : ACK of Group Cleanup Direct Message</li></ul> |

| 6   | <ul><li>111: NACK of Group Cleanup Direct Message</li><li>010 : Group Cleanup Direct Message</li><li>100 : Broadcast Message</li></ul>               |

| 5   | 0 : Standard Message<br>1 : Extended Message                                                                                                         |

| 3,4 | 00 - 11 : Number of Hops have been Left.                                                                                                             |

| 1,2 | 00 – 11 : Number of Allowed Hops                                                                                                                     |

Table 3-4: Flags Field of INSTEON Message [21].

Broadcast messages contain general information with no specific destination and are not acknowledged.

Group Broadcast messages are directed to a group of devices. After sending a Group Broadcast message to a group of devices, the message originator then sends a direct Group Cleanup message to each member of the group individually, and waits for an acknowledgement back from each device.

The first four bits in Flags field of INSTEON message manage message repeating. As mentioned above, all INSTEON nodes are capable of repeating messages by receiving and retransmitting them. Without a mechanism for limiting the number of times a message can be retransmitted and an uncontrolled 'data storm' of endlessly repeated messages could saturate the network. To solve this problem, INSTEON message incorporates "Allowed Hops" and "Hops have been Left" fields. An "Allowed Hops" value of zero tells other devices within range not to retransmit the message. A no zero "Allowed Hops" value tells devices receiving the message to retransmit it depending on the "Hops have been Left" field. If the "Hops have been Left" value is no zero, the receiving device decrements the "Hops have been Left" value. Devices that receive a message with a "Hops have been Left" value of zero will not retransmit the message. Also, a device that is the intended recipient of a message will not retransmit the message, no matter what the "Hops have been Left" value is.

The Commands field in INSTEON message made up of Commands 1 byte and Commands 2 byte. The usage of this sub fields depends on the message type (Direct, Broadcast, etc.). For example, in Direct messages the Command 1 value 0x11 meaning switch on and has a parameter in Command 2 ranging from 0x00 to 0xFF representing the on level [22].

INSTEON messages sent over the power lines are fragmented into frames, with each frame sent in conjunction with zero crossing of AC voltage on power line (Figure 3-6).

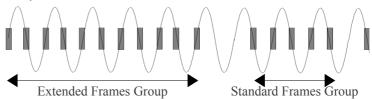

Standard Messages use a group of five frames and Extended Messages use a group of eleven frames, as Figure 3-8 shown.

A Start Frame (SF) is transmitted first in both the Standard and Extended Messages. The remaining message information is transmitted in Body Frames (BF).

| Standard Message Frames Group |    |    |    |    |  |  |  |  |  |  |

|-------------------------------|----|----|----|----|--|--|--|--|--|--|

| SF                            | BF | BF | BF | BF |  |  |  |  |  |  |

|    | Extended Message Frames Group |    |    |    |    |    |    |    |    |    |  |  |  |  |  |

|----|-------------------------------|----|----|----|----|----|----|----|----|----|--|--|--|--|--|

| SF | BF                            | BF | BF | BF | BF | BF | BF | BF | BF | BF |  |  |  |  |  |

Figure 3-8: INSTEON messages Fragmentation [21].

Both Start and Body frames consist of 24 bits and begin with a series of Sync Bits. Following the Sync Bits are four Start Code Bits. The remaining bits in a frame are INSTEON Message bits (Figure 3-9).

The total available space for INSTEON Message bits in a Standard frame group is 84, or  $10\frac{1}{2}$  bytes. So, as the standard message consist of 10 bytes the last four bits in a Standard frame group are ignored (stuffing).

|   | Start Frame                  |   |   |   |   |   |    |   |   |    |    |     |    |    |      |      |      |   |   |   |   |   |   |

|---|------------------------------|---|---|---|---|---|----|---|---|----|----|-----|----|----|------|------|------|---|---|---|---|---|---|

| 1 | 0                            | 1 | 0 | 1 | 0 | 1 | 0  | 1 | 0 | 0  | 1  | x   | x  | X  | X    | X    | x    | x | x | X | X | X | x |

|   | 8 Sync bits 4 Start Codubits |   |   |   |   |   | de |   |   | 12 | IN | STE | ON | Me | essa | ge b | oits |   |   |   |   |   |   |

|          | Body Frame                              |      |             |            |    |  |  |  |  |  |    |    |     |    |    |      |      |      |  |  |  |  |  |

|----------|-----------------------------------------|------|-------------|------------|----|--|--|--|--|--|----|----|-----|----|----|------|------|------|--|--|--|--|--|

| 1        | 1 0 1 0 0 1 x x x x x x x x x x x x x x |      |             |            |    |  |  |  |  |  |    |    |     |    |    |      |      |      |  |  |  |  |  |

| Sy<br>bi | 2<br>rnc<br>its                         | 4 \$ | Start<br>bi | t Co<br>ts | de |  |  |  |  |  | 18 | IN | STE | ON | Me | essa | ge b | oits |  |  |  |  |  |

Figure 3-9: Start and Body Frame Structures [21].

INSTEON transmitters wait for at least one zero crossing after each Standard message and two zero crossings after each Extended message before sending another message (Figure 3-10).

Figure 3-10: Frames Group Transmission [21].

These waiting times after sending power line messages are to allow sufficient time for INSTEON RF devices, if present, to retransmit a power line message.

If the originator of an INSTEON direct message does not receive an ACK from the intended recipient, the message originator will automatically try resending the message up to five times. In case a message did not get through because the number of "Allowed Hops" was set too low, each time the message originator retries a message, it also increases this number up to the limit of three. A larger number of Max Hops can achieve greater range for the message by allowing more devices to retransmit it.

#### 3.6 Universal Powerline Bus (UPB)

UPB is a low speed peer-to-peer protocol designed by Power Control System Inc., of Northridge California. It has two patents issued, the 6,734,784, granted May 11, 2004, which is titled "Zero Crossing Based Powerline Pulse Position Modulated Communication System" and the 6,784,790, granted August 31, 2004, which is titled "Synchronization/Reference Pulse-Based Powerline Pulse Position Modulated Communication System".

UPB protocol can be used in the presence of the most power line protocol (X10, INSTEON, etc.) with no interference between either UPB or them.

UPB devices have not been developed for 50 Hz power lines yet.

#### 3.6.1 Media Layer

The UPB protocol uses only electrical power lines as media transmission.

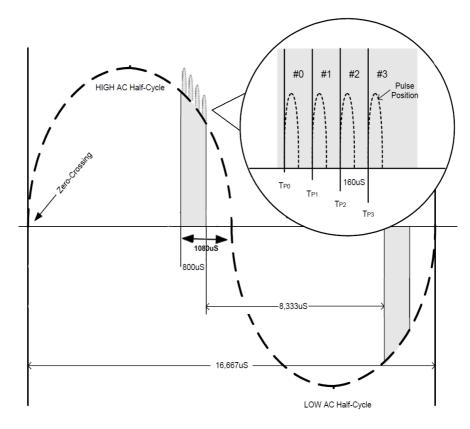

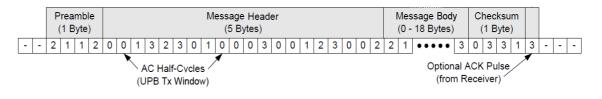

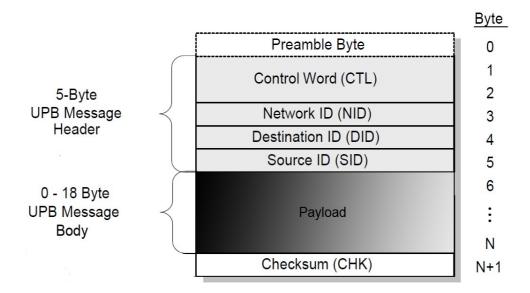

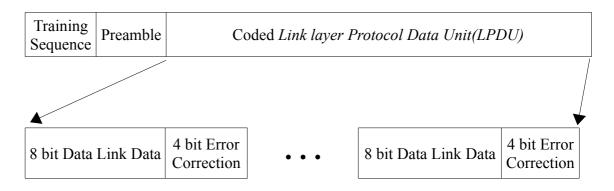

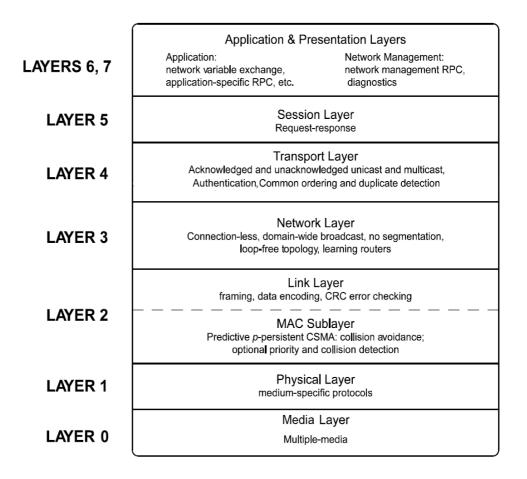

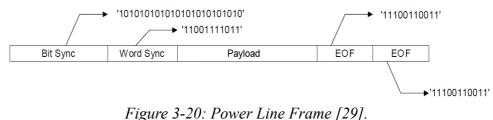

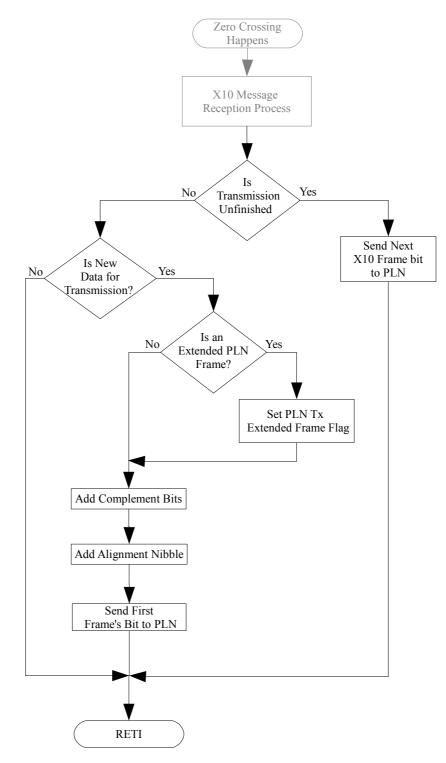

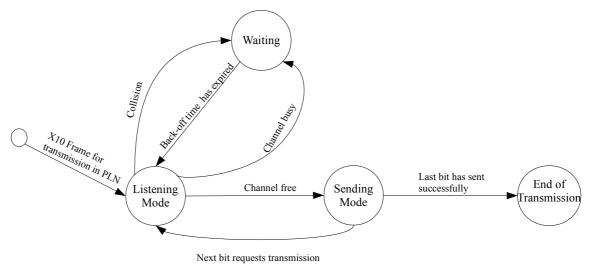

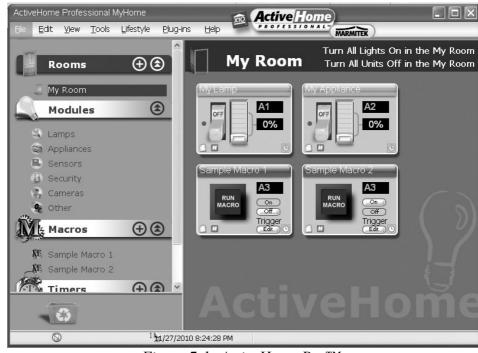

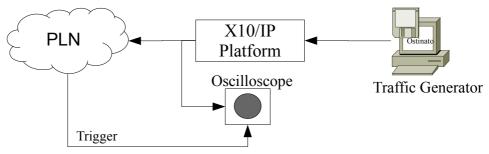

#### **3.6.2** Physical Layer