# An 'Active' Passive-Filter Topology for Low Power DC/AC Inverters

# By

Mahmoud Fayez Arman

Submitted in partial fulfilment of the requirements for the degree of

Doctor of Philosophy

Electronics and Computer Engineering

School of Engineering and Design

**Brunel University**

London, UK

### **Abstract**

This thesis presents a new output passive filter for voltage source inverter applications which is based on a shunt connected single tuned filter topology. The proposed circuit has the advantage of tracing harmonic components wherever its location in the frequency spectrum. The change in the harmonic location might be as a result of a change in the inverter operating frequency. Also, the proposed filter achieves harmonic reduction close to the traditional single tuned passive filter. In order to show the superiority of the proposed model, a comparison is introduced with other self tuning harmonic filters showing merits and drawbacks of each technique. The proposed circuit (when integrated in square wave inverter) has also shown a tremendous reduction in the switching losses in comparison with high frequency Pulse Width Modulation inverter. Mathematical analyses showing the design of the proposed filter together with extensive simulation results to verify the design are also introduced. The practical implementation of the system is presented and the results show excellent agreement with the theory and simulation. In order to appreciate the proposed filter a new method for classifying passive power filters is introduced. The review includes a comparison of these configurations showing their merit and drawbacks.

70 my Parents, Jayez, Khadijeh & Sweet sisters, Mai, Mira, Mayar

# Acknowledgements

My gratitude and thanks are due to Almighty Allah the one who supported me and blessed me with good health, power and time during my work period. The deepest appreciation and thanks to my supervisor Dr. Mohamed K. Darwish, Brunel University-London, for his guidance, assistance and encouragement throughout my PhD study. His advice and moral support were very helpful for the achievement of this thesis and are gratefully acknowledged.

Also, special thanks and gratitude are due to Dr. Christos Marouchos, Cyprus University of Technology, for his invaluable help, discussions and encouragement. Also, I would like to express my thanks and appreciation for the kind support and help from Brunel's power laboratory technicians, Tony and Chris, and Dr. Michael Theodoridis. I also thank the staff and my colleagues at the Brunel Institute of Power Systems (BIPS research group), specially members of Room H306 for their support and friendship.

Last but not least, I would like to pass my special gratitude to my father, my mother, and my sweet sisters for their patience and their emotional support along the time of conducting this research. Special dedication is to the soul of my grandmothers, Amina and Jamila, and my grandfathers, Yousif and Mahmoud.

| <b>Table of Contents</b>                                                     | Page No. |

|------------------------------------------------------------------------------|----------|

| Abstract                                                                     | IV       |

| Acknowledgements                                                             | II       |

| List of Tables                                                               | VIII     |

| List of Figures                                                              | IX       |

| List of Symbols                                                              | XIII     |

| List of Abbreviations                                                        | XIV      |

| Chapter 1                                                                    | 1        |

| Introduction                                                                 | 1        |

| 1.1 Preface                                                                  | 1        |

| 1.2 Description of Power Harmonics Phenomena                                 | 3        |

| 1.3 Sources and Effects of Power Harmonics                                   | 4        |

| 1.4 Thesis Aim and Outline                                                   | 6        |

| Chapter 2                                                                    | 8        |

| Classification of Power Electronic Filters                                   | 8        |

| 2.1 Introduction                                                             | 8        |

| 2.2 Classification of Passive Power Filters                                  | 8        |

| 2.2.1 Classification According Based on Connection and Compensated Harmonics | 10       |

| 2.2.1.1 Series-Connected AC Reactor                                          | 10       |

| 2.2.1.2 Shunt-Connected Passive Filter                                       | 10       |

| 2.2.2 Classification According to Parameters in the Circuit                  | 17       |

| 2.2.2.1 Fixed Passive Filter                                                 | 18       |

| 2.2.2.2 Variable Passive Filter                                              | 18       |

| 2.2.3 Classification According to Point of Common Coupling                   | 20       |

| 2.3 Overview of Active Power Filters                                         | 21       |

| 2.3.1 Configurations of Active Power Filters                                 | 22       |

| 2.3.1.1 Shunt Active Power Filters                                           | 23       |

| 2.3.1.2 Series Active Power Filters                                          | 25       |

| 2.3.1.3 Hybrid Active Power Filters                                          | 26       |

| 2.3.1.3.1 Series / Shunt Active Power Filters                                | 26       |

| 2.3.1.3.2 Series Active / Shunt Passive Power Filters                        | 27       |

| 2.3.1.3.3 Shunt Active / Shunt Passive Power Filters                         | 27       |

| 2.4 General Comparison of Power Electronic Filters                           | 28       |

| 2.5 Summary                                                                  | 31       |

| Chapter 3                                                                                   | 32           |

|---------------------------------------------------------------------------------------------|--------------|

| Investigation of Power Electronic Voltage Source H-bridge Inverters                         | 32           |

| 3.1 Introduction                                                                            | 32           |

| 3.2 Voltage Source H-bridge Inverters                                                       | 32           |

| 3.2.1 Traditional H-bridge VSI                                                              | 34           |

| 3.2.2 Common Modulation Methods for Traditional H-bridge VSI                                | 37           |

| 3.2.2.1 Low Frequency Square Wave Modulation                                                | 37           |

| 3.2.2.2 High Frequency Sinusoidal PWM Modulation                                            | 37           |

| 3.2.3 Multilevel Cascaded H-bridge VSI                                                      | 42           |

| 3.2.4 Common Modulation Methods for Multilevel Cascaded H-bridge VSI                        | 45           |

| 3.2.4.1 Low Frequency Staircase Wave Modulation                                             | 46           |

| 3.2.4.2 High Frequency Multicarrier SPWM Modulation                                         | 47           |

| 3.2.4.3 Hybrid Frequency Modulation – HV-LV Stages                                          | 51           |

| 3.3 General Comparison of Voltage Source H-bridge Inverters                                 | 52           |

| 3.4 Summary                                                                                 | 54           |

| Chapter 4                                                                                   | 55           |

| The Switched Capacitor Circuit applied to the proposed Output Filter for Po<br>Inverter     | wer<br>55    |

| 4.1 Introduction                                                                            | 55           |

| 4.2 Switched Capacitor Circuit                                                              | 55           |

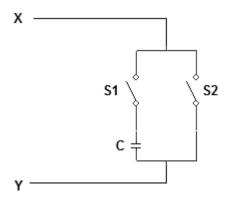

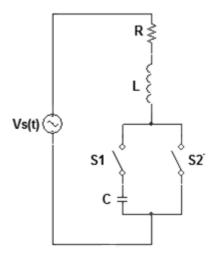

| 4.2.1 Single Capacitor, Double Switch (SCDS) Circuit                                        | 56           |

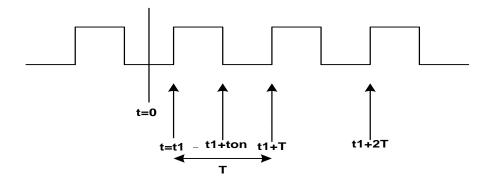

| 4.2.1.1 Switching Function Analysis of SCDS Circuit                                         | 59           |

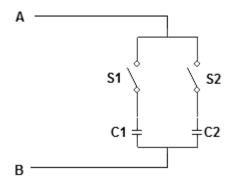

| 4.2.2 Double Capacitor, Double Switch (DCDS) Circuit                                        | 67           |

| 4.3 Other Topologies of Switched Capacitor Circuit                                          | 74           |

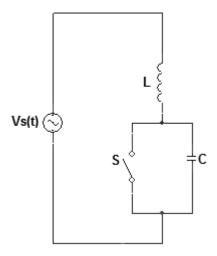

| 4.3.1 Single Capacitor, Single Switch (SCSS) Circuit                                        | 74           |

| 4.3.2 Triple Switch SCC configurations                                                      | 75           |

| 4.4 Selection Criteria of SCC for the Proposed Output Filter                                | 77           |

| 4.5 Summary                                                                                 | 79           |

| Chapter 5                                                                                   | 81           |

| Simulation Modelling and Implementation of the Proposed Single Capacitor I<br>Switch Filter | Double<br>81 |

| 5.1 Introduction                                                                            | 81           |

| 5.2 Computer Simulation Modelling of SCDS Tuned Output Passive Filter                       | 82           |

| 5.2.1 Orcad PSPICE Software                                                                 | 82           |

| 5.2.2 Parameters and Components of the Simulated Model                                      | 84           |

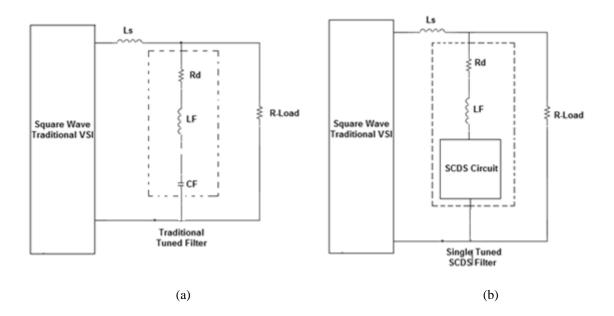

| 5.2.3 Single Tuned Output Passive Filter for Traditional VSI                                | 84           |

| 86  |

|-----|

| 87  |

| 87  |

| 88  |

| 88  |

| 89  |

| 89  |

| 91  |

| 93  |

| 94  |

| 97  |

| 109 |

| 111 |

| 111 |

| 111 |

| 115 |

| 116 |

|     |

| 123 |

| 124 |

| 125 |

| 127 |

| 130 |

|     |

| List of Tables                                                                      | Page No. |

|-------------------------------------------------------------------------------------|----------|

| Table 2-1 Comparison of Common Power Electronic Filters                             | 29       |

| Table 3-1 H-bridge VSI Switching States                                             | 36       |

| Table 3-2 Multilevel Cascaded H-bridge VSI Switching States (5-Level CHB)           | 46       |

| Table 3-3 Comparison of Voltage Source H-bridge Inverters                           | 53       |

| Table 4-1 Comparison between Switched Capacitor Circuits for the Selection Criteria | ia 78    |

| <b>Table 5-1</b> Proposed Filter Parameters                                         | 84       |

| List of Figures                                                                               | Page No. |

|-----------------------------------------------------------------------------------------------|----------|

| <b>Figure 2.1</b> Classification of passive filter configuration based on connection type     | 9        |

| Figure 2.2 Low Pass L-filter                                                                  | 11       |

| Figure 2.3 Band Pass Tuned filter, Single and Double tuned Filter configuration               | 12       |

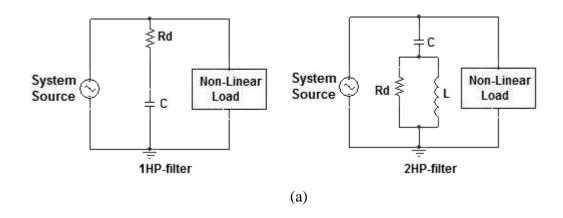

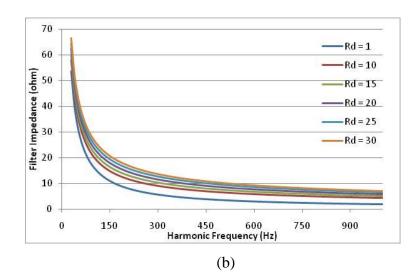

| <b>Figure 2.4</b> High Pass filter, 1st order and 2nd order HP filters                        | 13       |

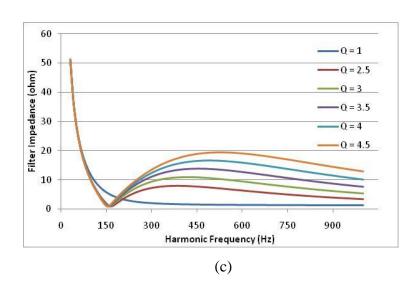

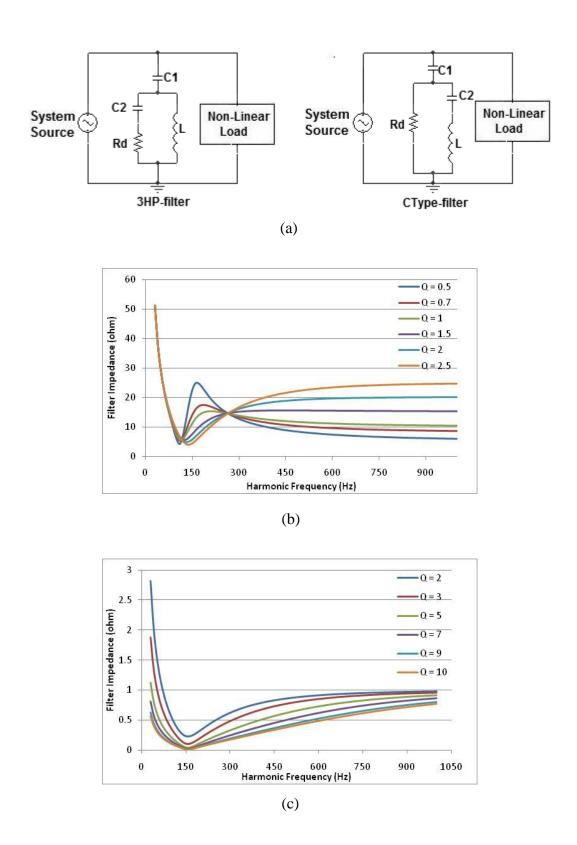

| <b>Figure 2.5</b> High Pass filter, 3rd order and C-Type HP filter                            | 16       |

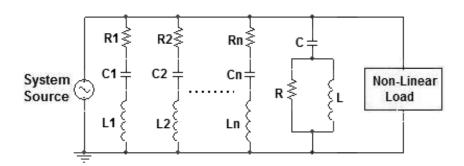

| Figure 2.6 Composite passive filter                                                           | 17       |

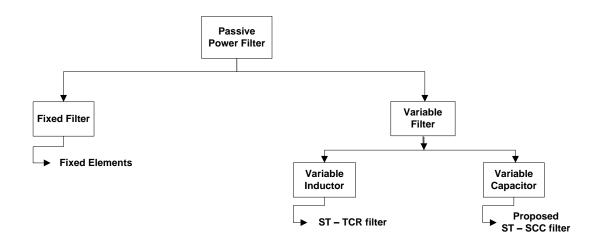

| <b>Figure 2.7</b> Classification of passive filter configuration based on element's parameter | rs 18    |

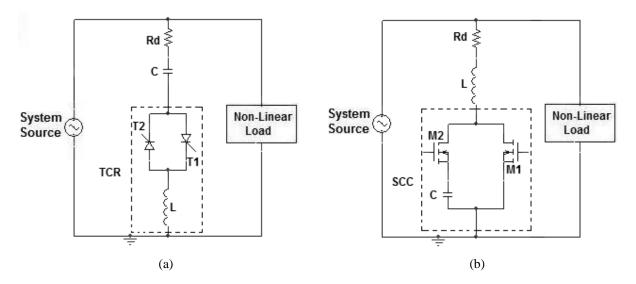

| Figure 2.8 Variable passive filter configurations                                             | 19       |

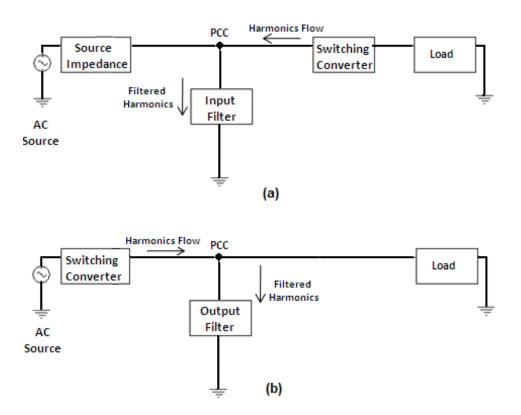

| Figure 2.9 Passive Filter classification according to place of insertion                      | 21       |

| Figure 2.10 Classification of active power filters configurations                             | 22       |

| Figure 2.11 Generalized block diagram for Active Power Filters                                | 22       |

| Figure 2.12 Shunt active power filter configuration                                           | 24       |

| Figure 2.13 Power circuit configurations of shunt APF VSI                                     | 24       |

| Figure 2.14 Series active power filter configuration                                          | 26       |

| Figure 2.15 Series / Shunt active power filter configuration                                  | 27       |

| Figure 2.16 Series active / Shunt passive power filter configuration                          | 28       |

| Figure 2.17 Shunt active / Shunt passive power filter configuration                           | 28       |

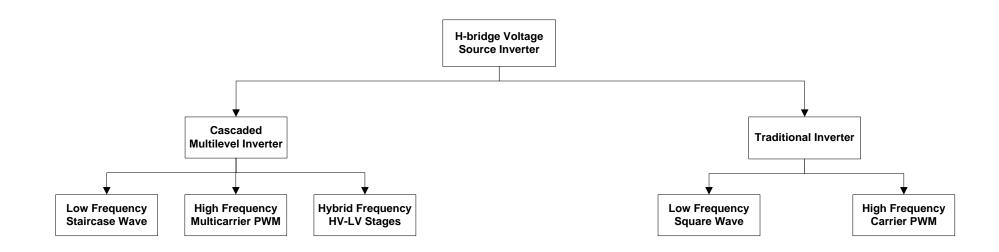

| Figure 3.1 Classification of H-bridge voltage source inverters                                | 33       |

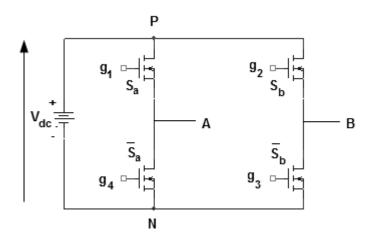

| Figure 3.2 Single Phase H-bridge voltage source inverters                                     | 34       |

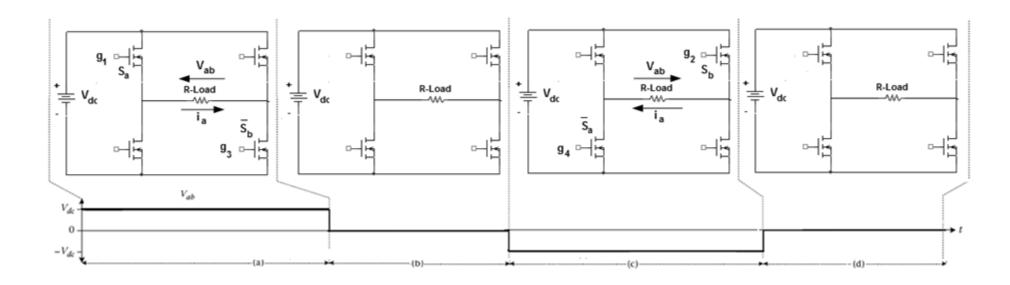

| Figure 3.3 H-bridge inverter switching states                                                 | 35       |

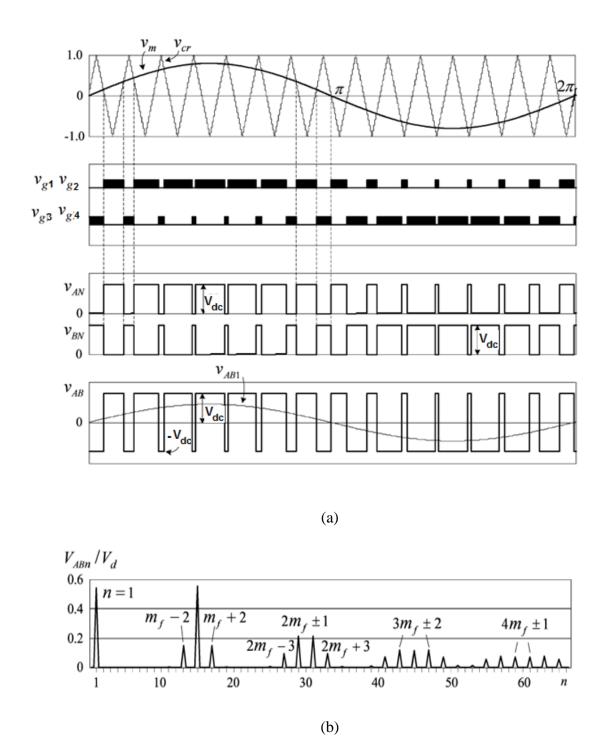

| Figure 3.4 Bipolar SPWM for H-bridge voltage source inverter                                  | 39       |

| Figure 3.5 Unipolar SPWM for H-bridge voltage source inverter                                 | 41       |

| Figure 3.6 Voltage Source Cascaded H-bridge Multilevel Inverter Topology                      | 44       |

| Figure 3.7 Output voltage of an 11-level multilevel cascaded H-bridgeVSI                      | 44       |

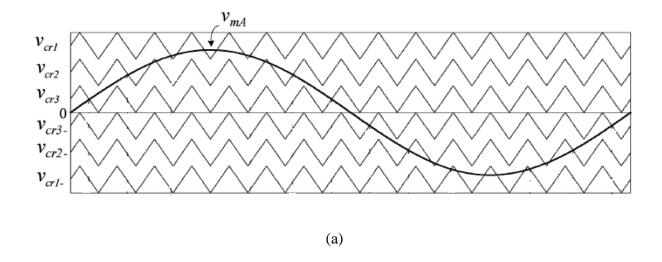

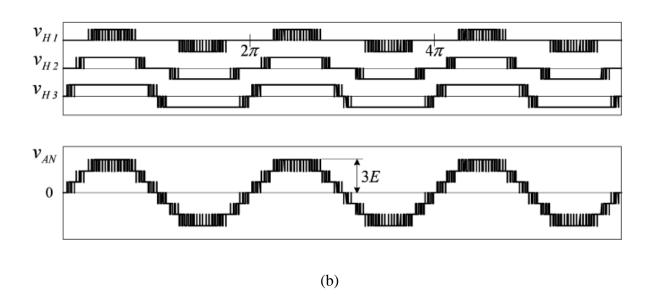

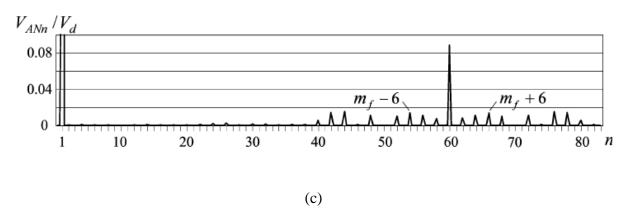

| Figure 3.8 Phase-shifted SPWM scheme for seven level CHB inverter                             | 48       |

| Figure 3.9 Level-shifted SPWM scheme for seven level CHB inverter                             | 50       |

| Figure 3.10 CHB inverter modulated by hybrid switching frequency scheme                       | 52       |

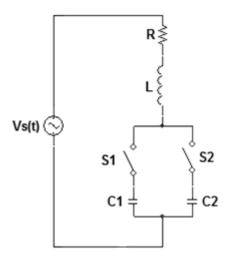

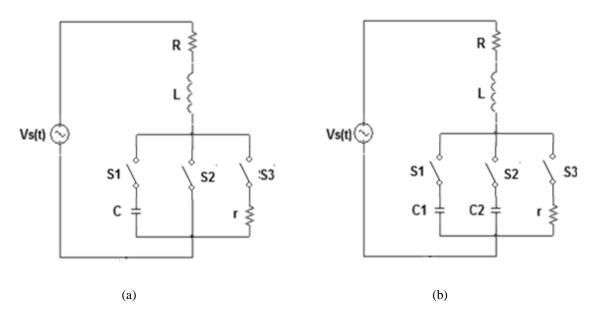

| Figure 4.1 Single Capacitor Double Switch Circuit                                             | 56       |

| Figure 4.2 Single Capacitor Double Switch Circuit (SCDS) with inductor current lim            | iter 57  |

| Figure 4.3 The Switching Function                                                             | 59       |

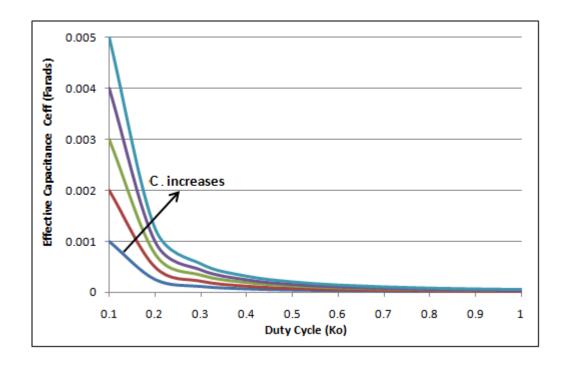

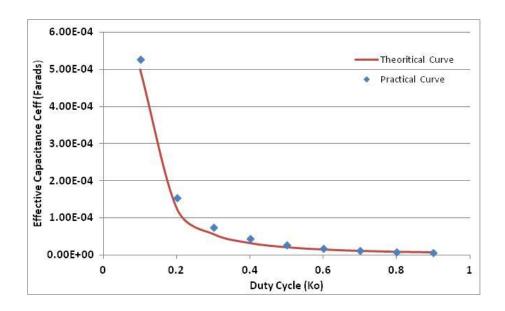

| Figure 4.4 Relation between duty cycle, and effective capacitance of SCDS circuit             | 67       |

| Figure 4.5 Double Capacitor Double Switch Circuit                                             | 68       |

| Figure 4.6 Double Capacitor Double Switch Circuit                                             | 68       |

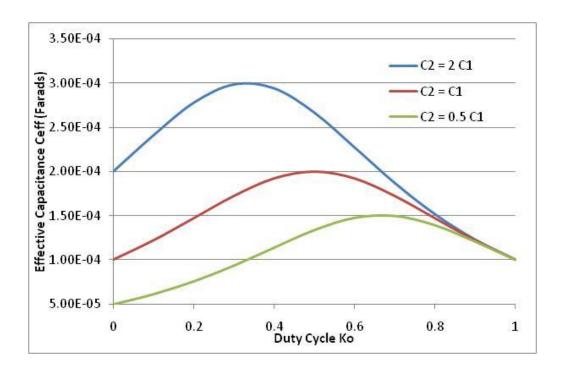

| Figure 4.7 Relation between duty cycle, and effective capacitance of DCDS (S1)                | 72       |

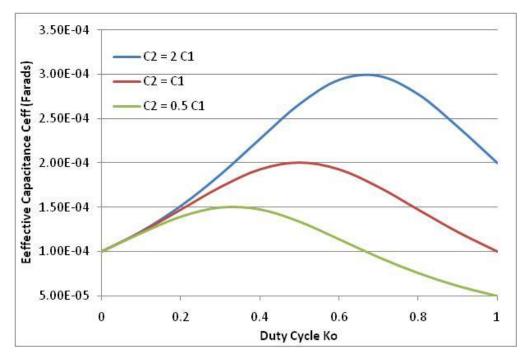

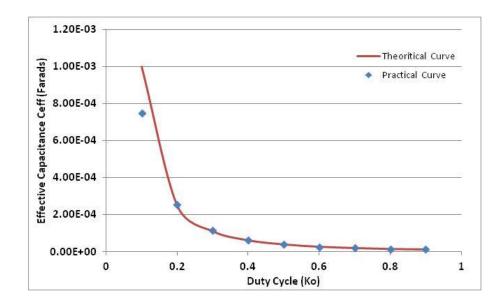

| Figure 4.8 Relation between duty cycle, and effective capacitance of DCDS (S2)         | 73   |

|----------------------------------------------------------------------------------------|------|

| Figure 4.9 Single Capacitor Single Switch Circuit with inductor current limiter        | 75   |

| Figure 4.10 Triple Switched Capacitor Circuits configurations, a: SCDS, and b: DCDS    | 76   |

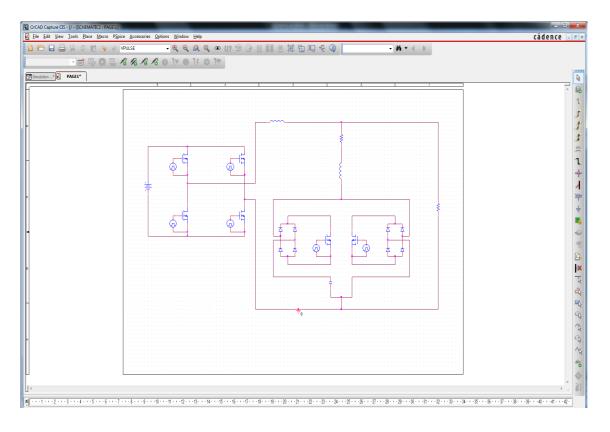

| Figure 5.1 Circuit Modeling using Orcad Pspice Software                                | 83   |

| Figure 5.2 A schematic overview of a: the Traditional and Proposed Single Tuned Filter | r 85 |

| Figure 5.3 Proposed Single Tuned Filter utilizing Single Capacitor Double Switch       | 86   |

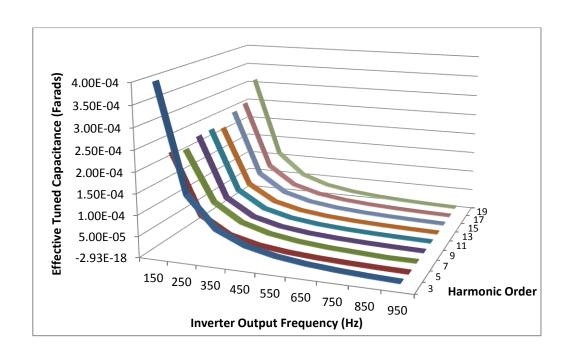

| Figure 5.4 Tuned Effective Capacitance (Theoretical)                                   | 90   |

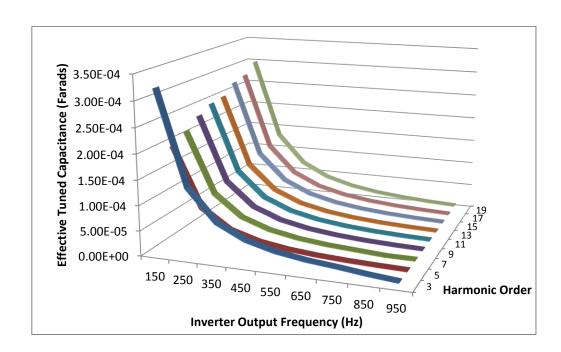

| Figure 5.5 Tuned Effective Capacitance (Simulation)                                    | 90   |

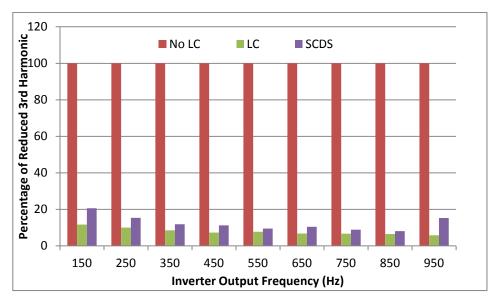

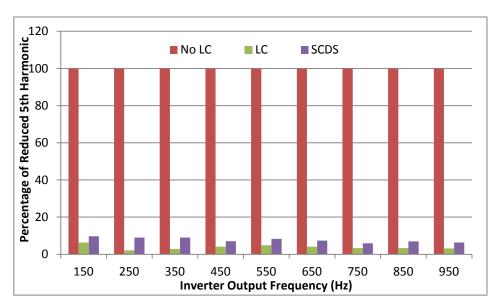

| Figure 5.6 Percentage of reduced 3rd harmonic (Simulation)                             | 91   |

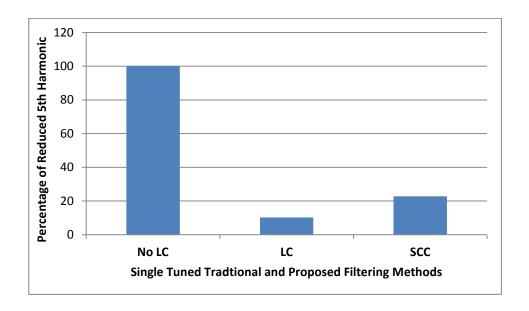

| Figure 5.7 Percentage of reduced 5th harmonic (Simulation)                             | 91   |

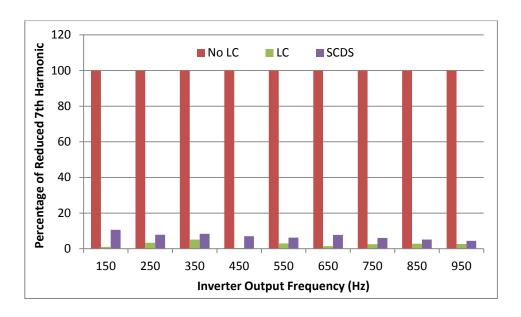

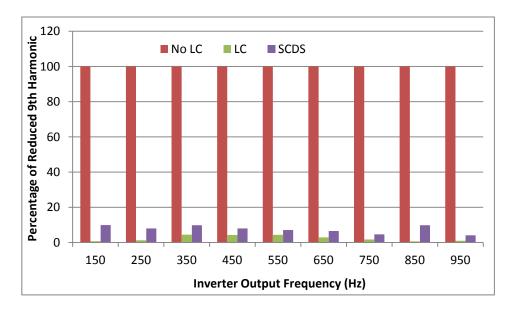

| Figure 5.8 Percentage of reduced 7th harmonic (Simulation)                             | 92   |

| Figure 5.9 Percentage of reduced 9th harmonic (Simulation)                             | 92   |

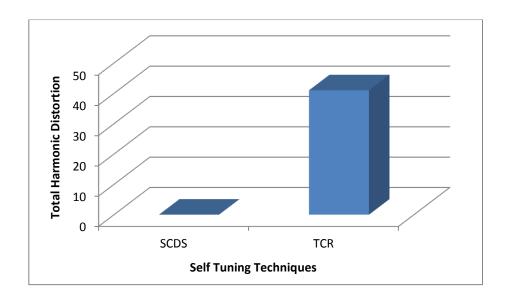

| Figure 5.10 Total Harmonic Distortion for TCR and SCDS                                 | 94   |

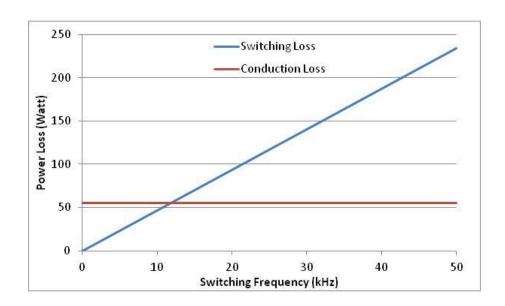

| Figure 5.11 Switching loss and Conduction loss in term of Switching frequency          | 95   |

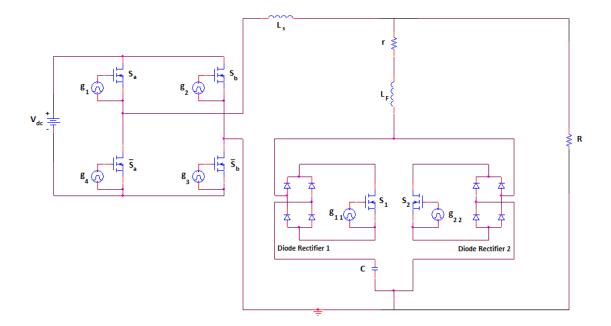

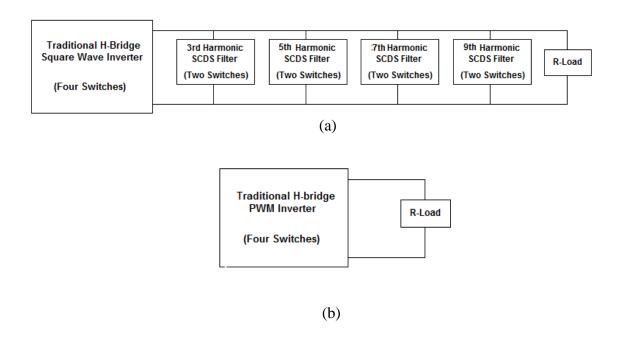

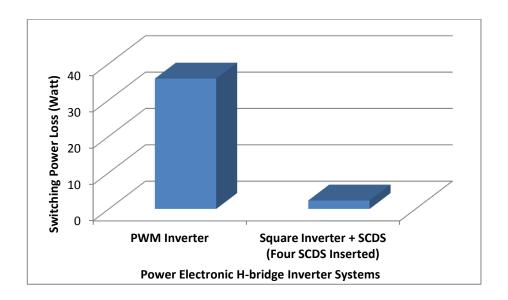

| Figure 5.12 Two voltage source inverter systems                                        | 95   |

| Figure 5.13 Switching power losses in two power electronic H-bridge inverter systems   | 96   |

| Figure 5.14 The proposed system showing traditional and new single tuned filter        | 98   |

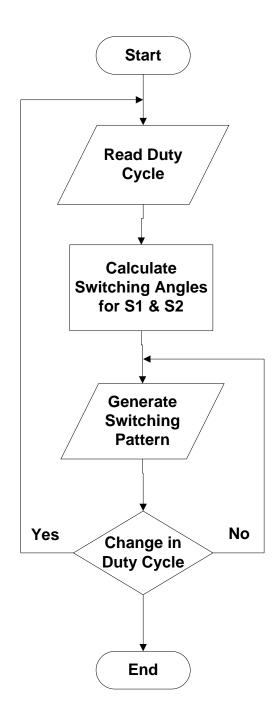

| Figure 5.15 Flowchart of the programmable generation of the switches' duty cycle       | 99   |

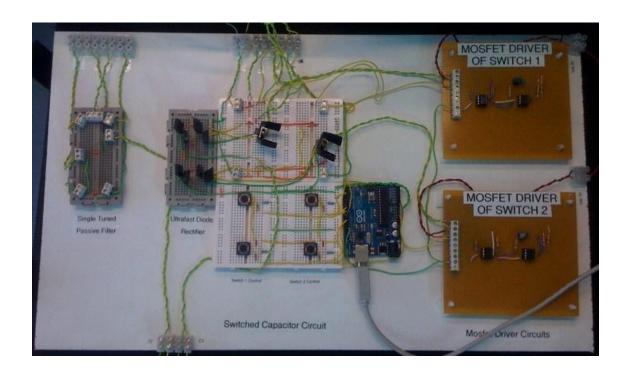

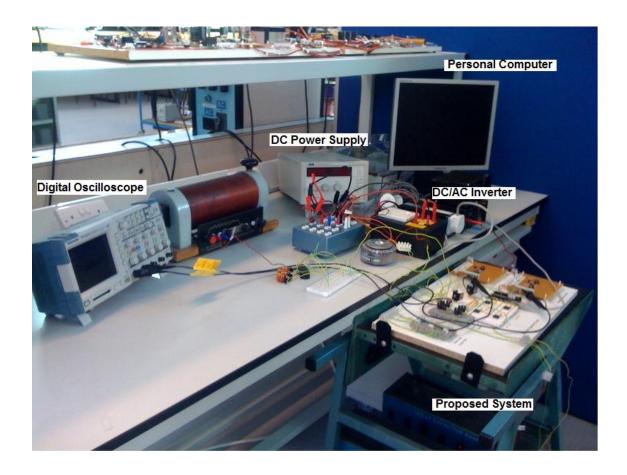

| Figure 5.16 The experimental setup showing the proposed system                         | 100  |

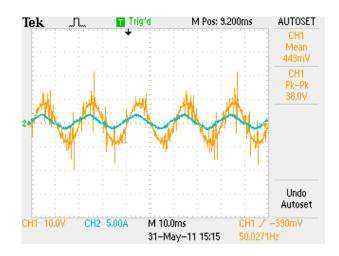

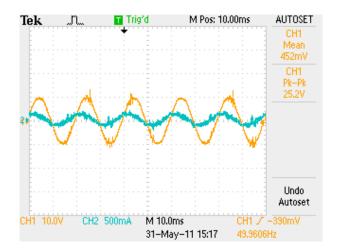

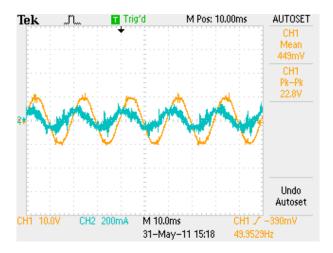

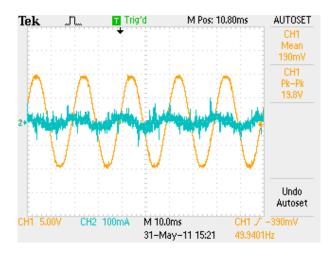

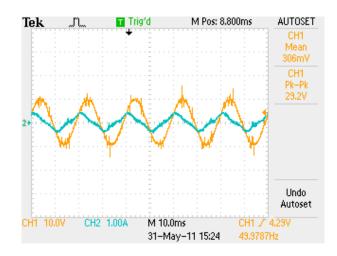

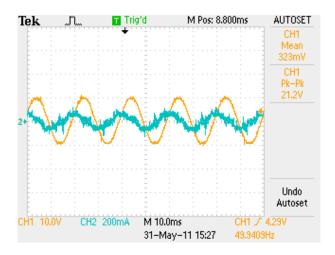

| <b>Figure 5.17</b> Voltage and Current wavefrom at $K_o$ =0.1, (C=5 $\mu F$ )          | 101  |

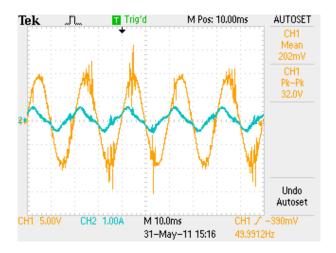

| <b>Figure 5.18</b> Voltage and Current wavefrom at $K_o$ =0.2, (C=5 $\mu F$ )          | 101  |

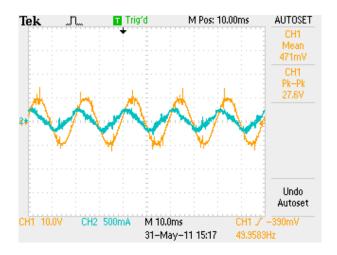

| <b>Figure 5.19</b> Voltage and Current wavefrom at $K_o$ =0.3, (C=5 $\mu$ F)           | 101  |

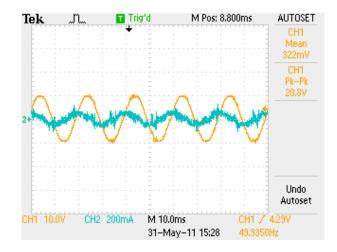

| <b>Figure 5.20</b> Voltage and Current wavefrom at $K_o$ =0.4, (C=5 $\mu$ F)           | 102  |

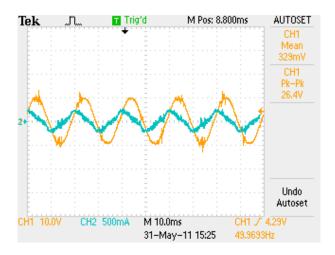

| <b>Figure 5.21</b> Voltage and Current wavefrom at $K_o$ =0.5, (C=5 $\mu$ F)           | 102  |

| <b>Figure 5.22</b> Voltage and Current wavefrom at $K_o$ =0.6, (C=5 $\mu$ F)           | 102  |

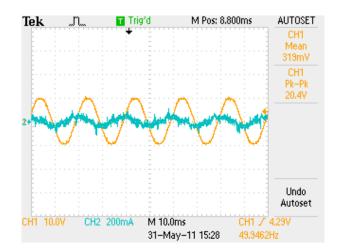

| <b>Figure 5.23</b> Voltage and Current wavefrom at $K_o$ =0.7, (C=5 $\mu$ F)           | 103  |

| <b>Figure 5.24</b> Voltage and Current wavefrom at $K_o$ =0.8, (C=5 $\mu$ F)           | 103  |

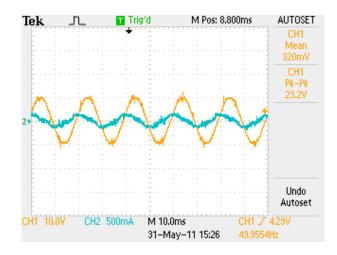

| <b>Figure 5.25</b> Voltage and Current wavefrom at $K_o$ =0.9, (C=5 $\mu$ F)           | 103  |

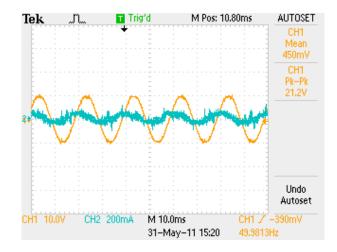

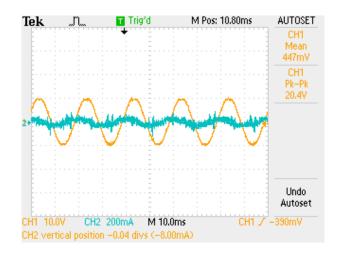

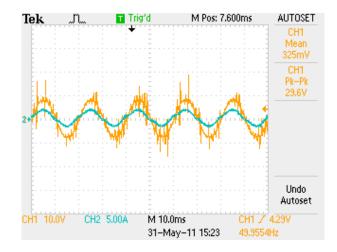

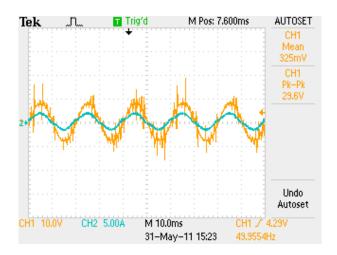

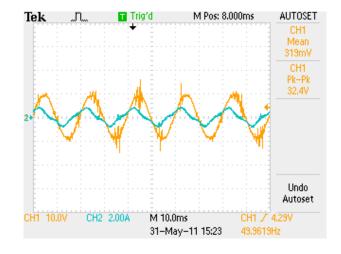

| <b>Figure 5.26</b> Voltage and Current wavefrom at $K_o$ =0.1, (C=10 $\mu$ F)          | 104  |

| <b>Figure 5.27</b> Voltage and Current wavefrom at $K_o$ =0.2, (C=10 $\mu$ F)          | 104  |

| <b>Figure 5.28</b> Voltage and Current wavefrom at $K_o$ =0.3, (C=10 $\mu$ F)          | 105  |

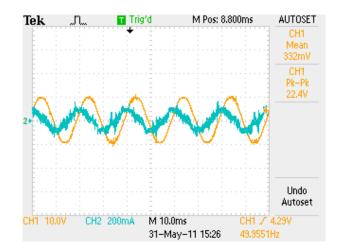

| <b>Figure 5.29</b> Voltage and Current wavefrom at $K_o$ =0.4, (C=10 $\mu$ F)          | 105  |

| <b>Figure 5.30</b> Voltage and Current wavefrom at $K_o$ =0.5, (C=10 $\mu$ F)          | 105  |

| <b>Figure 5.31</b> Voltage and Current wavefrom at $K_o$ =0.6, (C=10 $\mu$ F)          | 106  |

| <b>Figure 5.32</b> Voltage and Current wavefrom at $K_o$ =0.7, (C=10 $\mu F$ )         | 106  |

| <b>Figure 5.33</b> Voltage and Current wavefrom at $K_0=0.8$ , (C=10 $\mu$ F)          | 106  |

| <b>Figure 5.34</b> Voltage and Current wavefrom at K <sub>o</sub> =0.9, (C=10 μF) | 107 |

|-----------------------------------------------------------------------------------|-----|

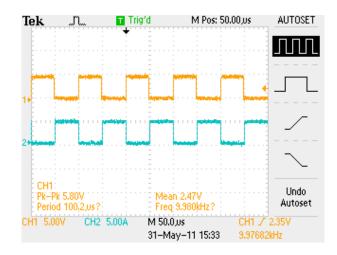

| <b>Figure 5.35</b> Anti-parallel switching pulses at K <sub>o</sub> =0.5          | 107 |

| <b>Figure 5.36</b> Experimental results of SCDS (Fixed = $5 \mu F$ )              | 108 |

| <b>Figure 5.37</b> Experimental results of SCDS (Fixed = $10 \mu F$ )             | 108 |

| Figure 5.38 Experimental results showing the percentage of reduced 5th harmonic   | 109 |

# **List of Symbols**

$\theta$ ,  $\phi$  Phase Angle

Ø High Frequency Component of Switching Function

ω Angular Frequency

ω<sub>s</sub> Switching Angular Frequency

$\gamma$   $C_2/C_1$

A<sub>0</sub>, A<sub>n</sub>, B<sub>n</sub> Fourier Coefficients

b Number of DC Sources

C Capacitance

C<sub>eff</sub> Effective Capacitance

C<sub>eff-max</sub> Maximum-Effective Capacitance

F(t) Switching Function

f<sub>r</sub> Tuning or Resonance Frequency

f<sub>s</sub> Switching Frequency

I Instantaneous Phase Current

*Î* Peak Value of Current

i<sub>1</sub> Fundamental Component of Current

I<sub>m</sub> Maximum Current

i<sub>t</sub> Total Load Current

K<sub>o</sub> Duty Cycle

K<sub>o-min</sub> Minimum-Duty Cycle

L Inductance

L<sub>F</sub> Tuned Filter Inductance

m Voltage Level number

m<sub>f</sub> Frequency Modulation Index

n Harmonic Number

Q Quality Factor

R, r Resistance

Rd Damping Resistance

S Switch

T Time Period

t Time

t<sub>off</sub> OFF Time

t<sub>on</sub> ON Time

$\hat{V}_{XY}$ ,  $\hat{V}_{AB}$  Peak Value of Voltage

V<sub>a</sub> Instantaneous Voltage Level

V<sub>ab</sub> Output Voltage

$V_{abn}$  RMS voltage of nth order Harmonic

V<sub>an</sub> Voltage terminal across an

V<sub>bn</sub> Voltage terminal across bn

V<sub>c</sub> Capacitor Voltage

V<sub>cr</sub> Carrier Signal

V<sub>dc</sub> DC Voltage

V<sub>g</sub> Gate signal

V<sub>L</sub> Inductor Voltage

V<sub>m</sub> Modulating Signal

V<sub>R</sub> Resistor Voltage

$V_s \hspace{1cm} Supply \hspace{0.1cm} Voltage$

X<sub>c</sub> Capacitive Reactance

X<sub>ceff</sub> Effective capacitive Reactance

X<sub>L</sub> Inductive Reactance

# **List of Abbreviations**

1HP First-Order High Pass Filter

2HP Second-Order High Pass Filter

3HP Third-Order High Pass Filter

APF Active Power Filter

ASD Adjustable Speed Drive

BJT Bipolar Junction Transistor

CHB Cascaded H-bridge

DCDS Double Capacitor Double Switch

DSP Digital Signal Processor

DT Double Tuned Filter

FACTS Flexible AC Transmission System

GTO Gate Turn-off Thyristor

H H-bridge Cell

HAPF Hybrid Active Power Filter

HV-LV High Voltage-Low Voltage Stage

IGBT Insulated Gate Bipolar Transistor

LS-SPWM Level Shifted-Sinusoidal Pulse Width Modulation

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PC Personal Computer

PCC Point of Common Coupling

PIC Peripheral Interface Controller

PPF Passive Power Filter

PS-SPWM Phase Shifted-Sinusoidal Pulse Width Modulation

PWM Pulse Width Modulation

RES Renewable Energy Source

RMS Root Mean Square

SCC Switched Capacitor Circuit

SCSS Single Capacitor Single Switch

SPICE Simulation Program with Integrated Circuit Emphasis

SPWM Sinusoidal Pulse Width Modulation

ST Single Tuned Filter

T Thyristor

TCR Thyristor Controlled Reactor

THD Total Harmonic Distortion

UPS Uninterruptible Power Supply

VSI Voltage Source Inverter

VS-MLI Voltage Source-Multilevel Inverter

# Chapter 1

## Introduction

### 1.1 Preface

In more than a decade, the field of electric power quality has grown tremendously. This is due to a considerable increase in the occurrence of switching power electronic circuits in power systems. This fast growth in power electronic technology is associated with the use of various power semiconductors switching devices such as thyristors, GTOs as well as transistors (BJT, MOSFET, IGBT, etc.). This growth came with a price; such as current and voltage harmonics. Small distributed loads, such as computers and television (TV) sets with switched mode power supplies at their inputs are considered to be sources of harmonics in power distribution systems. In addition, switched power electronic converters used to drive ac motors, such as adjustable speed drives, are considered to be source of harmonics to the load. In general, harmonics can be injected towards the ac source or to a sensitive load (i.e. motor). These harmonics cause problems due to their harmful effects of increasing power losses in the system, resulting in oversized power devices due to the requirement of large heat sinks. Harmonics also contribute to transformer saturation, electromagnetic interference, incorrect operation of voltage sensitive devices, and shorter life of organic insulation. All the above mentioned harmful effects have led to an incremental concern about harmonic elimination or to reduce the effect of harmonic pollution [1-4].

Inconsequence, the idea of harmonic filtration methods started to emerge and critically studied in the research environment. A large number of filter topologies and filtering techniques are proposed in literature including passive, active and hybrid

filters. The first investigated type was the passive filter. The basic principle behind passive filtering techniques is to provide a low impedance path to ground for undesired harmonics [1]. Passive filter circuits, such as shunt LC passive filters, are used to draw harmonic currents to ground. Other series configurations provide high attenuation for current harmonics, hence decreasing their magnitudes. These filters are inserted in Shunt or Series at the source of harmonics. Passive filters can be described as tuned and high pass which are used to attenuate specific harmonics and to eliminate high-order harmonics, respectively [5]. Such filters are relatively easy to design, cheap and reliable. However, it implies increasing the number of components in order to eliminate several harmonics at a given site. Active filters were introduced after passive filters. They operate by injecting harmonic current into the line system with the same magnitudes as the harmonic generated by the nonlinear load, but at opposite phases. These filters generate the opposite phase harmonics by a switching power electronic circuits such as DC/AC inverters. They are preferred over the passive filters because of their better filtering characteristics and their capability of improving the system stability by avoiding possible resonance between the filter components and the mains impedance [6-12]. However, these filters suffer from complex control and high switching losses due to the presence of active power elements. Combining the merits of both passive and active filters, hybrid filter topologies have been introduced during the last decade. The main aim of developing this type of filters is to achieve the desired filtering performance with a significant reduction of kVA effort required by the power active filter [5]. They are cost-effective solutions to suppress harmonics compared to active filters [5].

Many researchers approach the problem from the point of view of diverting or eliminating most of the undesired harmonics from the system source. This is achieved by designing and/or combining different filtering techniques (i.e. Passive, Active or Hybrid) in order to get the lowest undesired harmonic output. Most of the available filter topologies are used as an input filter (protecting system source) or as an output filter (protecting a sensitive load) for a power electronic converter. Such output filters must be flexible in order to reduce harmonics under different operating frequencies of the power electronic converter. In other words, these filters should be able to eliminate or reduce harmonics wherever its location in the frequency spectrum. In this case, other approaches are required to be investigated in this field of harmonic filtering and this is the main aim of the thesis.

### 1.2 Description of Power Harmonics Phenomena

Power systems apparatuses are designed to supply an alternating voltage and current which are purely sinusoidal. From terminological point of view, the purely sine waveform which the system is designed and is expected to operate is known as fundamental wave. The corresponding frequency is called fundamental frequency [13]. In some part of the world like United Kingdom fundamental frequency is 50 Hz and other existing value is 60 Hz [13]. In this work, fundamental frequency of 50 Hz is adopted.

Utilities endeavour to provide pure sinusoid supply to the consumers. In ideal situation, the supplied voltage and the current flowing to the end user load have waveforms of the same shape. Hypothetically, this situation is possible if the consumer is using a linear load. In practice, the current flowing through the system is a non linear function of the voltage and shows periodic distortions superimposed onto the fundamental sinusoidal current waveform [14].

These distortions can be decomposed into integer harmonics (n times 50/60), and other harmonics divided into inter harmonics and sub harmonics [14, 15]. Inter harmonics is composed of harmonics having frequencies which are greater than the fundamental frequency but not integer multiple of it. On the other hand, sub harmonics is composed of harmonics having frequencies which are smaller than the fundamental frequency and not an integer multiple of it [13]. Any current waveform, which is not linearly related to the supply voltage, is drawn from a non linear load. In general, when the current waveform contains harmonics not linearly related to those presented in the supply voltage, the non linear load is called a harmonic source [14]. Nowadays, the distortion level on the supply network is a serious concern due the proliferation of the non-linear loads in the industrial, commercial, and domestic environments [15]. Inconsequence, harmonic distortion can be considered as a sort of an electrical pollution in the power system which can cause problems if the accumulation of the harmonic currents exceeds certain limits [15].

### 1.3 Sources and Effects of Power Harmonics

The increasing use of power electronic devices has an enormous effect on the increasing attention about power quality issues such as harmonic distortion. Typical harmonic sources are adjustable speed drives (ASDs), personal computers (PCs), TVs, and many other devices that use power electronic conversion. Common harmonic sources can be categorized as follows [1,14,15]:

• Power electronic devices: the main purpose today for using switching power electronic devices the capability of drawing a current waveform and shape it in order to get the desired output (i.e. AC or DC). In other words, power electronic

converter can be viewed as a matrix of semiconductor switches that provides a flexible interconnection between input and output nodes of an electrical power system. These switches provide a good controllability on the converter output. Although this is beneficial, this has an immediate side effect which is the incremental levels of harmonics in the system. Power electronic converters include AC/DC rectifiers and DC/AC inverter and other power conversion circuits.

- Arcing devices: harmonics from these devices are generated as a result of the nonlinear relationship between the voltage and current. The main harmonic sources in this category are the electric arc furnace, and arc welders.

- Electromagnetic saturable devices: This phenomenon occurs mainly in equipments such as power transformers and electromagnetic devices with a steel core, including motors. Harmonics from these devices are generated due to the nonlinearity of the magnetic core caused by the electromagnetic saturation.

Each power system apparatus has a distinct sensitivity to harmonic distortion, and therefore harmonics flowing in power systems affect each type of apparatus differently. Harmonic distortion may have several effects such as the following:

- Transformer overheating: in transformers, the primary effect is the additional heat generated by the losses caused by the harmonic content of the load current. In this case, the designer must make different design choices for a transformer to accommodate higher frequencies [14,16,17].

- Telephone interference: it has also been observed that harmonics is a cause in the degradation of the communication system performance due to interference caused by harmonics with the communication system frequency [1,14].

- Malfunction of electronic loads: some power electronic loads are sensitive to AC supply voltage characteristics where they may malfunction [17].

- Metering errors: metering and instrumentation can be affected by harmonic components [17,18].

## 1.4 Aim and Objectives:

The aim of this research is to design a new topology of single tuned passive filter circuit which has the ability to perform the harmonic filtration process effectively. This new filter topology is designed as an output filter for DC/AC inverter. The new design leads to two significant results, first, to achieve the same performance in reducing a specific harmonic component as the traditional single tuned passive filter is capable of, secondly, is to trace any harmonic component regardless its location in the frequency spectrum. The new topology is a modification of the conventional single tuned passive filter topology. The modification is achieved by inserting a switched capacitor circuit in series with the tuned inductor. The switched capacitor circuit in this case acts as a variable capacitor which may be varied by changing the duty cycle of the semiconductor switches so that the value of the equivalent capacitance tracks the variation of the harmonic frequency profile which might be a result of a change of the operating frequency of an inverter. The novelty of introducing the switched capacitor circuit to the field of passive filtering is a main feature of this research. The main applications of the switched capacitor circuits in electrical power field are in active filtering and reactive power compensation, while no research has been conducted to introduce it to the field of passive filtering.

### 1.5 Thesis Outline:

The thesis consists of six chapters, broken down as follows: Chapter 1 is an introduction of the aim and the layout of the thesis. Chapter 2 elaborates different techniques and topologies for harmonic compensation using passive power filters with critical comparison between them. It also introduces a new method for classifying this type of filters. Also, a brief description of the other well-known methods of harmonic filtering, active and hybrid filters. Chapter 3 conducts an overview of voltage source Hbridge inverters where the proposed filter can be used as an output filter for this switching power converter. The author's contribution in chapter 2 and 3 are: critical review of different types of harmonic filters and H-bridge inverters (Traditional and Multilevel), and a comparative analysis of the reviewed topologies for the sake of determining the appropriate configuration in this research work. Chapter 4 presents the mathematical and analytical derivation of switched capacitor circuits in addition to an overview of other related topologies. A selection criterion is set in order to adopt the most accepted switched capacitor circuit configuration for the proposed filtering technique. Chapter 5 presents the modelling and the mathematical analysis of the proposed tuned passive filter using Orcad PSPICE software and simulation and practical results are presented and discussed in details. Finally the conclusions and future work are presented in chapter 6. Appendices A and B present the microcontroller program code and list of publications, respectively.

# Chapter 2

# **Classification of Power Electronic Filters**

### 2.1 Introduction

The survey of published papers on power electronic filtering techniques shows a great deal of interest in the past few years. Many references in the surveyed literature have discussed the evolution of filtering techniques over many years, including passive, active, and hybrid filters [19,20]. The interest in the subject focuses on circuit configurations with their ability to compensate specific or range of harmonics. Passive filters are given a special attention in this chapter due to the adoption of a new passive filter topology. This chapter classifies the available passive filtering techniques according to their configurations, location as well as type of connection. It also presents an overview of the other common filtering techniques (i.e. Active and Hybrid) surveyed in literature. A brief discussion is presented on the merits and drawbacks of each filtering method; leading to the provision of the main guidelines for the proposal of the adopted new passive filter in this thesis. This chapter highlights passive filter techniques in specific as it is necessary to appreciate the new proposed filter for inverter applications, which will be conducted in the following chapter.

### 2.2 Classification of Passive Power Filters

Passive filters (PPF) are constructed from passive elements (resistors, inductors, and capacitors) and thus the name [21]. Harmonic filters, passive filters in specific, come in many "shapes and sizes" and a large number of circuit configurations have

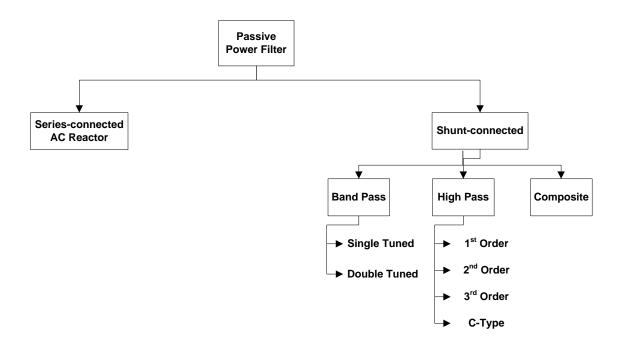

Figure 2.1 Classification of passive filter configuration based on connection type and harmonic to be compensated

been proposed in the literature to enable the compensation of harmonics in power systems. To classify these configurations for the purpose of clarifying the strengths and weaknesses of each topology, it is desirable first to distinguish and classify the overall passive filtering topologies and techniques. On the basis of the published work in the field of passive power filtering, this type of filers can be classified using the following criteria:

- 1. Topology and configuration based on connection type in the circuit (e.g. series connected or shunt connected), and harmonics to be compensated (e.g. specific and/or range of harmonics);

- 2. Type of element's parameters in the circuit (e.g. Fixed or variable filters); and

- 3. Point of common coupling (e.g. Input or Output filters)

The following Sections classify the Passive Power Filter according to the above criteria. This will provide a better understanding in dealing with these filters, as it shows the merits and limitations of each type.

# **2.2.1** Classification According to Configurations Based on Connection Type in the Circuit and Compensated Harmonics

Passive filters are composed of a combination of capacitors, inductors, and damping resistors [5]. These filters can be categorized as series, and shunt connected filters as shown in Figure 2.1. Each type of connection and related topologies is presented in the following subsections showing differences and impedance-frequency relationship for harmonic compensation.

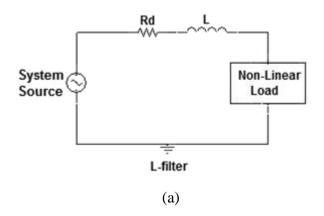

#### 2.2.1.1 Series-Connected AC Reactor

Series AC Reactor is constituted of an inductor connected in series with the nonlinear loads. This type of configuration is considered as a low pass filter. Figure 2.2a illustrates the basic configuration of series-connected reactor in the power system. It has the ability to pass low frequency harmonics, the fundamental component, and provides high impedance to high frequency harmonic currents to limit their proliferation into the power system. Figure 2.2b shows filter impedance-harmonic frequency relationship at different damping resistor values (Rd). Rd controls the minimum impedance at a harmonic frequency which sometimes reflects the internal resistance of the series reactor. The merit of this filter is in its low cost, small size, and provides no system resonance condition. However, it suffers from handling the rated full load current, and it only improves harmonic distortion from 30% to 40% at best according to related studies [21].

#### 2.2.1.2 Shunt-Connected Passive Filter

Shunt filters' passive components generally are rated for part of the system voltage (with respect to ground). Such design leads to smaller component sizes and costs.

Figure 2.2 Low Pass L-filter, (a) Filter configuration in power system and (b) Filter impedance-harmonic frequency relationship at different damping resistors

Shunt-connected passive filters can be classified into three basic categories as follows:

- 1. Band pass filters (of single or double tuned),

- 2. High pass filters (of first-, second-, or third- order, or c-type),

- 3. Composite filters.

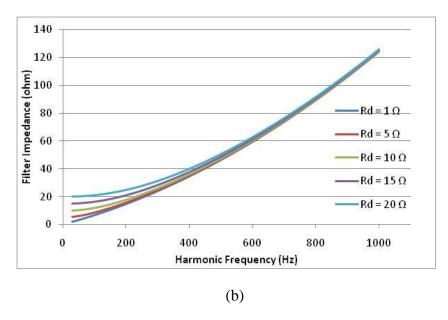

Band pass filters, including single tuned (ST) and double tuned (DT), are usually used to compensate specific harmonic frequencies. The ST filter (Figure 2.3a) contains a capacitor (C) in series with an inductor (L).

Figure 2.3 Band Pass Tuned filter, (a) Single and Double tuned Filter configuration in power system and (b) ST filter impedance-harmonic frequency relationship at different quality factors

DT filter (Figure 2.3a) is composed of two ST filters connected in shunt with the non linear load in order to tune at two harmonic frequencies. Capacitor and inductor values, in both band pass filters, are determined so that the filter's impedance is near zero or at the harmonic frequency, which bypasses that harmonic. This harmonic frequency is called the tuning frequency which is given by:

$$f_r = \frac{1}{2\pi\sqrt{LC}} \tag{2.1}$$

A damping resistor, Rd, can be inserted in series with the tuned components in order to adjust the tuning's sharpness [14].

Figure 2.4 High Pass filter, (a) 1st order and 2nd order HP filters Filter configuration in power system, (b) 1st HP filter, and (c) 2nd HP filter impedance-harmonic frequency relationship at different quality factors

This adjustment is represented by a term called the quality factor (Q) which is given by:

$$Q = \frac{\sqrt{L/C}}{Rd} \tag{2.2}$$

Figure 2.3b illustrates ST filter impedance, tuned at 150 Hz, as a function of the harmonic frequency at different quality factor. It is noticed that the sharpness of the filter is controlled by varying this factor as in (2.2).

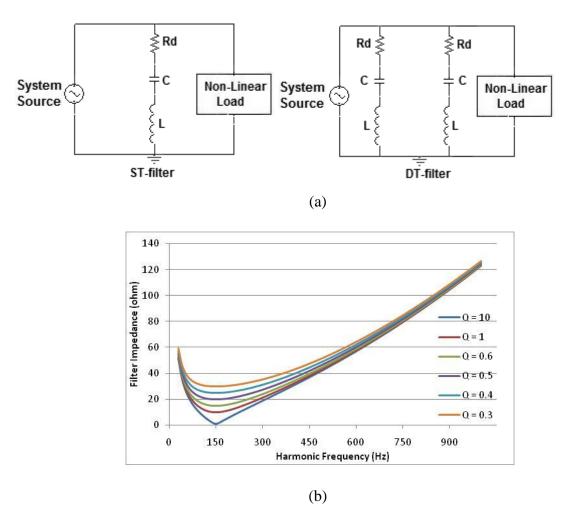

High pass filters are able to absorb a wide range of harmonic by providing a low impedance path at this range of high frequencies. The inserted damping resistor determines the sharpness of the tuning filter and its frequency response behaviour. For high pass filters, the quality factor is defined as follows [14]:

$$Q = \frac{Rd}{\sqrt{L/C}} \tag{2.3}$$

Figure 2.4a presents the first-order high-pass filter (1HP), which provides low impedance at high frequencies due to the capacitor characteristics. 1HP filter is basically composed of capacitor in series with a resistor. Due to the absence of an inductor, the quality factor does not apply, and the series resistance is chosen to limit the current that flows through the capacitor. Figure 2.4b shows 1HP impedance as a function of the harmonic frequency at various quality factors. In order to have low impedances at high frequencies, the capacitor size needs to be large. Inconsequence, this increases the cost and cause over reactive compensation of the system. For these reasons, this filter is not as much popularly used as are the other types of HP filters.

The second-order high pass filter (2HP), as shown in Figure 2.4a, consists of a capacitor in series with a parallel inductor and resistor. They are determined so that the filter acts like the ST filter at the tuning frequency and like the 1HP filter at high

frequencies. This is due to the small value of the inductive reactance at low frequencies bypassing the resistor in the parallel branch, and large value at high frequencies, allowing the current to flow in the resistor branch. At the tuning frequency, a notch valley is observed (Figure 2.4c) which is a result of tuning the capacitor with the inductor at the desired harmonic frequency as in (equation 2.1). Figure 2.4c shows the effect of varying the quality factor where the higher Q is, the closer the filter acts like ST filter. The 2HP filter is considered as the most popular high pass filter adopted in industrial systems [14].

The third order high pass filter (3HP), as shown in Figure 2.5a, presents high impedance, mainly capacitive, at the fundamental frequency and low impedance, predominantly resistive, over high frequencies [14]. The behaviour of this filter matches ST and 1HP filter at tuning frequency, and at higher frequencies, respectively as shown in Figure 2.5b. This is due to the small inductive reactance at low frequencies, bypassing resistor-capacitor branch, and high impedance at higher frequencies, where the current will pass through resistor-capacitor branch. Capacitors C<sub>1</sub> and C<sub>2</sub> are tuned with the inductor to the desired frequency, (equation 2.1) [22,23]. 3HP filter yields less loss at the fundamental frequency compared to 2HP filter because of the insertion of C<sub>2</sub> in series with the resistor [24]. Figure 2.5b shows the impact of varying the quality factor over the filter's impedance characteristic. It is clearly shown that the filter exhibits a resonant valley at the tuning frequency and a resonant peak at higher frequency value [22]. This is also due to the effect of tuning both capacitors to the same frequency with the inductor.

The harmonic filtering performance of the C-type filter, shown in Figure 2.5a, lies in between that of the 2HP and 3HP filters. The series inductor-capacitor branch in

Figure 2.5 High Pass filter, (a) 3rd order and C-Type HP filters Filter configuration in power system, (b) 3rd HP filter, and (c) C-Type HP filter impedance-harmonic frequency relationship at different quality factors

parallel with the resistor is tuned at the desired frequency, (equation.2.1). At the tuning frequency, the resistor branch is bypassed by the low impedance branch exhibited by the tuned inductor and capacitor elements. Thus the filter acts as a capacitor branch at the fundamental frequency where a little current flowing through the resistor and loss is minimized. The tuning of  $C_1$  and  $C_2$  with the inductor makes the filter behaves like ST filter. At higher frequencies, the inductor reactance becomes large. Inconsequence, the current will flow through the resistor branch which makes the filter perform similar to the 1HP filter as shown in Figure 5.4c [25].

The third type of shunt connected filters is the composite passive filter, as shown in Figure 2.6. This type is composed of a number of passive filters, previously conducted, in shunt with the non-linear load. A common type of composite filter includes several band pass filters and a branch of a high pass filter. Band pass filters are tuned individually to selected low frequency harmonics. The high pass filter branch is inserted to attenuate high frequency harmonics [26].

Figure 2.6 Composite passive filter: nth number of ST filter, and 2HP filter

### 2.2.2 Classification According to Parameters in the Circuit

Passive filters can be classified according to their element's parameters in the circuit. The operation of the filter is dependent on the parameters flexibility. In this section, passive filter is classified into fixed and variable filters. The latter type can be categorized as variable inductor, and variable capacitor as shown in Figure 2.7

Figure 2.7 Classification of passive filter configuration based on element's parameters in the circuit

Each type of this classification and related topologies is presented in the following subsections.

#### 2.2.2.1 Fixed Passive Filter

Passive power filters operate using fixed parameters (i.e. inductor, capacitor, and resistor), as presented in section 2.2.1, are classified as fixed filters. In this case, the filters do not respond to any change in the system. The filter performs the filtering action regardless any change in the frequency spectrum. All types of filters discussed earlier in this chapter are classified under this category.

#### 2.2.2.2 Variable Passive Filter

Variable passive filters components are varied in order to get different values of inductors and/or capacitors. Such design can be implemented in various topologies of passive filter by replacing the fixed tuned element and insert the variable element circuit.

Figure 2.8 Variable passive filter configurations, a: ST filter using TCR, and b: Proposed ST filter using SCC

Variable passive filters can be classified into two basic categories as follows:

- 1. Variable inductor (of Thyristor-controlled reactor as presented in literature [27,28]),

- 2. Variable capacitor (of Switched capacitor circuit as proposed in this thesis),

Variable inductor based passive filter, include a tuned capacitor and thyristor-controlled reactor (TCR) which act as a variable inductor. Figure 2.8a illustrates this method adopted by ST filter topology. In this technique, the inductor is connected in series with two thyristors back to back (T1 and T2). The thyristors are either in zero or full conduction [5]. The equivalent inductor reactance in this circuit can be varied by controlling the triggering angle of the thyristors. Although such technique can be effective in varying the inductance value, however the triggering of the thyristors, in either zero or full conduction, can cause the generation of huge amount of current harmonics. This is due to the intrinsic capability of the thyristor to switch at low frequency. Therefore, although the inductor value is controlled, the harmonic distortion flowing into the system is increased. This requires insertion of additional passive filter

in order to compensate the harmonics injected by the TCR. Inconsequence, this will increase number of components, and the cost of the system.

Variable capacitor based passive filter, include a tuned inductor and variable capacitance circuit called Switched Capacitor Circuit (SCC). This circuit is the main contribution in this thesis. Figure 2.8b illustrates this method adopted by ST filter topology. In this technique, the capacitor is connected in series with a fast semiconductor switch (i.e MOSFET, M2) where the series configuration is connected in parallel with a second switch (M1). This type of SCC is called Single Capacitor Double Switch (SCDS) circuit. The equivalent capacitor reactance in this circuit can be varied by controlling the duty-cycles of the switches. The switches can operate at relatively high switching frequency (up to 10 kHz). High switching frequency is preferred to enhance the spectral performance of the SCCs output which shows superiority on TCR circuit in terms of harmonic injection. Inconsequence, no need for additional filters for the line current which will decrease number of components and the cost of the system compared to TCR. This proposed filter is covered in details in Chapter 4.

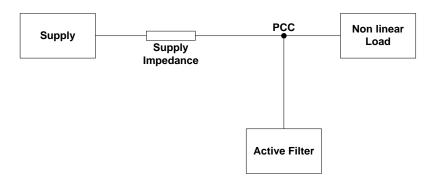

#### 2.2.3 Classification According to Point of Common Coupling

Passive filters can be classified according to their point of common coupling in the system. Filters can be inserted before harmonic sources (i.e. power electronic converters) in order to protect the system source from harmonics; this type of filters is called Input Filters. On the other hand, filters inserted after power converters are called Output filters. The place where filter is inserted is called Point of common coupling (PCC). Figure 2.9a shows a schematic of shunt input filter which provides harmonic protection for the supply system. Shunt filter placement, as shown in Figure 2.9b, protects the consumer's load from harmonic injection into the main line.

Figure 2.9 Passive Filter classification according to place of insertion, a: Shunt Input filter, and b: Shunt Output filter

All types of passive filter, previously conducted in this chapter, and other power electronic filters, active and hybrid filters conducted in the following sections, can be used as an input or output filters.

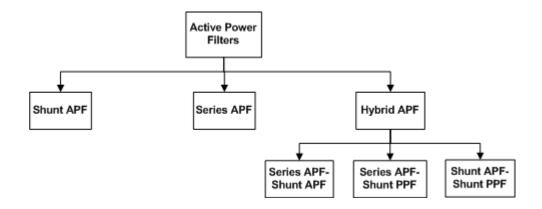

### 2.3 Overview of Active Power Filters

Active power filters were developed to provide better dynamic control of harmonic compensation. The developments in solid state switching devices and their control methods played a significant role in this area of harmonic filtering. Active power filters (APF) can be classified by types of converter used in their circuit and type of connection (i.e. Shunt or Series). APFs can be classified into shunt, series, and hybrid APFs as shown in the block diagram in Figure 2.10. Hybrid active power filters (HAPFs) are a combination of active and passive filters in order to combine the merit of each type as will be conducted in the following sections [5].

Figure 2.10 Classification of active power filters configurations

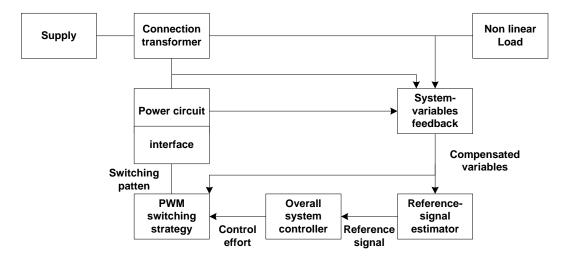

#### 2.3.1 Configurations of Active Power Filters

A typical APF configuration, including components and their interconnections, can be represented by the generalised block diagram as shown in Figure 2.11. The transmitted harmonic current in the main line, which is generated by the nonlinear load, is sensed and supplied to the reference current estimator. The reference signal from the current estimator drives the overall system controller which generates the control strategy for the PWM switching pattern. This pattern controls the power circuit through a suitable interface. The power circuit in the generalized block diagram can be connected in series or shunt as will be discussed in APFs classification [19].

Figure 2.11 Generalized block diagram for Active Power Filters

#### 2.3.1.1 Shunt Active Power Filters

Configurations of this type of APFs are considered as the most important and widely used type in industrial applications [19]. The main purpose of this type is to cancel out current harmonics generated by the non-linear load which are transmitted towards the supply. It is connected to the system as shown in the line diagram in Figure 2.12. Shunt configuration eliminate current harmonics by injecting equal but opposite harmonic current. This means that shunt APF operates as a current source injecting the harmonic components generated by the load but phase shifted by 180° [21]. Inconsequence, non-linear load harmonic currents flowing in the main line are cancelled by the effect of the APF, and the source current remains sinusoidal and free of undesired harmonics. The configuration of the shunt APF is shown in Figure 2.12 [19].

Shunt APFs are normally implemented with pulse width modulated-voltage source inverters (PWM-VSIs). This type of inverters operates as current controlled voltage source. Traditionally, two level PWM-VSI is aimed to compensate non-linear load harmonics rated in the medium power range (hundreds of kVA) due to semiconductors rated values limitations [21]. However, over the last years multilevel PWM-VSIs have been proposed for medium voltage and higher rated power applications. The use of multilevel VSI connected in cascade is considered as an alternative way to compensate high power non-linear loads harmonics.

Figure 2.12 Shunt active power filter configuration

Figure 2.13 Power circuit configurations of shunt APF VSI, a:Two-level VSI, and b: Multilevel VSI

The power circuit configurations of traditional VSI, and multilevel VSI are shown in Figure 2.13. VSIs will be presented and overviewed in the following chapter where it is adopted for the application of the new proposed filter in this thesis. The two-level VSI circuit is common in most shunt APFs either for single-phase [19,29] or three-phase [30-36] configurations. Multilevel VSI based for APF circuits are found in [37]. The main advantages of VSIs in general are the relatively simple control strategy needed for PWM wave shaping and the standard availability for power ratings that can cover the low and medium, using two-level VSI, and high power application regions,

using multilevel VSIs. However, the switching frequency of this harmonic compensation system is considered to be relatively high.

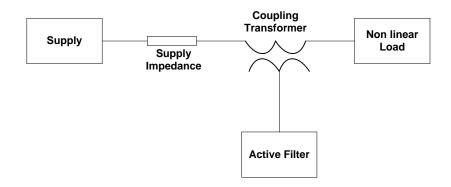

#### 2.3.1.2 Series Active Power Filters

Series APF produces a PWM voltage waveform, which is to be added/subtracted, on an instantaneous basis, to/from the supply voltage in order to apply a pure sinusoidal voltage waveform to the load [19]. Series APF is connected in series with the supply system. It prevents harmonic currents from flowing into the supply system or compensates the distortion in the load voltage as shown in Figure 2.14. This filter is controlled in a way so that it presents low and high impedance to fundamental and harmonic frequencies, respectively, at the PCC. This is applied in order to prevent harmonic currents from flowing into the system. It injects the needed voltage harmonic compensation at the PCC. The main aim of such type of active filters is not directly related to current harmonics compensation of the load, but to isolate these harmonics between the load and the supply source. A drawback to this type of APF is its full carriage of full load current which requires it to withstand high values of rated load current. Inconsequence, this increases the current rating, especially the secondary side of the coupling transformer (increase copper losses, and the physical size of the filter) [19]. In addition, this type is not able to directly eliminate current harmonics. Also, the load will lose the power supply if the filter's transformer experienced failure event [5]. Due to the abovementioned drawbacks, series APFs are less common industrially than shunt APFs.

Figure 2.14 Series active power filter configuration

The main advantage of series filters over shunt ones is that they can be used easier for voltage harmonic compensation [19] which dedicates this type to the benefit of the loads. It supplies the load with a pure sinusoidal voltage waveform which is vital for voltage sensitive devices. Circuit configuration of the shunt active filters, in the previous section, can be reused for series APF where only two-level VSI is reported in the literature [19].

#### 2.3.1.3 Hybrid Active Power Filters

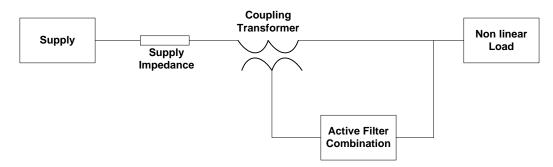

Some combinations of the previous presented APFs and/or passive filters can achieve more benefits to the filtering operation, as shown in Figure 2.11. These can be classified as follows:

#### 2.3.1.3.1 Series / Shunt Active Power Filters

This combination aims to gain the merits of series and shunt APFs configurations as shown in Figure 2.15. This can be achieved by controlling both filter topologies to get the desired performance of harmonic elimination. A special control algorithm must be developed for the control of both filters in order to get the maximum compensation performance of both filters.

Figure 2.15 Series / Shunt active power filter configuration

This hybrid APF topology has received less attention compared to other APF configuration due to the control complexity, the dependency of the switching pattern of both filter circuits, and consequently higher cost [38-40]. According to literature [38], this topology is used in power system FACTs research studies.

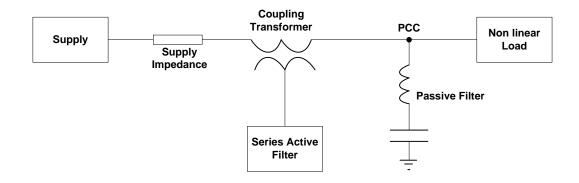

#### 2.3.1.3.2 Series Active / Shunt Passive Power Filters

This type does not suffer from complexity compared to the latter filter. It is composed of the series APF, which provides a high impedance for harmonic frequencies, and a shunt passive filter, which provides a low impedance path for the harmonic currents of the load [40,41]. This hybrid filter extend the capabilities of the traditional series APF to reduce current harmonics as well as voltage harmonics [40,41]. This topology has not been studied thoroughly in literature due to the lack of interest in series APF, and the huge concentration on shunt APFs topologies. Figure 2.16 illustrates the configuration of series active/ shunt passive power filter.

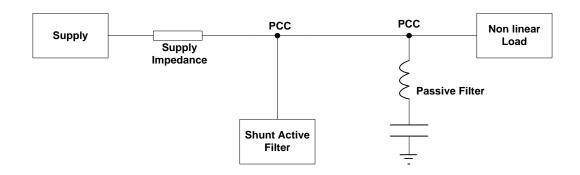

#### 2.3.1.3.3 Shunt Active / Shunt Passive Power Filters

The integration of shunt active and shunt passive power filters represents a very important hybrid topology as shown in Figure 2.17. This combination shows a mixture of the most common configurations used in industrial applications, in both active and

Figure 2.16 Series active / Shunt passive power filter configuration

passive filtering technologies. The active filter part is responsible of low order current harmonics while the passive part is designed for the rest load current harmonics [19,42]. The main drawback of this method and the latter hybrid topologies are high number of components due to the presence of two filters, passive and active circuits, from the point of view of size and cost.

Figure 2.17 Shunt active / Shunt passive power filter configuration

#### 2.4 General Comparison of Power Electronic Filters

It is noticed from the previous review of power electronic filters, the expansion of the use of power electronic circuits in order to eliminate harmonics which is generated mainly from switching converters. This can lead to the fact that the source of the harmonic problem can be solved using the power electronic circuit itself in the case of active filters. Although active filters, including hybrid configurations, have many

Table 2-1 Comparison of Common Power Electronic Filters

| Power Filter             | Туре        | Main Components | Merit                                  | Drawback                           |  |

|--------------------------|-------------|-----------------|----------------------------------------|------------------------------------|--|

|                          | Series PPF  | -Inductor       | -Low cost                              | -Full load current carriage        |  |

|                          |             | -Resistor       | -Low component number                  |                                    |  |

|                          |             |                 | -Low impedance path at tuned frequency | -Filters one/two harmonics only    |  |

| Passive                  | Shunt Tuned |                 | -Harmonic load current carriage        | -Require multiple filters for high |  |

| Filter                   | PPF         | -Inductors      |                                        | harmonic number                    |  |

|                          |             | -Capacitors     | -Low impedance path for high range of  | -Does not achieve as low as tuned  |  |

| Shunt High Pass -Resisto |             | -Resistors      | frequencies                            | filter impedance                   |  |

|                          | PPF         |                 | -One filter is enough for the harmonic | -High number of components some    |  |

|                          |             |                 | range                                  | types in this category             |  |

|                          |             |                 | -Dedicated to voltage sensitive loads  | -Full load current carriage        |  |

|                          | Series APF  |                 | (voltage harmonic elimination)         | -Large physical size and cost      |  |

| Active                   |             |                 |                                        | -Disruption of supply when         |  |

| Filter                   |             | -Semiconductor  |                                        | transformer failure occur          |  |

|                          |             | Switches        | -Current harmonics compensation        | -High switching frequency          |  |

|                          | Shunt APF   |                 | -Simple control                        | -High component number in          |  |

|                          |             |                 | -Standard availability of VSI          | multilevel VSI based APF           |  |

|                         | Shint DDE |  | -Voltage and Current harmonic elimination                                                                                                                            | -Complex control -High number of switches -High switching losses |  |

|-------------------------|-----------|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| Hybrid<br>Active Filter |           |  | -Extend the capabilities of APF to reduce current harmonics -Simpler control compared to Series APF-Shunt APF -Lower switching losses due to the presence of one APF | - The intrinsic drawbacks of Series APF                          |  |

| Shunt APF-<br>Shunt PPF |           |  | -Simple control due to the presence of shunt APF -Carriage of a portion of the load current                                                                          | -High number of components                                       |  |

promising advantages, passive filters still have their unique features and merits as well. A comparison of the above discussed topologies, including passive and active filters, showing the merits and drawbacks together with its component level contents is presented in Table 2-1. However, the selection of the proper power electronic filter for a certain application which depends on many factors the designer has to compromise between them, such as; harmonics to be compensated (voltage and/or current), size and volume, economic considerations, packaging requirements, switching frequency's range and whether the filter is used as an input or output filter. From the literature review and the above comparison between different topologies of power electronic filters, it has been shown that passive filters are superior in the point of view of ease in implementation, simple design, and low cost, especially single tuned filter which is the most common filter used in many applications. Therefore, this filter will be used after modification to implement the new passive filter topology aimed from this research. The proposed filter topology is an output filter for power inverters applications.

#### 2.5 Summary

The subdivisions outlined in this chapter present a quick, yet a relevant review of power electronic filters technology presented in the surveyed published literature. It constitutes classification of passive and active filters used in electric power application. This subdivision is very useful from the point of view of recognising the merits and drawbacks of each type and configuration of power electronic filters. These points will lead to the definition of the new filter topology adopted in this research which is designed for power inverters applications. Therefore, it is important to introduce and discuss these inverters in the next chapter before presenting the new topology in chapter 4.

# Chapter 3

# Investigation of Power Electronic Voltage Source H-Bridge Inverters

#### 3.1 Introduction

Power electronic converters which transform DC voltages to sinusoidal AC voltages are known as inverters. The main function of inverters is the generation of an AC output waveform with controllable amplitude, phase, and frequency for desired applications. The conversion is achieved by the suitable control of semiconductor switches, where this is called modulation. These switches interconnect the DC source to the AC load with different arrangements. The DC sources can be either energy storage components, such as batteries, or a rectifier (AC-DC converter). The main aim of using different types of modulation is to provide an output waveform with minimum undesired harmonics. In this thesis, inverters will be the main source of harmonics at which the proposed filter is tested. This chapter describes the most common H-bridge VSIs topologies and its modulation techniques found in industry. Special attention is given to low frequency, square wave, and high frequency, PWM, for both traditional and multilevel configurations.

### 3.2 Voltage Source H-bridge Inverters

VSIs are the most common power conversion systems in many power applications [5] such as uninterruptable power supplies (UPS), domestic appliances (washing machines, air conditioning, etc.), photovoltaic power conversion, adjustable speed drives, and active power filters. The inverter output current is defined by the load,

Figure 3.1 Classification of H-bridge voltage source inverters

which is required to have high spectral performance according to the need of the application [34]. This can be achieved by developing modulation schemes; otherwise output filters are used [5]. The following sections present the operating principles and concepts related to VSIs topologies and its corresponding control schemes. Figure 3.1 shows the classification of H-bridge VSI and its subdivision according to their modulation techniques.

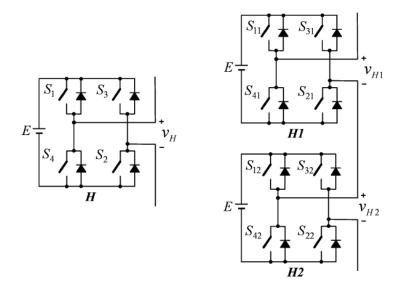

#### 3.2.1 Traditional H-bridge VSI

The popular H-bridge VSI is composed of four semiconductor switches, two switches for each leg. A single phase topology is illustrated in Figure 3.2. Each leg has its own switching control pattern, where 1 represents the switching during the conduction period (On-state), and 0 represents the disconnection period (Off-state) [5,43]. Four different switching states are defined by  $S_a$  and  $S_b$  as shown in Figure 3.3 illustrating the active parts of the circuits in each state [5]. For instance, the amplitude of output voltage  $v_{ab}$ , equals to the amplitude of  $V_{dc}$ .

Figure 3.2 Single Phase H-bridge voltage source inverters

Figure 3.3 H-bridge inverter switching states: (a) vab = Vdc, (b) vab = 0, (c) vab = -Vdc, and (d) vab = 0.

Table 3-1 H-bridge VSI Switching States

| Switching State | Gate Signal, Sa | Gate Signal, S <sub>b</sub> | Output Voltage, v <sub>ab</sub> |  |

|-----------------|-----------------|-----------------------------|---------------------------------|--|

| (a)             | 1               | 0                           | $V_{ m dc}$                     |  |

| (b)             | 0               | 0                           | 0                               |  |

| (c)             | 0               | 1                           | -V <sub>dc</sub>                |  |

| (d)             | 0               | 0                           | 0                               |  |

The operation of generating different voltage levels can be expressed generally as follows [5]:

$$v_{ab} = (S_a - S_b)V_{dc} (3.1)$$

where  $S_a$  and  $S_b$  equals to either 1 or 0. Gate signals switching states for each switch is shown in Table 3-1 [5]. Therefore, by replacing gate signals combination, different output voltage levels are obtained. Hence, three output voltage levels can be generated as  $\{V_{dc}, 0, -V_{dc}\}$ .

Transistor-based inverter topology is used for low voltage applications due to the limitation of the implemented semiconductor technology. Nevertheless, high voltage thyristor-based inverters can make this topology suitable for higher power applications. However, due to the limitation of using low switching frequency in thyristor-based inverters, filters are needed in order to control the output harmonics for many applications such as a.c. motors [5,44]. This problem can be solved using multilevel VSI, where H-bridge inverter topology is considered as its main building block as will be discussed later in this chapter. The multilevel topology produces more voltage levels hence reducing harmonics and therefore could be used in upgrading existing inverters to higher voltage applications [5].

#### 3.2.2 Common Modulation Methods for Traditional H-bridge VSI

As conducted earlier, VSI inverters are required to provide sinusoidal output waveforms, free of undesired harmonics. This can be implemented by inserting an output filter in order to eliminate harmonics, from the square waveform which is rich in harmonics, or by modulating and controlling the semiconductor switches as will be presented in the following subsections. This process is called modulation; where there are various methods proposed and applied in industry [5,45]. Each method has its unique operating principles, implementation, and performance. This section presents the most common modulation methods for traditional VSI.

#### **3.2.2.1** Low Frequency Square Wave Modulation

The square-wave modulation is the most basic and easy to implement for H-bridge VSIs [5,45]. This scheme generates a square output waveform with the desired frequency. Figure 3.3 illustrates the output voltage waveform using this modulation method. The operation of this modulation has been discussed in the previous section, showing switching states and the output voltage. This method suffers from low power quality output which is at the expense of the ease of implementation. Therefore, large size filters have to be inserted or another modulation technique can be used as will be conducted in the following section.

#### 3.2.2.2 High Frequency Sinusoidal PWM Modulation

This type of modulation is classified under high frequency carrier based schemes where it is called Sinusoidal PWM (SPWM). It is considered as the most widely used technique in power inverters applications [5,45]. SPWM is well known in its good power quality output. However, it operates under high switching frequency which introduces high switching losses. On the other hand, if the switching frequency is low as

seen in square wave modulation, the size, volume, and economical cost of the output filters increase. In this case, a trade off between switching losses, and filter design cost has to be investigated. The basic idea behind SPWM is by generating a chopped square waveform. This can be achieved by controlling the width of the switching pulses which is also called the duty cycle [45]. The process is achievable by comparing a reference signal, sinusoidal wave, with a carrier signal, triangular wave, where the intersection between both signals produces the desired output waveform. Multicarrier SPWM strategies can be used for multilevel VSIs as will be discussed later in this chapter.

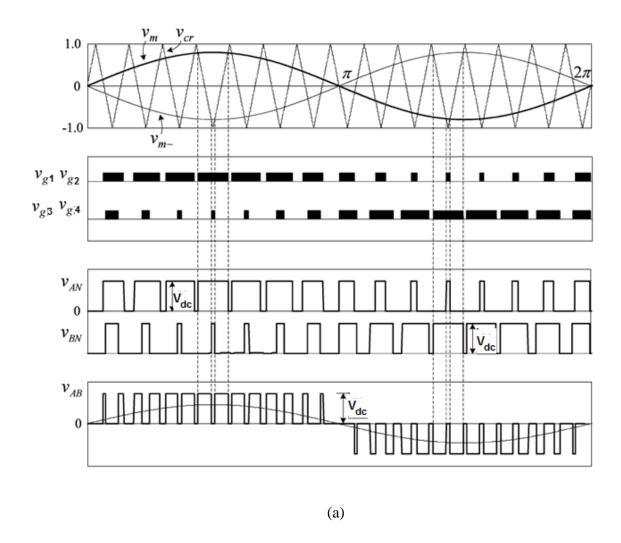

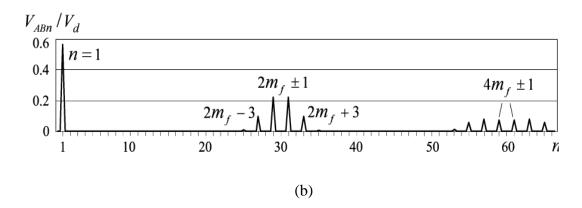

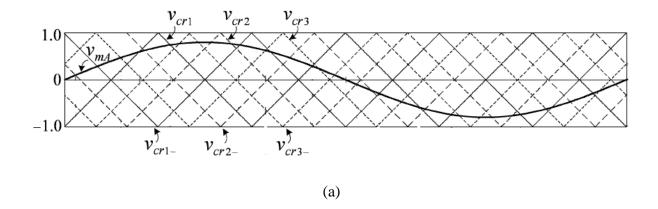

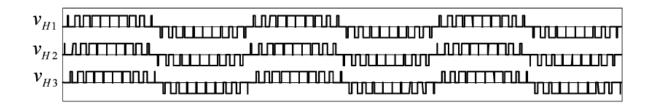

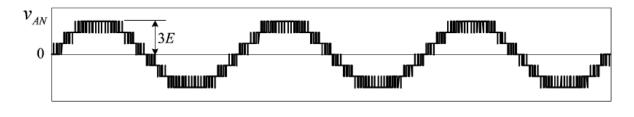

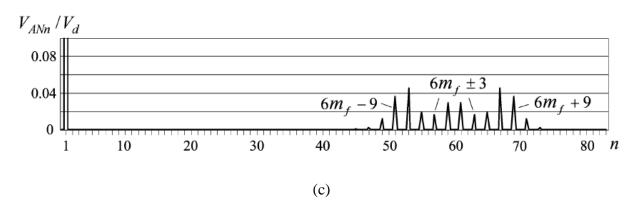

The most common SPWM modulation techniques can be classified as bipolar, and unipolar PWM methods [45]. Figure 3.4a illustrates a typical waveforms of Hbridge VSI modulated by bipolar scheme, where v<sub>m</sub> is the sinusoidal modulating signal,  $v_{cr}$  is the triangular carrier signal, and  $v_{g1}$  and  $v_{g3}$  are the gate pulses for switches  $S_a$  and S<sub>b</sub>, respectively as shown in Figure 3.2 [46]. The upper and lower in each inverter leg behaves in anti-parallel manor where one switch is on and the other is off. Therefore, two independent switch's gate signals are considered in the operating principle explanation,  $v_{g1}$  and  $v_{g3}$ . These gate signals are a result of the intersection between  $v_m$ and v<sub>cr</sub>. According to Figure 3.4a, the inverter output voltage, v<sub>ab</sub>, can be found from the inverter terminal output voltages van and vbn. Since, the output voltage waveform vab switches between the positive and negative dc voltages, this scheme has derived its name as bipolar SPWM [46]. Figure 3.4b [46] shows the harmonic spectrum of the inverter output voltage using bipolar SPWM scheme, where vab is normalized to its dc voltage  $V_{dc}$ .  $v_{abn}$  is the rms value of the  $n^{th}$  order harmonic voltage. The spectral performance shows that harmonics appear as sidebands centred around the frequency modulation index  $m_f$  and its multiples such as  $2m_f$  and  $3m_f$ , where this index is the relation between the modulating voltage frequency  $v_{\text{m}}$ , and the carrier frequency  $v_{\text{cr}}$ .

Figure 3.4 Bipolar SPWM for H-bridge voltage source inverter  $m_{\rm f}=15$ , (a) waveforms, (b) harmonic spectrum

The switching frequency of the semiconductor switches is equal to the carrier frequency. The second SPWM modulation technique is the unipolar scheme. This type normally requires two sinusoidal modulating signals, v<sub>m</sub> and v<sub>m</sub>-, where they have the same magnitude but opposite in phase as shown in Figure 3.5a. Both signals are compared with one triangular carrier signal v<sub>cr</sub>, which generates two gate signals, v<sub>g1</sub> and v<sub>g3</sub>, for switches S<sub>a</sub> and S<sub>b</sub>, respectively. In this case, the inverter output voltage switches between zero and  $+V_{\text{dc}}$  in the positive half cycle and between zero and  $-V_{\text{dc}}$  in the negative half cycle of the fundamental frequency. Therefore, this method is known as unipolar SPWM [46]. Figure 3.5b illustrates the harmonic spectrum of the inverter output voltage v<sub>ab</sub>, which shows the harmonics as sidebands centred around 2m<sub>f</sub> and 4m<sub>f</sub> [46]. The low order harmonics, seen around m<sub>f</sub> in bipolar SPWM, are eliminated in this scheme. The dominant harmonics are seen around 2mf and their sideband frequencies. This is actually the equivalent inverter switching frequency, which is also observed by the load [46]. Although, the switching frequency of the inverter in both modulation schemes, bipolar and unipolar, are the same, the dominant harmonics changed its location and are shifted higher in the spectrum in the unipolar case. This is due to the fact that switches S<sub>a</sub> and S<sub>b</sub> do not switch simultaneously, where they switch at different time instances, leading to doubling the inverter switching frequency. This phenomenon distinguishes the bipolar scheme from unipolar where all four switches are operating during each half cycle of the output waveform. An alternative way to implement unipolar SPWM is by using one modulating signal and two phase shifted carriers [46].

Figure 3.5 Unipolar SPWM for H-bridge voltage source inverter, (a) waveforms, (b) harmonic spectrum

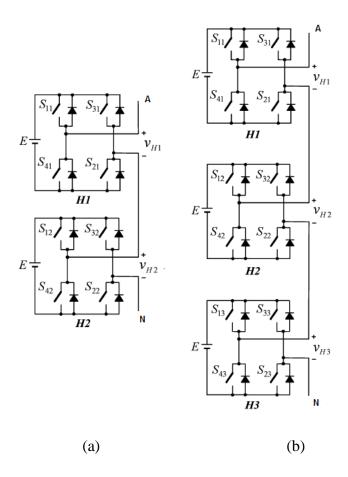

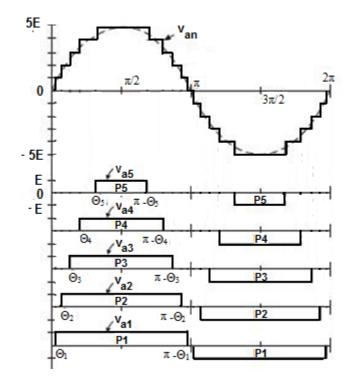

#### 3.2.3 Multilevel Cascaded H-bridge VSI