# Automotive embedded systems software reprogramming

A thesis submitted for the degree

of Doctor of

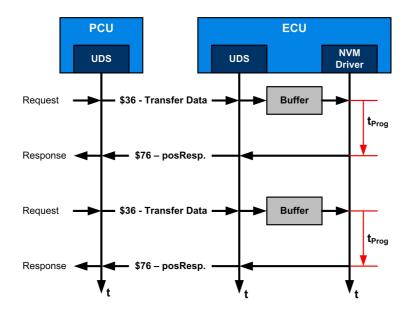

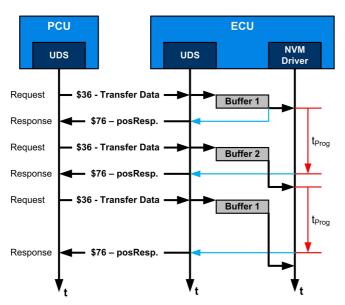

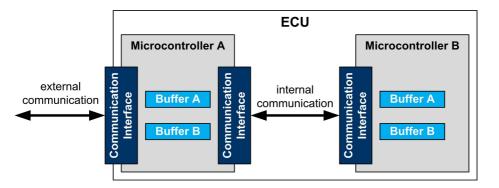

Philosophy

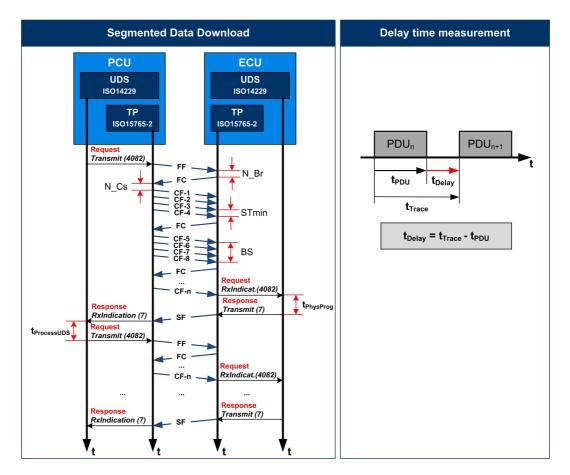

by

Ralf Schmidgall

School of Engineering and Design

**Brunel University**

May 2012

# Abstract

The exponential growth of computer power is no longer limited to stand alone computing systems but applies to all areas of commercial embedded computing systems. The ongoing rapid growth in intelligent embedded systems is visible in the commercial automotive area, where a modern car today implements up to 80 different electronic control units (ECUs) and their total memory size has been increased to several hundreds of megabyte.

This growth in the commercial mass production world has led to new challenges, even within the automotive industry but also in other business areas where cost pressure is high. The need to drive cost down means that every cent spent on recurring engineering costs needs to be justified. A conflict between functional requirements (functionality, system reliability, production and manufacturing aspects etc.), testing and maintainability aspects is given.

Software reprogramming, as a key issue within the automotive industry, solve that given conflict partly in the past. Software Reprogramming for in-field service and maintenance in the after sales markets provides a strong method to fix previously not identified software errors. But the increasing software sizes and therefore the increasing software reprogramming times will reduce the benefits. Especially if ECU's software size growth faster than vehicle's onboard infrastructure can be adjusted.

The thesis result enables cost prediction of embedded systems' software reprogramming by generating an effective and reliable model for reprogramming time for different existing and new technologies. This model and additional research results contribute to a timeline for short term, mid term and long term solutions which will solve the currently given problems as well as future challenges, especially for the automotive industry but also for all other business areas where cost pressure is high and software reprogramming is a key issue during products life cycle.

# Content

| 1 | Intr | oducti  | ion                                            | 1  |

|---|------|---------|------------------------------------------------|----|

|   | 1.1  | Vehicl  | e's life cycle                                 | 2  |

|   | 1.2  | Repro   | gramming within an ECU's life cycle            | 4  |

|   | 1.3  | Aspec   | ts of software reprogramming                   | 7  |

|   |      | 1.3.1   | Automotive innovation vs. software size        | 8  |

|   |      | 1.3.2   | Automotive development focus and priority      | 9  |

|   |      | 1.3.3   | Automotive system complexity and compatibility | 10 |

|   |      | 1.3.4   | Automotive network aspects                     | 12 |

|   |      | 1.3.5   | Summary                                        | 14 |

|   | 1.4  | Scope   | of the thesis                                  | 15 |

|   | 1.5  | Organ   | isation of the thesis                          | 16 |

| 2 | Bad  | ckgrou  | ınd                                            | 18 |

|   | 2.1  | Embeo   | dded Systems                                   | 19 |

|   | 2.2  | Electro | onic Control Unit                              | 21 |

|   |      | 2.2.1   | Microcontroller                                | 21 |

|   |      | 2.2.2   | Memory                                         | 22 |

|   |      | 2.2.3   | ECU Software Components Overview               | 24 |

|   | 2.3  | Progra  | amming Control Unit (Test system)              | 28 |

|   | 2.4  | Progra  | amming Sequence                                | 29 |

|   | 2.5  | Comm    | unication Stack                                | 33 |

|   |      | 2.5.1   | Field bus systems                              | 35 |

|   |      | 2.5.2   | Media Access Control Overview                  | 36 |

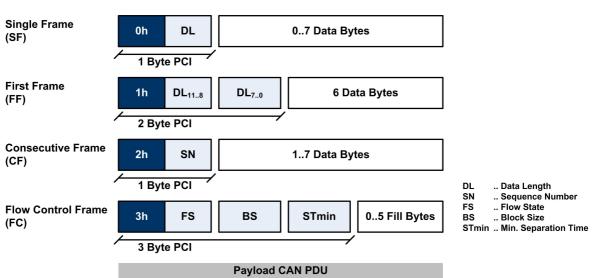

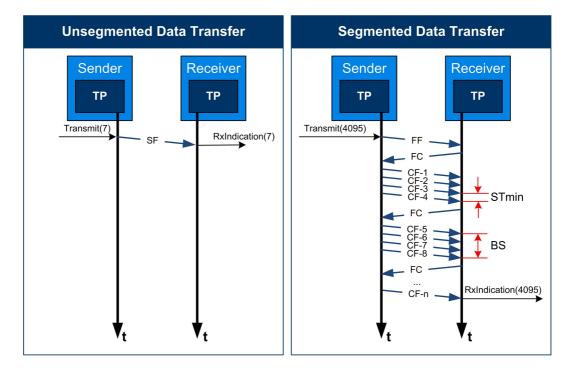

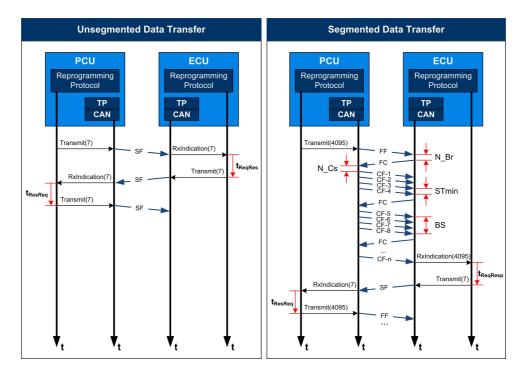

|   |      | 2.5.3   | Transport Layer Protocol                       | 36 |

|   |      | 2.5.4   | Application Protocols                          | 38 |

|   | 2.6  | Netwo   | rk                                             | 39 |

|   | 2.7  | Summ    | ary                                            | 40 |

| 3 | Do   | uble bi | uffered data transfer                          | 41 |

|   | 3.1  | Repro   | gramming Protocol                              | 42 |

|   | 3.2  |         | e buffered data transfer                       |    |

|   | 3.3  | Metho   | d's utilisation                                | 49 |

|   |      | 3.3.1   | Mapping to Diagnostic Protocol ISO-14229 – UDS | 49 |

|   |     | 3.3.2   | Mapping to other application protocols      | 51  |

|---|-----|---------|---------------------------------------------|-----|

|   |     | 3.3.3   | Mapping to multi controller systems         | 51  |

|   | 3.4 | Concl   | usion                                       | 52  |

| 4 | Fie | ld bus  | system protocol stacks                      | 53  |

|   | 4.1 | Contro  | oller Area Network                          | 54  |

|   |     | 4.1.1   | CAN bus protocol according to ISO 11989     | 54  |

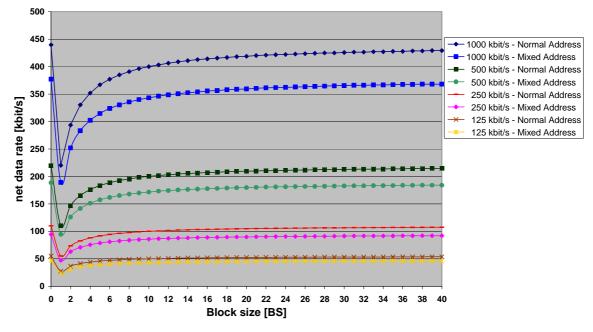

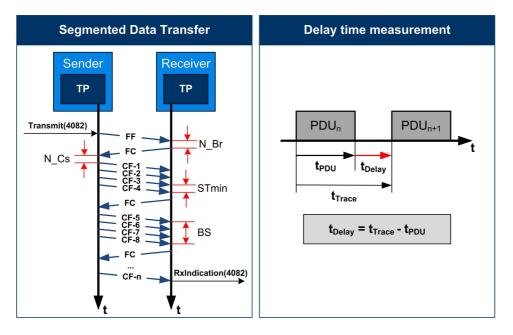

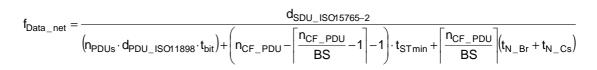

|   |     | 4.1.2   | CAN-TP according to ISO 15765-2             |     |

|   |     | 4.1.3   | Complete reprogramming process based on UDS | 70  |

|   |     | 4.1.4   | Conclusion                                  | 71  |

|   | 4.2 | FlexRa  | ay                                          | 73  |

|   |     | 4.2.1   | FlexRay (FlexRay Specification 2.1)         | 73  |

|   |     | 4.2.2   | FlexRay Transport Protocol (ISO 10681-2)    | 84  |

|   |     | 4.2.3   | Complete reprogramming process based on UDS | 91  |

|   |     | 4.2.4   | Conclusion                                  | 93  |

|   | 4.3 | Summ    | nary                                        | 94  |

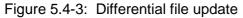

| 5 | Dat | a size  | reduction                                   | 96  |

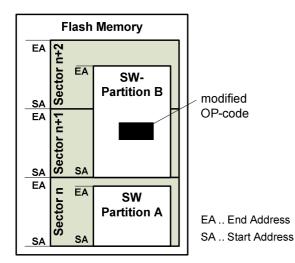

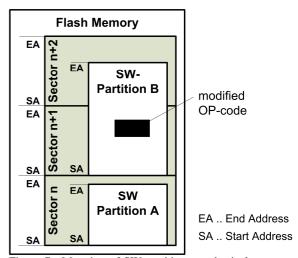

|   | 5.1 | Partiti | oning                                       | 97  |

|   |     | 5.1.1   | Analysis                                    | 97  |

|   |     | 5.1.2   | Discussion                                  |     |

|   | 5.2 | Fill by | te skipping                                 | 99  |

|   |     | 5.2.1   | Analysis                                    | 99  |

|   |     | 5.2.2   | Discussion                                  | 100 |

|   | 5.3 | Data c  | compression                                 | 103 |

|   |     | 5.3.1   | Analysis                                    | 103 |

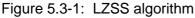

|   |     | 5.3.2   | LZ77 and LZSS Algorithm                     | 104 |

|   |     | 5.3.3   | Discussion                                  |     |

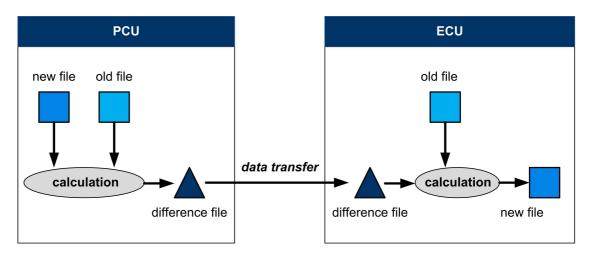

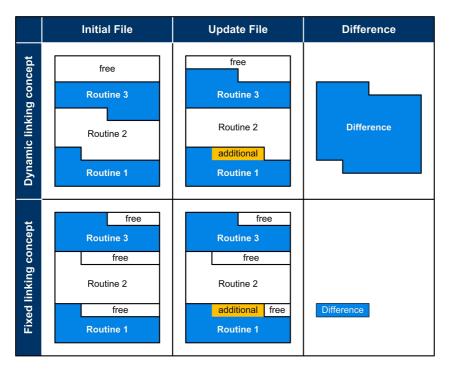

|   | 5.4 | Differe | ential file                                 | 107 |

|   |     | 5.4.1   | Analysis                                    |     |

|   |     | 5.4.2   | Discussion                                  | 111 |

|   | 5.5 | Concl   | usion                                       | 112 |

| 6 | Mic | rocon   | troller Hardware Optimisation               | 116 |

|   | 6.1 | Memo    | ry status information                       | 116 |

|   |     | 6.1.1   | Analysis                                    |     |

|   |                                                             | 6.1.2                                                                                                                    | Discussion                                                                                                                                                                                                         | 119                                                                                            |

|---|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   | 6.2                                                         | Doubli                                                                                                                   | ng interrupt vector tables                                                                                                                                                                                         | 121                                                                                            |

|   |                                                             | 6.2.1                                                                                                                    | Analysis                                                                                                                                                                                                           | 121                                                                                            |

|   |                                                             | 6.2.2                                                                                                                    | Discussion                                                                                                                                                                                                         | 122                                                                                            |

|   | 6.3                                                         | Conclu                                                                                                                   | usion                                                                                                                                                                                                              | 123                                                                                            |

| 7 | Net                                                         | work a                                                                                                                   | architecture                                                                                                                                                                                                       | 125                                                                                            |

|   | 7.1                                                         | Introdu                                                                                                                  | uction                                                                                                                                                                                                             | 127                                                                                            |

|   |                                                             | 7.1.1                                                                                                                    | Networking issues                                                                                                                                                                                                  | 127                                                                                            |

|   |                                                             | 7.1.2                                                                                                                    | Network types                                                                                                                                                                                                      | 128                                                                                            |

|   | 7.2                                                         | Routin                                                                                                                   | g nodes (Gateways)                                                                                                                                                                                                 | 129                                                                                            |

|   | 7.3                                                         | Routin                                                                                                                   | g strategy                                                                                                                                                                                                         | 130                                                                                            |

|   |                                                             | 7.3.1                                                                                                                    | Analysis                                                                                                                                                                                                           | 130                                                                                            |

|   |                                                             | 7.3.2                                                                                                                    | Discussion                                                                                                                                                                                                         | 131                                                                                            |

|   | 7.4                                                         | Conclu                                                                                                                   | usion                                                                                                                                                                                                              | 135                                                                                            |

|   |                                                             | 7.4.1                                                                                                                    | Routing strategy                                                                                                                                                                                                   | 135                                                                                            |

|   |                                                             | 7.4.2                                                                                                                    | Network design                                                                                                                                                                                                     | 136                                                                                            |

|   |                                                             | 7.4.3                                                                                                                    | Summary                                                                                                                                                                                                            | 139                                                                                            |

|   |                                                             |                                                                                                                          |                                                                                                                                                                                                                    |                                                                                                |

| 8 | Rep                                                         | orogra                                                                                                                   | mming in parallel                                                                                                                                                                                                  | 141                                                                                            |

| 8 | Rep<br>8.1                                                  | •                                                                                                                        | mming in parallel                                                                                                                                                                                                  |                                                                                                |

| 8 | -                                                           | Introdu                                                                                                                  | •                                                                                                                                                                                                                  | 142                                                                                            |

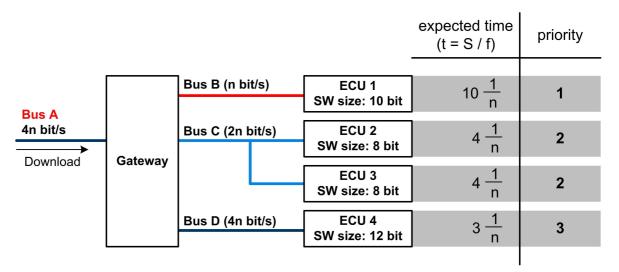

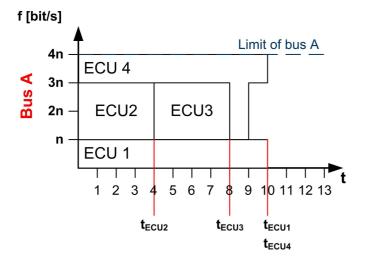

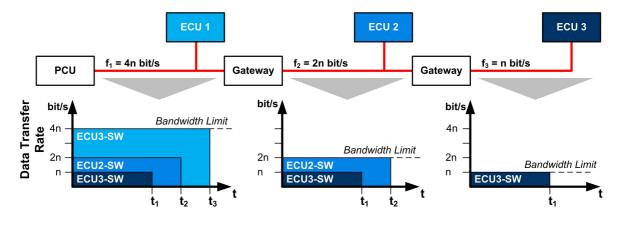

| 8 | 8.1                                                         | Introdu<br>ECU se                                                                                                        | uction                                                                                                                                                                                                             | 142<br>143                                                                                     |

| 8 | 8.1<br>8.2<br>8.3                                           | Introdu<br>ECU se<br>Discus                                                                                              | uction<br>chedule calculation                                                                                                                                                                                      | 142<br>143<br>147                                                                              |

| 8 | 8.1<br>8.2<br>8.3<br>8.4                                    | Introdu<br>ECU se<br>Discus<br>Conclu                                                                                    | uction<br>chedule calculation<br>ssion                                                                                                                                                                             | 142<br>143<br>147<br>149                                                                       |

|   | 8.1<br>8.2<br>8.3<br>8.4                                    | Introdu<br>ECU se<br>Discus<br>Conclu                                                                                    | uction<br>chedule calculation                                                                                                                                                                                      | 142<br>143<br>147<br>149<br>151                                                                |

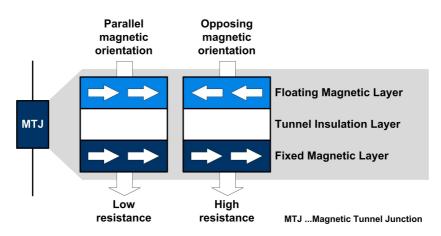

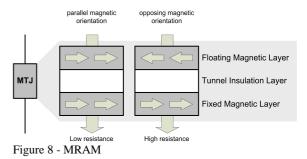

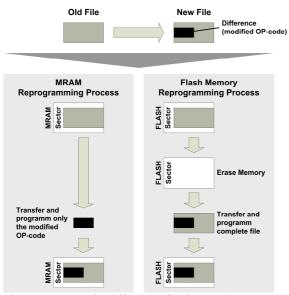

|   | 8.1<br>8.2<br>8.3<br>8.4<br>Mag                             | Introdu<br>ECU se<br>Discus<br>Conclu<br>gnetore<br>Introdu                                                              | uction<br>chedule calculation<br>ssion<br>usion<br>esistive RAM                                                                                                                                                    | 142<br>143<br>147<br>149<br>151<br>152                                                         |

|   | 8.1<br>8.2<br>8.3<br>8.4<br>Mag<br>9.1<br>9.2               | Introdu<br>ECU so<br>Discus<br>Conclu<br>gnetoro<br>Introdu<br>Discus                                                    | uction<br>chedule calculation<br>ssion<br>usion<br>esistive RAM<br>uction                                                                                                                                          | 142<br>143<br>147<br>149<br>151<br>152<br>153                                                  |

|   | 8.1<br>8.2<br>8.3<br>8.4<br>Mag<br>9.1<br>9.2<br>9.3        | Introdu<br>ECU so<br>Discus<br>Conclu<br>gnetoro<br>Introdu<br>Discus<br>Case s                                          | uction<br>chedule calculation<br>ssion<br>usion<br>esistive RAM<br>uction<br>ssion<br>ssion<br>study to the differential file approach                                                                             | 142<br>143<br>147<br>149<br>151<br>152<br>153<br>154                                           |

| 9 | 8.1<br>8.2<br>8.3<br>8.4<br>Mag<br>9.1<br>9.2<br>9.3<br>9.4 | Introdu<br>ECU so<br>Discus<br>Conclu<br>gnetoro<br>Introdu<br>Discus<br>Case s<br>Conclu                                | uction<br>chedule calculation<br>ssion<br>usion<br>esistive RAM<br>uction<br>ssion<br>study to the differential file approach<br>usion                                                                             | 142<br>143<br>147<br>149<br>151<br>152<br>153<br>154<br>156                                    |

| 9 | 8.1<br>8.2<br>8.3<br>8.4<br>Mag<br>9.1<br>9.2<br>9.3<br>9.4 | Introdu<br>ECU so<br>Discus<br>Conclu<br>gnetoro<br>Introdu<br>Discus<br>Case s<br>Conclu                                | uction<br>chedule calculation<br>ssion<br>usion<br>esistive RAM<br>uction<br>ssion<br>ssion<br>study to the differential file approach                                                                             | 142<br>143<br>147<br>149<br>151<br>152<br>153<br>154<br>156                                    |

| 9 | 8.1<br>8.2<br>8.3<br>8.4<br>9.1<br>9.2<br>9.3<br>9.4<br>Cas | Introdu<br>ECU se<br>Discus<br>Conclu<br>gnetore<br>Introdu<br>Discus<br>Case s<br>Conclu                                | uction<br>chedule calculation<br>ssion<br>usion<br>esistive RAM<br>uction<br>ssion<br>study to the differential file approach<br>usion                                                                             | 142<br>143<br>147<br>149<br>151<br>152<br>153<br>154<br>156<br>157                             |

| 9 | 8.1<br>8.2<br>8.3<br>8.4<br>9.1<br>9.2<br>9.3<br>9.4<br>Cas | Introdu<br>ECU se<br>Discus<br>Conclu<br>gnetore<br>Introdu<br>Discus<br>Case s<br>Conclu                                | uction<br>chedule calculation<br>ssion<br>usion<br>esistive RAM<br>uction<br>ssion<br>study to the differential file approach<br>usion<br>by – Software reprogramming                                              | 142<br>143<br>147<br>149<br>151<br>152<br>153<br>154<br>156<br>157<br>157                      |

| 9 | 8.1<br>8.2<br>8.3<br>8.4<br>9.1<br>9.2<br>9.3<br>9.4<br>Cas | Introdu<br>ECU se<br>Discus<br>Conclu<br>gnetore<br>Introdu<br>Discus<br>Case s<br>Conclu<br>Se stuc                     | uction<br>chedule calculation<br>ssion<br>usion<br>esistive RAM<br>esistive RAM<br>uction<br>ssion<br>study to the differential file approach<br>usion<br>by – Software reprogramming<br>are reprogramming via CAN | 142<br>143<br>147<br>147<br>151<br>151<br>152<br>153<br>154<br>156<br>157<br>157<br>158        |

| 9 | 8.1<br>8.2<br>8.3<br>8.4<br>9.1<br>9.2<br>9.3<br>9.4<br>Cas | Introdu<br>ECU so<br>Discus<br>Conclu<br>gnetoro<br>Introdu<br>Discus<br>Case s<br>Conclu<br>Se stuc<br>Softwa<br>10.1.1 | uction   chedule calculation   assion   usion   esistive RAM                                                                                                                                                       | 142<br>143<br>147<br>147<br>149<br>151<br>152<br>153<br>154<br>156<br>157<br>157<br>158<br>158 |

|    | 10.1.5      | ISO 15765-2 (CAN TP) FlowControl parameter STmin         | 170 |

|----|-------------|----------------------------------------------------------|-----|

|    | 10.2 Applic | ation Protocol ISO 14229 (UDS) Optimisation              | 172 |

|    | 10.3 Gatewa | ay optimisation                                          | 178 |

|    | 10.3.1      | Buffer for the partly store and forward routing strategy |     |

|    | 10.3.2      | Increasing gateways clock frequency                      |     |

|    | 10.3.3      | Summary                                                  |     |

|    | 10.4 Softwa | are reprogramming via FlexRay                            | 182 |

|    | 10.4.1      | Vehicle access by CAN bus system                         |     |

| 11 | Conclusio   | on and Outlook                                           | 188 |

|    | 11.1 Summ   | ary                                                      |     |

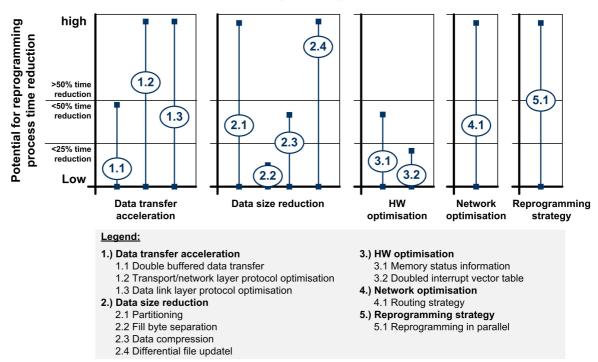

|    | 11.1.1      | Method's performance potential                           |     |

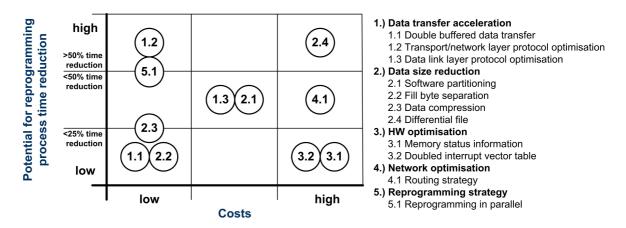

|    | 11.1.2      | Method's potential vs. effort and costs                  |     |

|    | 11.1.3      | Utilisation in practice                                  |     |

|    | 11.1.4      | Further work                                             | 197 |

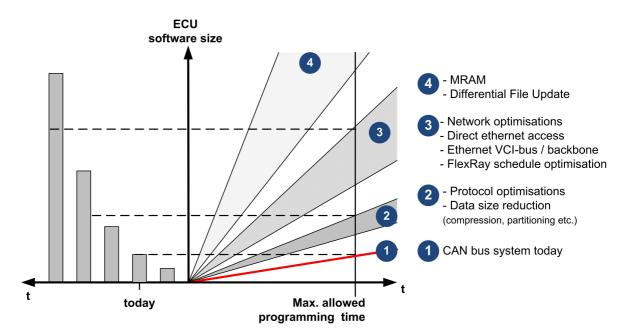

|    | 11.2 Outloo | k                                                        | 199 |

|    | 11.2.1      | Automotive Ethernet                                      |     |

|    | 11.2.2      | MRAM technology                                          |     |

|    | 11.2.3      | Wireless access                                          |     |

|    | 11.3 Conclu | usion                                                    | 200 |

| 12 | Figures     |                                                          | 202 |

| 13 | Tables      |                                                          | 205 |

| 14 | Bibliogra   | ohy                                                      | 207 |

| Α  | Journal P   | aper – IEEE TVT                                          | A-1 |

# Acknowledgement

I thank my supervisor Dr. Ian Dear from the Brunel University for enabling and supporting the research presented in this thesis. The long time we discussed about the reprogramming topics have been always inspired. He found always the right words for motivation also if research progress was not given. Thank you, Ian!

Thanks are owned to Professor Dr.-Ing. Werner Zimmermann from the HS Esslingen -University of applicant science. He supported me since my first university studies and found always time to discuss new trends, protocols or technologies within the automotive diagnostic area. The author work to our book was the base to my interests in automotive communication systems.

I thank the students I supervised during their master thesis for their contributions to several data transfer acceleration topics (in alphabetical order): Samir Karic (ODX-V Development), Susann Kunde (FlexRay introduction), Rolf Molzahn (CAN network analysis), Sascha Neumann (network analysis with Symta/S) and Alexander Stock (FlexRay test system).

Many thanks to my colleges of the department for diagnostic development (GSP/OVE) at the Daimler AG (in alphabetical order): Dennis Artz, Viktor Brester, Gunnar Gaisser, Stefan Glattes, Michael Hiljegerdes, Andreas Kopf, Stephan Römer and Tobias Tetzlaff. Thank you for your support and the good technical discussions during the last years.

Thanks to Andreas Theissler for the good and inspired discussions about software reprogramming as well as for the support during writing the papers or the thesis. Also many thanks to Professor Dr. Joachim Goll for his support.

Lastly, I would like to thank my family for all their love and encouragement. Thanks to my parents who always supported me in all my pursuits. Thanks to my children Salome and Miriam for the understanding that her father was always working at the weekends.

And most of all for my loving, supportive, encouraging, and patient wife Kerstin for the support during all the years and especially during the final stages of this Ph.D. Thank you!

# Acronyms, terms and definitions

| ALU         | Arithmetic Logic Unit                                                          |

|-------------|--------------------------------------------------------------------------------|

| Application | The term "application software" represents the compiled binary code of an ECU. |

| ASAM        | Association for Standardisation of Automation and Measuring Systems            |

| AUTOSAR     | Automotive Open Software Architecture                                          |

| BDC         | Binary Delta Compression                                                       |

| BC          | Bandwidth Control (refer to ISO10681-2)                                        |

| BS          | Block Size (refer to ISO15765-2)                                               |

| BSW         | Basic Software                                                                 |

| CAN         | Controller Area Network                                                        |

| CCP         | CAN Calibration Protocol                                                       |

| cf.         | Latin "confer" – compare                                                       |

| CiA         | CAN in Automation                                                              |

| CPU         | Central Processing Unit                                                        |

| CRC         | Cyclic Redundancy Check                                                        |

| CSMA/CA     | Carrier Sense Multiple Access / Collision Avoided                              |

| CSMA/CR     | Carrier Sense Multiple Access / Collision Resolution                           |

| e.g.        | Latin "exempli gratia" – for example                                           |

| et al.      | Latin "et alii" – and others                                                   |

| ECM         | Engine Control Module                                                          |

| ECU         | Electronic Control Unit                                                        |

| E/E         | Electric and electronic                                                        |

| EEPROM      | Electrical Erasable and Programmable Read Only Memory                          |

| EMC         | Electromagnetic compatibility                                                  |

| EOP         | End of production                                                              |

| EPROM       | Electrical Programmable Read Only Memory                                       |

| etc         | Latin "et cetera" – and so on                                                  |

| FIFO        | First in first out                                                             |

| HIS         | German "Hersteller Initiative Software"                                        |

| HMI         | Human - Machine Interface                                                      |

| ISA         | International Society of Automation                                            |

| i.e.        | Latin "it est" – that means                                                    |

| ISO         | International Standardisation Organisation                                     |

| ISR         | Interrupt Service Routine                                                      |

| JTAG        | Joint Test Action Group                                                        |

| LIN         | Local Interconnect Network                                                     |

| LTE     | Long Term Evolution                                                         |

|---------|-----------------------------------------------------------------------------|

| MCD     | Measurement, calibration and diagnostics                                    |

| MOS-FET | Metal oxide semiconductor field-effect transistor                           |

| MOST    | Media Oriented Systems Transport                                            |

| kb      | Kilobit                                                                     |

| kBit    | Kilobit                                                                     |

| kB      | Kilobyte (1024 byte)                                                        |

| kByte   | Kilobyte (1024 byte)                                                        |

| Mb      | Megabit (1024 kb)                                                           |

| MB      | Megabyte (1024 kB)                                                          |

| msec    | Millisecond                                                                 |

| MRAM    | Magnetoresistive Random Access Memory                                       |

| MTJ     | Magnetic Tunnel Junction                                                    |

| NVM     | Non Volatile Memory                                                         |

| ODX     | Open Diagnostic Data Exchange                                               |

| OEM     | Original Equipment Manufacturer                                             |

| OICA    | Organisation internationale des Constructeurs d'Automobiles                 |

| OPEN    | One Pair Ethernet                                                           |

| PC      | Personal Computer                                                           |

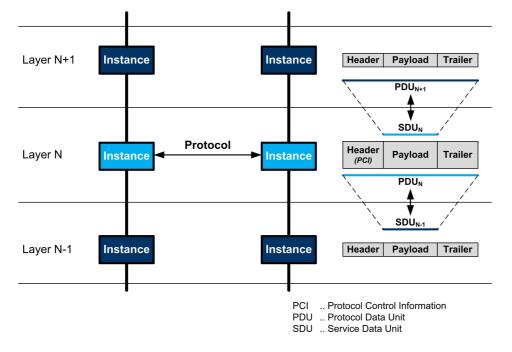

| PCI     | Protocol Control Information                                                |

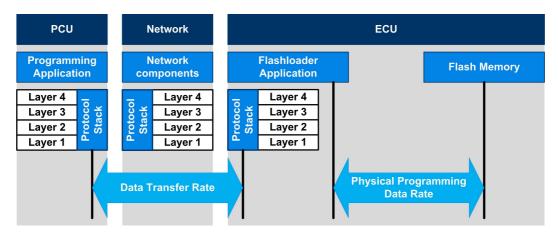

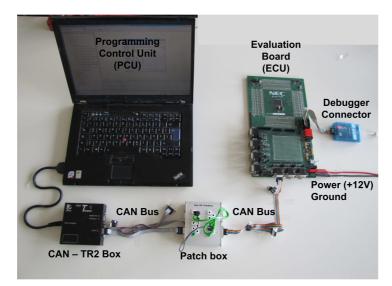

| PCU     | Programming Control Unit<br>Initiates and controls a reprogramming process. |

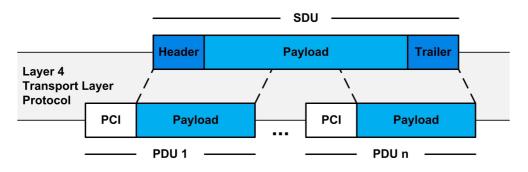

| PDU     | Protocol Data Unit                                                          |

| PLL     | Phase-locked Loop                                                           |

| PROM    | Programmable Read Only Memory                                               |

| RAM     | Random Access Memory                                                        |

| ROM     | Read Only Memory                                                            |

| RTE     | Runtime Environment                                                         |

| SAE     | Society of Automotive Engineers                                             |

| SDU     | Service Data Unit                                                           |

| SID     | Service Identifier                                                          |

| SOP     | Start of Production                                                         |

| STmin   | Minimum Separation Time (refer to ISO15765-2)                               |

| TTCAN   | Time Triggered Controller Area Network                                      |

| VCO     | Voltage-controlled Oscillator                                               |

| XCP     | Universal Measurement and Calibration Protocol                              |

| \$01    | "\$" indicates a hexadecimal (hex) nomenclature.                            |

|         |                                                                             |

# **1** Introduction

# Content

| 1.1 | Vehicle's life cycle2        |                                                |     |  |  |

|-----|------------------------------|------------------------------------------------|-----|--|--|

| 1.2 | Repro                        | Reprogramming within an ECU's life cycle4      |     |  |  |

| 1.3 | Aspe                         | cts of software reprogramming                  | 7   |  |  |

|     | 1.3.1                        | Automotive innovation vs. software size        | 8   |  |  |

|     | 1.3.2                        | Automotive development focus and priority      | 9   |  |  |

|     | 1.3.3                        | Automotive system complexity and compatibility | .10 |  |  |

|     | 1.3.4                        | Automotive network aspects                     | .12 |  |  |

|     | 1.3.5                        | Summary                                        | .14 |  |  |

| 1.4 | Scop                         | e of the thesis                                | 15  |  |  |

| 1.5 | Organisation of the thesis16 |                                                |     |  |  |

Ever since the invention of the car by Carl Benz (1844-1929) 125 years ago engineers have been striving to improve performance, increase reliability and reduce costs. Early innovations were based around purely mechanical leap forwards in technology. However, over the last 30 years electronic systems have been rapidly taking over the technology advances to improve functionality, performance, reliability and reduce costs. Currently, more and more functionality, which was implemented in hardware in the past, is implemented in software today. In-addition, what was futuristic driver assist or even replacement technology is now a reality due to this computing power. If we consider the mid to high range end of the market it is now warrantable to talk about highly complex computer systems on wheels. This revolution is primarily due to the rapid trends in more powerful microcontrollers and communications technology. Complex mathematical algorithms, which required complete computer centres in the past, can be calculated on a single powerful microcontroller today. This added to the revolution in real-time sensor technology, and has created a new era for personal transport technology. A consequence of this

trend in rapid expansion of software quantity in embedded systems is the need to consider the hidden cost of increasing software quality and maintainability in embedded systems. With focus on the automotive industry, one of the most fitting statements about the automotive future is:

The majority of all automotive innovations will be within the electrics and electronics (E/E) area. The vast part will be software.

This prediction is supported by nearly all vehicle manufacturers [Dra11], suppliers [Hau11] and scientists [Bro11]. Of course, the percentage values vary but the basic statement is equal: The quota of electronics (hard- and software) and as a result complexity will continuously increase. This thesis is also supported by the Oliver Wyman Automotive's study "Car Innovation 2015" given by J. Dannenberg and J. Burgard et al. They predict that "electrics and electronics will remain the most important enabler of automotive innovations through 2015 and beyond, and will grow by six percent annually" [Dan07].

These prospects have a simple consequence: increasing amounts of software results in longer software reprogramming time for those embedded systems. That was not a problem so far but today software size has been increased in such a way that fundamental activities within the product life cycle, e.g. initial programming of the Electronic Control Units (ECUs) during production process or software updates within service / after sales can no longer be handled within adequate time windows. Expanding reprogramming time finally results in economical and therefore financial disadvantages for the automotive industry. This aspect raises some crucial questions:

- 1) Why is software reprogramming such an important issue?

- 2) Why is software reprogramming process acceleration necessary?

- 3) Is there a basic approach to solve the reprogramming challenge?

- 4) Are there any other industries that have the same essential problems?

Within this chapter an overview is given to software reprogramming aspects with the aim to provide answers to the crucial questions according to ECUs' or embedded systems' software reprogramming process.

#### 1.1 Vehicle's life cycle

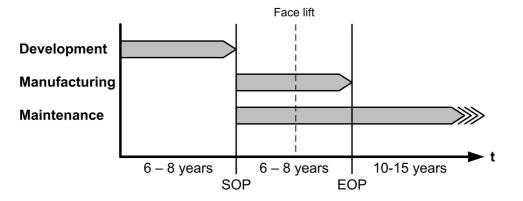

Compared to other electronic systems, vehicles and therefore automotive ECUs have a quite different life cycle. As depict in figure 1.1-1 a car is typically developed between 6 and 8 years. The model line is manufactured and sold also between 6 and 8 years. After the vehicle is manufactured the maintenance time period starts where the first 2 -3 years a

warranty time is given. The challenge within the automotive industry is the combination of a mass product with a long time life cycle combined with the high dynamic in electronic development and technology's evolution.

Figure 1.1-1: Vehicle model line life cycle

It is a common intention of all vehicle manufacturers to reduce the development period as well as the manufacturing time (hours per vehicle) for new model lines. Hence, several model lines will derive from a basic platform. This allows the reuse of electrical and electronic components (e.g. sensors, actuators and ECUs) to reduce costs. Exact values for the different periods in figure 1.1-1 as well as numbers of derived model lines can not be given because these are commercial sensitive data, and these vary for different vehicle manufacturers.

Figure 1.1-1 also depicts, that an electrical design decision (e.g. ECU functionality, communication network architecture etc.) have been made a long time period before the model line is initially produced (Start of Production – SOP). These decisions will also influence the maintenance processes for that model line several years after model line's end of production (EOP) time. Typically significant changes of such design decisions can not be modified so easily. It might be possible to make some new design aspects in the middle of a model line production period, but typically significant changes are not intended e.g. bus architectures, network design.

The thesis is looking at vehicles that are now in the development or production stage and identifies the current problems associated with the embedded system's software reprogramming process. The aspects above also make a contribution to the discussions within this thesis.

# 1.2 Reprogramming within an ECU's life cycle

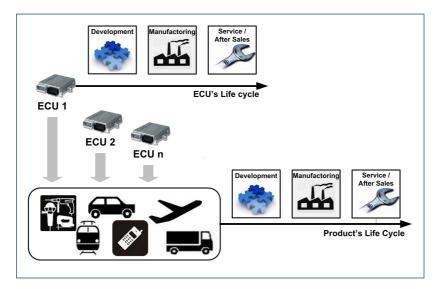

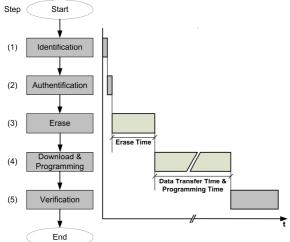

Today electronic control unit's application software reprogramming is an important issue. At the very least, if the ECU is manufactured the application software still has to be initially programmed. Depending on the final usage and the final product's life time, an ECU could be reprogrammed several times during its life cycle. Figure 1.2-1 depicts an abstract overview. Below the typical reprogramming stages within a vehicle ECU's life cycle are described with focus on automotive ECUs.

Figure 1.2-1: Reprogramming stages within an ECU's life cycle

#### Software reprogramming during the development process

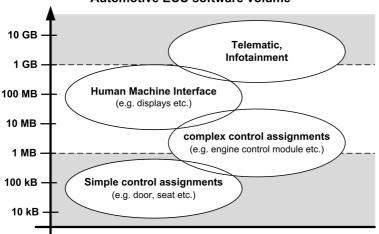

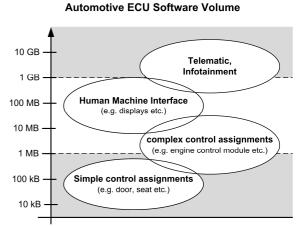

During the ECU's development process the software may be reprogrammed several times because new functionality is developed or bugs are fixed. Especially in an early development state only a few ECUs are available for testing. Within typical ECU development processes the different features and the complete functionality are not available on the first (early) sample. The functionality increases step by step and therefore reprogramming of an ECU's application software is an essential issue. Figure 1.2-2 depicts the current typical software volumes for automotive ECUs depending on their assignments.

If the ECU is part of a more complex system (e.g. vehicle, plane, train, machine etc.) functionality could be distributed over several ECUs. In that case it might be necessary to reprogram application software of more than one ECU, e.g. for bug fixing purposes or to have the latest software version for testing. Especially the last aspect has a strong correlation to software reprogramming time: with focus on the automotive industry, a modern high-end class car includes up to 80 different ECUs where each ECU provides several functionalities. If such a vehicle-in-development is prepared for test drives (e.g. winter tests in Scandinavia or heat tests in the USA etc.) the most recent software for each ECU

should be programmed. Hence, the total amount of time per vehicle should be as small as possible, especially if a fleet of several vehicles is prepared.

Automotive ECU software volume

Figure 1.2-2: Automotive ECU software volume

Another reprogramming scenario during the development process is the adaptation of software to a vehicle, e.g. parameterisation of an engine control unit to the engine. In that case the parameter set has to be reprogrammed several times until the final parameter set is found. Until the engine control unit is reprogrammed the ignition is off. Hence, the engine is not running and the electrical power for all ECUs is supplied completely by the vehicle battery. To guarantee a correct process without low system voltage interruption the programming time should be as fast as possible.

#### Software reprogramming during manufacturing process

ECU's application software programming process is an essential part of the value chain. During the ECU's production process the final ECU software is programmed into the target system. Two different scenarios could occur: 1) ECU's application software is completely programmed during the ECU manufacturing process within the ECU assembling line or 2) one or more software fragments are programmed later within the vehicle assembling line. Of course, in both cases the final application software is programmed, but due to the different reprogramming places the total reprogramming time has different consequences.

If the ECU is programmed completely within the ECU's manufacturing process (scenario 1), the ECU could be programmed before packaging. Thus the microcontroller's internal interfaces<sup>1</sup> are available and usable. The software is programmed very fast but

<sup>&</sup>lt;sup>1</sup> refer to chapter 2

typically without standardised protocols. This strategy is preferred if only one software variant of the ECU exists and no specific software adaptation for the final control assignment is necessary.

If the ECU has a specific software part depending on the final control assignment it might provide some benefits if the final software is programmed at the vehicle assembly line. For example, an engine control module (ECM) could have different parameter sets depending on the number of the engine's cylinders. If vehicles with different engines are produced on the same assembly line and the ECMs have been delivered finally programmed, each ECM variant allocates storage place. Late programming at the vehicle assembly line (scenario 2) provides a) economic benefits because of the smaller and less complex part storage requirements and b) assembly complexity is decreased because the manufacturer has only one device for selection. These economical benefits will not be achieved if the total software programming process time significantly increases the assembling line clock. Here a strong necessity is given to quantify and reduce the reprogramming time.

#### Software reprogramming within service or after sales market

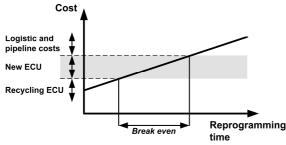

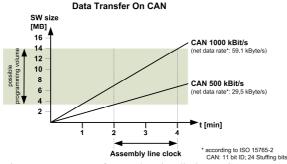

Software reprogramming is an important repair method for the vehicle manufacturers in the aftersales or service market. If customer's complaints could be solved by a new software release reprogramming is the preferred repair method. As discussed above, ECU software sizes vary in a range of several kByte up to several MByte depending on ECU's control assignment (refer to figure 1.2-2). As a consequence today's reprogramming process time is in regions of several minutes up to hours based on the currently given automotive bus systems (discussed later in section 1.3.2).

The total time for the software reprogramming process has an immediate economic impact. The more time required the higher the costs are. For the garage the equipment (e.g. Programming Control Unit (PCU), power supply etc.) and the working area are occupied during that time. For the customer the vehicle is not usable. If the total time for software updates enlarges up to hours economical and therefore financial disadvantages occur, e.g. if a truck requires a longer garage time. In case of a software bug the vehicle manufacturer has to pay the down time costs.

Another aspect is to decrease the risk of process errors. Depending on the existing environmental conditions, a software reprogramming process is more or less stable. The more time a reprogramming process requires the higher the risk of interruption. The acceleration of a software reprogramming phase reduces this risk and provides a more stable and reliable process.

|                     | 2010       | 2011       | change in % |

|---------------------|------------|------------|-------------|

| Passenger vehicles  | 63.377.724 | 66.237.761 | + 4.5       |

| Commercial vehicles | 14.180.650 | 14.033.714 | -1.0        |

| Total               | 77.558.374 | 80.271.475 | + 3.5       |

| Table 1.2-1: | World automotive | production | [Vda11] |  |

|--------------|------------------|------------|---------|--|

|--------------|------------------|------------|---------|--|

The increasing software sizes in future vehicles will increase the software reprogramming times, too. If it is assumed that only one ECU of each new produced vehicle will be reprogrammed within the warrantee period, the increased costs will be enormous. As depicted in table 1.2-1 the world automotive production was up to 66 million passenger cars in 2011 [Vda11]. A reprogramming process cost reduction, e.g. by reprogramming time reduction etc., of  $1 \in$  provides world wide potential up to 80 million  $\in$  per year.

#### Summary

The necessity to reprogram ECU application software is given during the complete product life cycle. The increasing software size provides new problems which have never existed before. The result is an economical disadvantage that could be solved by decreasing software reprogramming time. Generally this topic is not only relevant for the automotive industry. The increasing software reprogramming time of a plane requires a longer down time in the hangar or machines are longer non-productive. However, the cost market of the business areas is completely different. Compared to the automotive industry, where vehicle piece costs are responsible for the cost pressure, in other industries the maintenance costs are important.

Hence, approaches to accelerate the software reprogramming process in the automotive industry are necessary, especially if the predictions and forecasts as mentioned above become true.

# 1.3 Aspects of software reprogramming

Today ECU application software reprogramming is an important issue within an ECU's life cycle. Especially in the after market business software reprogramming is a powerful repair method to solve software errors and in some cases it is the only repair method. Of course, the reprogramming process was established years ago, but with focus on the current automotive industry software reprogramming and the required time for this process becomes continuously more important. Also environmental aspects of software reprogramming are explained as well as an overview of history and reasons are given why the current situation is as it is.

#### 1.3.1 Automotive innovation vs. software size

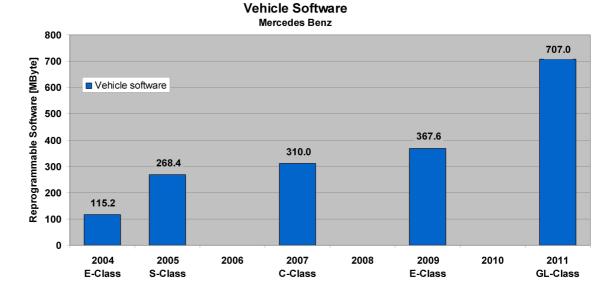

The automotive market is highly competitive. Innovations and new technologies are influencing customer's decisions when they select a new car. As already mentioned, the majority of all automotive innovations will be within the electrics and electronics (E/E) area. Today a significant part of vehicle's characteristics is made by software. This trend was already recognized in 2006 by W. Huhn and M. Schaper as they wrote in the McKinsey on IT report: "the focus and value in engineering products is shifting from chips to code" [Huh06]. Today the amount of software is up to 100 million lines of code and thousands of functions are controlled by software [Bro11]. M. Broy has analysed the vehicle software ratio during the last 40 years and identified an exponential increase [Bro11]. This statement is supported by the analysis of the software ratio within Mercedes-Benz vehicles since 2004 (refer to figure 1.3-1). Starting in 2004 the amount of embedded systems' software has doubled every 2.5 years. The tendency will be supported by the next S-Class generation in 2013 where again doubling of the software size is predicted.

Figure 1.3-1: Amount of vehicle software of Mercedes-Benz

The exponential growth has now reached the boundary where the amount of software is so high that the old concepts for software reprogramming are no longer able to fulfil the required process time limits (e.g. given by the assembly line clock).

# 1.3.2 Automotive development focus and priority

Compared to other industries the automotive industry has a very special role. In 2010 up to 77.6 million vehicles were manufactured worldwide<sup>2</sup>. In contrast to the manufacturing of planes or industrial machines with less than 1000 parts/year<sup>3</sup>, manufacturing cost aspects are in focus. M. Broy et al. [Bro11a] describe several reasons, where typical issues to reduce system complexity by decoupling system layers are not or only partly implemented because of cost aspects. With focus on software reprogramming only the following three examples of his list are mentioned and evaluated:

The number of running processes on a single microcontroller is increasing such that runtime behaviour and the schedule of those implemented processes have to be extensively organised.

The consequence is that new software (e.g. tasks or processes) is allocated on that microprocessor as long as resources are free. Clearly structured and layered software architecture is not implemented because memory intensive interfaces have been optimised for code size and runtime aspects. Also functionalities of different layers are combined to save memory resources. This results in an increasing software complexity and the necessity to reprogram the complete application software instead of single software parts.

Microcontroller's memory is so scarcely dimensioned that additional functionality is only possible by an expensive step to the next microcontroller's memory size.

Another aspect from cost discussion's point of view is the fact that microcontroller manufacturers supply microcontrollers with tiered memory sizes. The step to the next memory size results in higher costs for the microcontroller (significantly higher costs during model line life cycle because of the high number of parts/year). Hence, the above described optimisation of code size is the consequence in order to use the given memory size.

Compared to Ethernet commonly used within the PC industry, the simple and less resource consuming bus systems have less bandwidth and a strong dependency between physical layer, transport layer and application layer. Hence, they can not be parameterised independently.

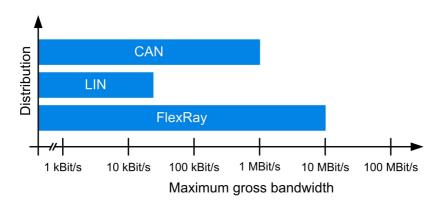

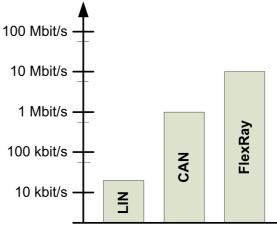

Figure 1.3-2 provides an overview about the currently most important and most implemented bus systems.

<sup>&</sup>lt;sup>2</sup> OICA - Provisional Production Statistics 2010 [OICA2010]

<sup>&</sup>lt;sup>3</sup> Refer to M.Broy et.al. in [Bro11a]

Figure 1.3-2: Most implemented automotive field bus systems

Until today these bus systems are sufficient for normal ECU communication based on signal exchange as well as for data transmission in case of software reprogramming. Cost aspects as well as construction<sup>4</sup> and weight<sup>5</sup> aspects are also reasons why an exclusively high performance network for software reprogramming purposes is not possible. Hence, other less cost intensive approaches are necessary to solve the current situation of increasing software despite the nearly constant vehicle bus system's bandwidth.

# 1.3.3 Automotive system complexity and compatibility

#### Innovation

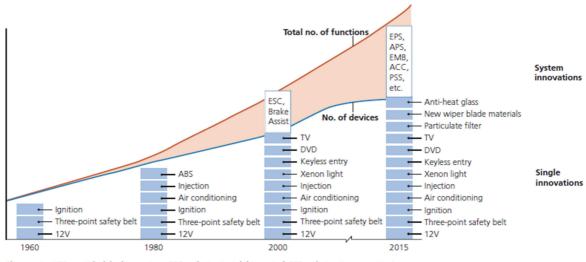

During recent years a noticeable move from single innovations to system innovations is visible. In the past a typical ECU provided a single functionality and was used for a single assignment. Today more and more different functionalities are combined to a more complex function.

Figure 1.3-3 depicts this shift on a time line. According to that picture, single innovations will move into saturation but systems innovation will expand. M. Broy et al. mentioned that prospective innovation for infotainment systems, advanced driver assistance systems or safety systems will only be possible by distributed and connected functions [Bro11a].

<sup>&</sup>lt;sup>4</sup> The position of cable bundles as well as their cross section has to be considered for car body and chassis construction. The cable bundle cross selection could not be increased endlessly because of car body's sturdiness.

<sup>&</sup>lt;sup>5</sup> Additional cable results in a higher weight and this has an impact on the fuel consumption and vehicle emissions. This is opposed to the current vehicle manufacturer strategy with green technology, less fuel consumption and less/zero emissions.

Please note: ABS = anti-lock braking system, ESC = electronic stability control, EPS = electronic power steering, APS = adaptive power steering, EMB = electro-mechanical braking, ACC = adaptive cruise control, PSS = predictive safety systems

#### Figure 1.3-3: Shift from single to system innovation [Dan07]

J. Dannenberg et al. [Dan07] support the observation of this evolution by an example of the Mercedes-Benz PRE-SAFE<sup>6</sup> system: "it links existing systems like crash sensors and ESP with seat controls, seatbelts and the sunroof, adding safety functions to existing components".

The move to system innovations is also visible in new automotive terminologies like function-orientated development. This means that a system's function is not tightly bound to a single ECU but multiple ECUs will be used to support a function based on factors such as memory availability and microcontroller load. This will have a significant impact on reprogramming times and strategies.

#### Compatibility

Due to the move to system innovations, a new challenge occurs: software compatibility. If an error occurs within such a distributed system it has to be guaranteed that a change of a single ECU's software which is part of that system results in a compatible common system. Especially within the automotive industry, where vehicles have no fixed and stringent service intervals and a customer is free to visit a garage or not, new software could be programmed into an old vehicle. The functional distribution of systems and the complexity results in an increasing test demand to guarantee compatibility. Depending on the

<sup>&</sup>lt;sup>6</sup> Mercedes-Benz PRE-SAFE system was introduced in 2002 as the first anticipatory protection system. In case the system recognises that in a situation a crash in unavoidable, the system initiates some activities to optimise passenger's situation if the crash occurs (e.g. close windows, tighten seat belts, move seats in an optimised position etc.).

involved ECUs the test permutation is so high, that it is not possible to test each possible combination. In that case testing of a well known release is a very efficient method but results in a release update where several ECUs have to be reprogrammed.

Table 1.3-1: Software release types

|                    | Release Type | Description                                                              | Usage                                                                                        |

|--------------------|--------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Single ECU         |              | Software release for a single ECU.                                       | • Each ECU                                                                                   |

| Equal ECUs         |              | Software release for<br>multiple but functional<br>equal ECU.            | <ul> <li>Door Control Unit</li> <li>Seat Control Unit</li> <li>etc.</li> </ul>               |

| System<br>Release  |              | Software release for<br>multiple/all ECUs which<br>are part of a system. | <ul> <li>Illumination system</li> <li>Driver assistence<br/>systems</li> <li>etc.</li> </ul> |

| Domain<br>Release  |              | Software release for all<br>ECUs which are part of<br>the same domain.   | <ul> <li>Power train</li> <li>Body domain</li> <li>Chassis domain</li> <li>etc.</li> </ul>   |

| Vehicle<br>Release |              | Software release for all<br>ECUs which are part of<br>the vehicle.       | <ul><li>Car</li><li>Truck</li><li>etc.</li></ul>                                             |

Table 1.3-1 provides an overview about possible release types. As a consequence of less test demand within development the reprogramming amount to service a vehicle in a garage is increasing.

# 1.3.4 Automotive network aspects

#### Complexity

Since the first automotive systems were interconnected in the early 1980s vehicle communication networks have become more and more complex. Figure 1.3-4 depicts the network evolution. At the beginning only vehicle functionality was interconnected by bus systems. The main focus was to reduce the number of sensors and the reduction of discrete wires and cables between the different ECUs. The continuous introduction of electronic systems results in more complex networks. HMI, telematics and infotainment systems become more important and their communication demands have increased. The current development trend is on driver assistance systems. Surround camera systems, radar, infrared or ultrasonic systems continuously scanning the vehicle's environment. The corresponding advanced driver assistance systems (e.g. park assistance<sup>7</sup>, lane departure warning<sup>8</sup> [merced] etc.) process the generated data and support the driver. As a result more and more domains are interconnected.

Figure 1.3-4: Increasing network complexity

While as of today only vehicle-internal domains are interconnected, the next technology steps will interconnect vehicles (i.e. car-to-car communication) as well as connect a vehicle into normal e-business networks (e.g. car hiring systems or smart charging communication for e-vehicles<sup>9</sup>). With focus on software reprogramming this development has some impacts:

- New bus systems are introduced to support functional communication requirements e.g. for new regulation systems. Those bus systems shall be used for software reprogramming communication too because cost aspects do not allow a second communication link exclusively for reprogramming.

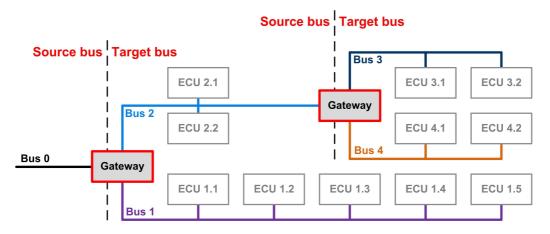

- Depending on the domain architecture several gateways have to be passed for a software reprogramming communication link to establish communication to the most outlying ECU. The data routing time of these gateways results in time delays and increases the total programming time.

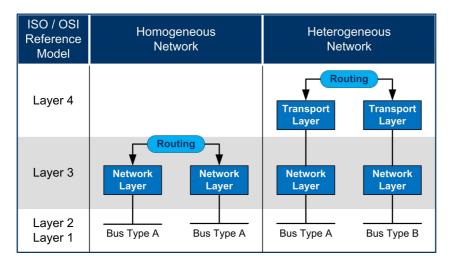

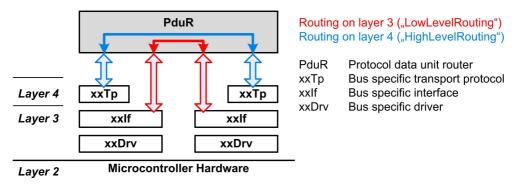

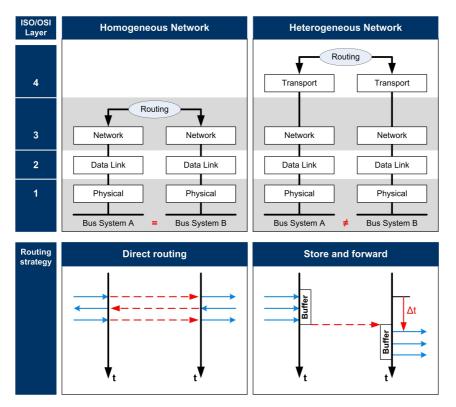

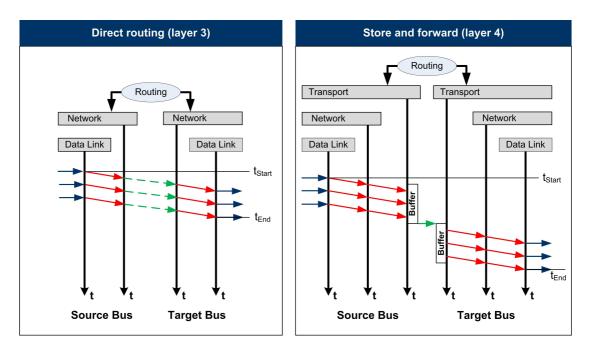

- Depending of the network connection type (heterogeneous network or homogeneous network) data routing is required on different layers according to the ISO/OSI

<sup>&</sup>lt;sup>7</sup> Park Assistance – autonomous car maneuvering from a traffic lane into a parking space.

<sup>&</sup>lt;sup>8</sup> Lane Departure Warning System – warns a driver when the vehicle begins to leave out of its lane.

<sup>&</sup>lt;sup>9</sup> E-vehicles: vehicles with electrical engine

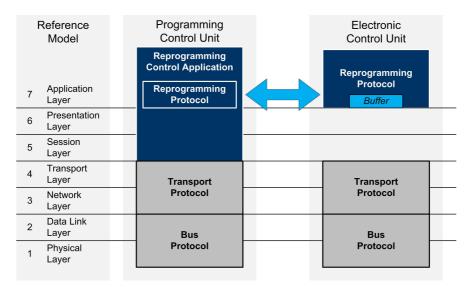

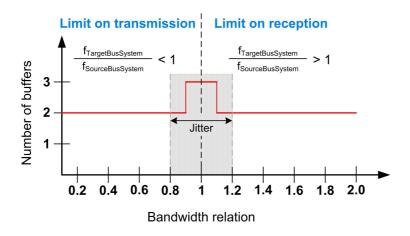

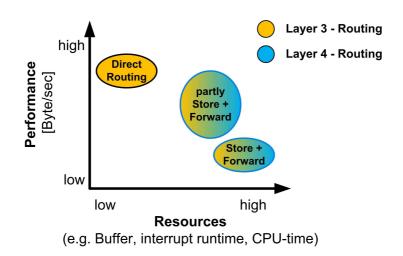

reference model layered architecture [ISO7498-1]. Due to that fact the data routing results in different routing strategies which has impacts to required resources (e.g. Buffer) as well as the possible routing performance and routing execution times.

#### Costs

Cost aspects, as described above, are the reason why normal vehicle functional communication and reprogramming communication share the same vehicle network. As there was no functional requirement for a high speed and being more expensive network up to now high speed networks have not be placed inside automobiles. Since the amount of software has been increasing the resulting programming time is meeting the timing limits of network, thus testing and reprogramming requirements are starting to drive the network speed requirements and functional becoming less important. To evaluate a business case to incorporate design considerations to reduce reprogramming time requires accurate predictions of reprogramming times. The physical network infrastructure (e.g. the cable trees) within the vehicle is a foundation that forms the heart of the system. New bus systems and network architectures can not be introduced easily or at low cost within an older vehicle. In contrast more powerful ECUs' (microcontrollers with better performance, more interfaces, increased memory size etc.) will be developed during a vehicle's life cycle and could be also introduced into an older car. Hence, network architecture as well as the bus systems' performance and the gateways' routing performance paired with a long-term persistence have a deep impact for software reprogramming strategies.

#### 1.3.5 Summary

Software reprogramming of automotive ECUs is a very important issue within a vehicle's life cycle. For bug fixing, software reprogramming is a method (sometimes the only low cost method) for the ECU supplier as well as for vehicle manufacturers within development, manufacturing and service/after-sales. The required time for software reprogramming is an important economical factor and depends on the software size to be reprogrammed as well as the communication link performance.

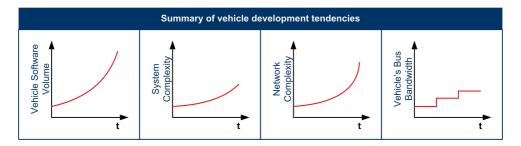

Figure 1.3-5: Vehicle development trends

Figure 1.3-5 depicts the current development tendencies. The software volume, system complexity (e.g. ECU's functionality dependencies) and network complexity (total number of bus systems, gateways and different bus system types) are significantly increased but the vehicle's network performance (bus bandwidth) is nearly constant. If the future trends discussed above become true, some challenges with focus on automotive software reprogramming occur:

- The demand for software reprogramming will still increase due to the increasing total amount of software within vehicles.

- Comprehensive reprogramming procedures for several ECUs will be necessary if complex distributed systems have to be reprogrammed to retain a compatible system.

- Software reprogramming time will still be increasing continuously due to increasing software size and the need to reprogram several ECUs.

Independent of future approaches to reduce the total complexity (e.g. software size, system dependencies and complexity) it might be necessary to accelerate the total automotive software reprogramming process.

# 1.4 Scope of the thesis

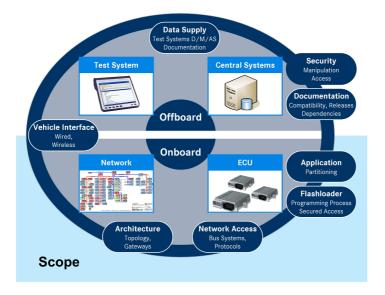

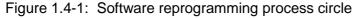

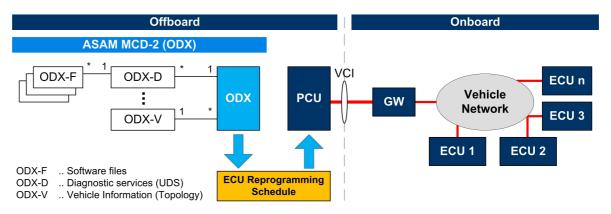

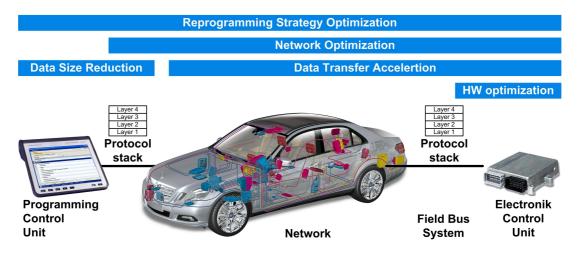

Within the automotive industry the ECU application software reprogramming process is quite complex. Figure 1.4-1 depicts the reprogramming process cycle divided into an off-board (non-vehicle) part and an onboard (vehicle) part.

The scope of the work reported in this thesis is on the on-board part of the global reprogramming process. ECU aspects (flashloader, application software, network access, communication protocols etc.) and network aspects (architecture, topology etc.) are the focus of investigation.

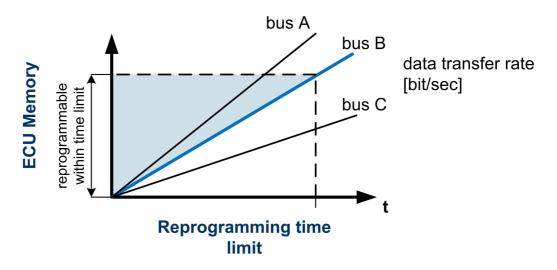

Figure 1.4-2: Software reprogramming time limitation

As depicted in figure 1.4-2 for future ECUs the given time limitation requirement to the maximum reprogramming time will not be fulfilled any longer without any optimisation. The research aims are:

- Quantify the reprogramming problem in today's vehicle architectures and communication standards and provide possible short term solution to the existing reprogramming issues.

- Quantify the impact that future emerging standards and technologies will have on reprogramming embedded ECUs and identify solutions to minimise their impact on reprogramming cost.

# 1.5 Organisation of the thesis

The thesis covers the onboard aspects for software reprogramming within automotive networks as defined in figure 1.4-1.

This chapter has identified the potential problem that the uptake of technology revolution, driven by the need for increased functionality has on reprogramming of complex embedded systems in the automobile industries. Not only does the industry have high production volumes, for an electronic product, it has long design times, production cycles and life time warrantee and thus long legacy costs. Problems caused today can have a very long term cost implication. Care must be taken to ensure future developments in car design consider all key life-time cost drivers. Chapter 2 provides the key architectural and implementation background information to the software reprogramming process and the involved components for the current state of the art ECUs. It also identifies the key areas where acceleration is possible in reprogramming time for existing technologies i.e. improved data transfer rates and data compression strategies. Additionally all necessary terms and definitions are introduced.

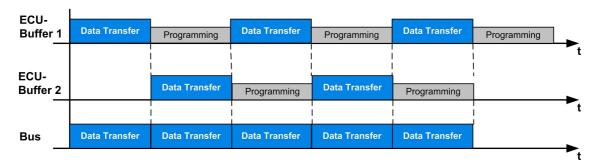

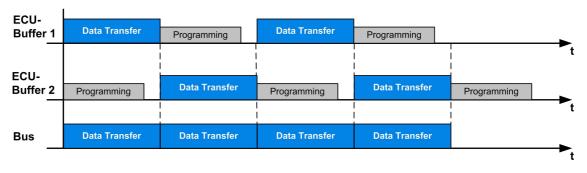

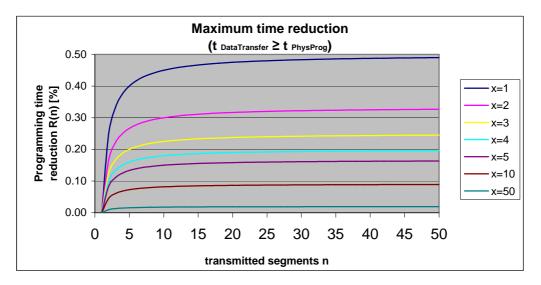

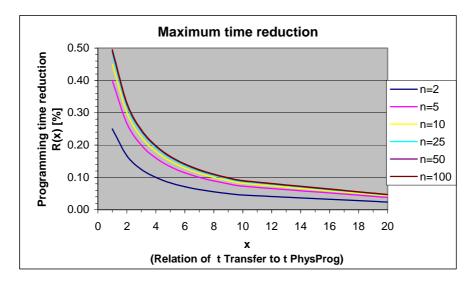

In Chapter 3 a new concept of using double buffering in the reprogramming procedure of ECU is introduced. A model is generated to evaluated and quantify the improvement of this approach.

In chapter 4 the research results are discussed to accelerate data transfer by communication protocol optimisations which are currently in use for automotive systems' software reprogramming process (i.e. vehicles currently in production and legacy systems) and new technologies currently being designed into the new generation of car systems. For each of these communication protocols this chapter generates quantitative models that can be used to evaluate reprogramming data transfer performance.

Chapter 5 discusses and introduces new approaches to reduce the amount of data needed to be transmitted during software reprogramming. Quantitative models are again produced to complete the set of techniques needed calculate optimum reprogramming time for current technology solution available.

Chapter 6 introduces theoretical hardware modification that could be made to ECU designs to optimise and to speed up the reprogramming process.

In chapter 7 the impact of the network architecture on the reprogramming process is discussed and evaluated. Coupling of different networks and routing aspects within gate-ways are discussed.

Reprogramming several ECUs in parallel is a powerful approach to optimise reprogramming time. The required pre-conditions and a method to schedule the ECUs to be reprogrammed are discussed in chapter 8.

Chapter 9 provides an introduction to the newly awaited MRAM technology and identifies how it could be utilised to implement some of the reprogramming approaches presented in chapter 5.

Chapter 10 provides case studies where some of the discussed approaches are implemented within an ECU and quantitative models verified.

Chapter 11 summarises the work and provide an outlook for future methods and technologies.

# 2 Background

# Content

| 2.1        | Embedded Systems 19                      |                                                                                                                   |                                       |  |

|------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|

| 2.2        | Electronic Control Unit                  |                                                                                                                   |                                       |  |

|            | 2.2.1                                    | Microcontroller                                                                                                   | .21                                   |  |

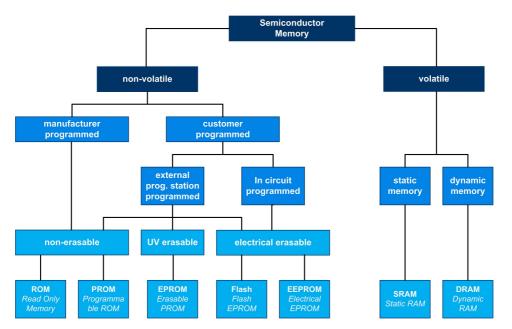

|            | 2.2.2                                    | Memory                                                                                                            | .22                                   |  |

|            | 2.2.3                                    | ECU Software Components Overview                                                                                  | .24                                   |  |

|            | 2.2.3.                                   | 1 Application Software                                                                                            | .25                                   |  |

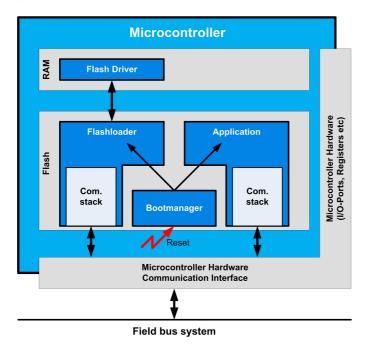

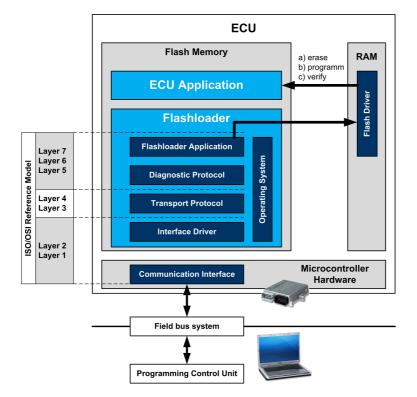

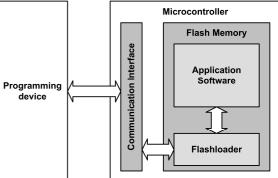

|            | 2.2.3.2                                  | 2 Flashloader                                                                                                     | .25                                   |  |

|            | 2.2.3.3                                  | 3 Boot Manager                                                                                                    | .27                                   |  |

| 2.3        | Prog                                     | ramming Control Unit (Test system)                                                                                | 28                                    |  |

| ~ 4        |                                          |                                                                                                                   |                                       |  |

| 2.4        | Prog                                     | ramming Sequence                                                                                                  | 29                                    |  |

| 2.4<br>2.5 | -                                        | ramming Sequence                                                                                                  |                                       |  |

|            | -                                        |                                                                                                                   | 33                                    |  |

|            | Comr                                     | nunication Stack                                                                                                  | <b>33</b><br>.35                      |  |

|            | <b>Com</b> r<br>2.5.1                    | munication Stack         Field bus systems                                                                        | <b>33</b><br>.35<br>.36               |  |

|            | <b>Com</b> r<br>2.5.1<br>2.5.2           | munication Stack         Field bus systems         Media Access Control Overview                                  | <b>33</b><br>.35<br>.36<br>.36        |  |

|            | Comr<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4 | munication Stack         Field bus systems         Media Access Control Overview         Transport Layer Protocol | <b>33</b><br>.35<br>.36<br>.36<br>.38 |  |

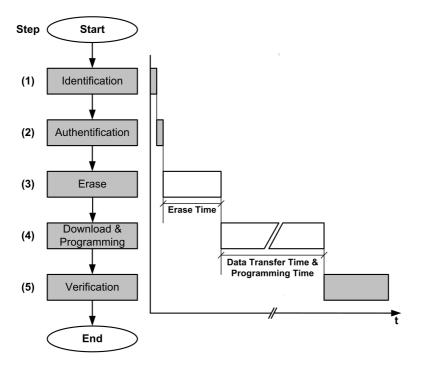

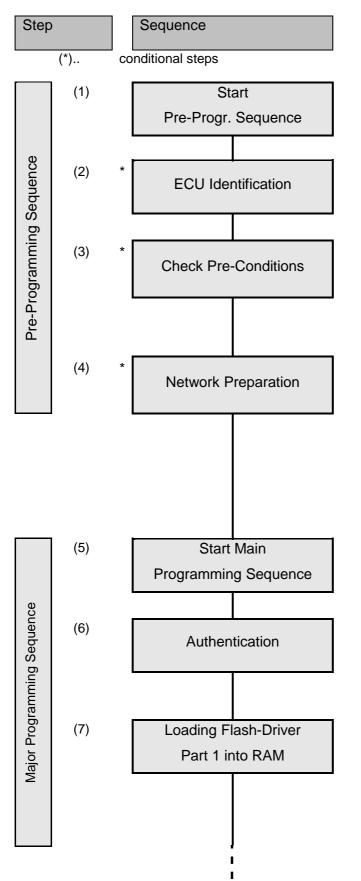

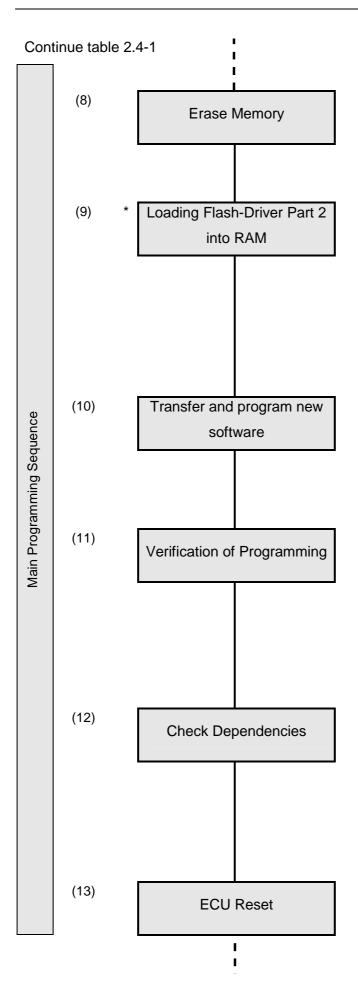

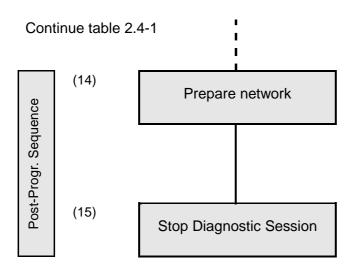

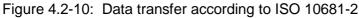

This chapter provides a short introduction into the software reprogramming process of embedded systems. The sub-components of an electronic control unit (ECU) which are relevant for the reprogramming process are explained and an introduction to the specific terms is given. The reprogramming sequence sub-clause shows the different steps of a reprogramming process. The communication stack sub-clause introduces into automotive embedded system's communication and the relevant protocols.

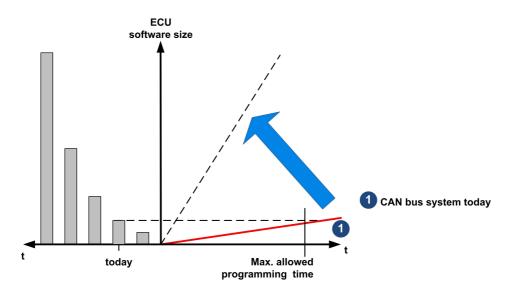

# 2.1 Embedded Systems

Today monitoring, control and regulation problems in technical systems (e.g. medical instruments, machines, vehicles, aeroplanes) are mainly realised by microcontrollersupported embedded systems (refer to [Ren11]). "Embedded system" is more a general term than a well defined system definition. M. Barr characterised embedded systems as "a combination of computer hardware and software, and perhaps additional mechanical or other parts, designed to perform a dedicated function" [Bar07]. Today the term "electronic control unit" (ECU) is established as a synonym for an embedded system. It could become more complex if at least two or more ECUs are part of a distributed embedded system. In that case normally they are interconnected via field bus systems to exchange data.

Figure 2.1-1 depicts a simple embedded system with the relevant components.

Figure 2.1-1: Embedded system components

A good example for a complex embedded system is a car where several systems allocated on several ECUs interact by exchanging data via a network. Such systems are also available on aircraft, trains, weapons and machines, and everywhere sensors and actors have to be controlled or regulation assignments are given.

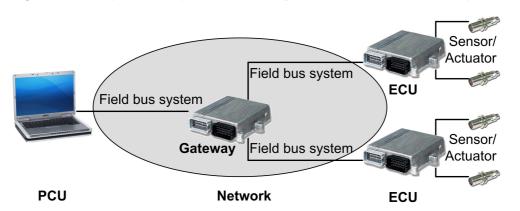

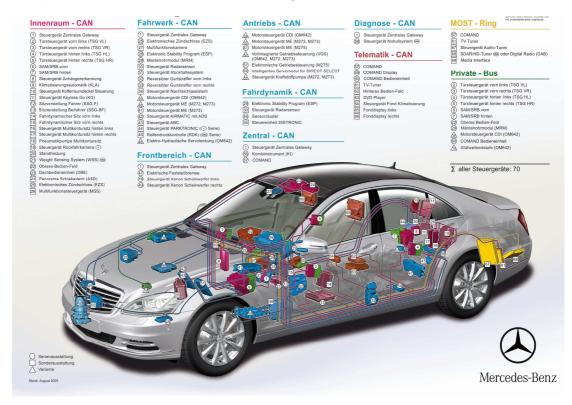

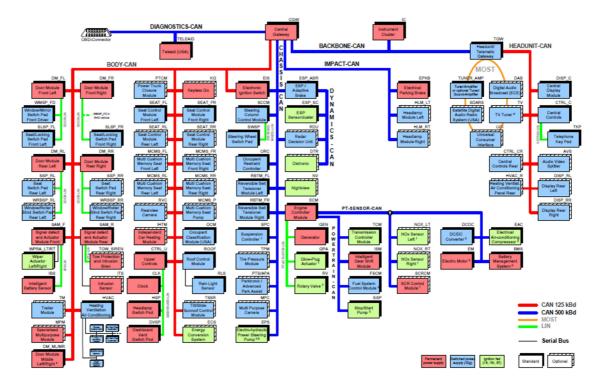

Figure 2.1-2 and figure 2.1-3 depict the more complex embedded system of a Mercedes Benz model line 221 (S-Class) vehicle. Each coloured square represents an ECU. The coloured lines representing communication bus systems (field bus systems - refer to section 2.5.1). The number of ECUs within a vehicle is growing continuously from only 2 ECUs (Engine control system ("Motronic") and breaking system - ABS) in the 1980s up to nearly 80 ECUs within modern premium class vehicle.

The positions of all ECUs are depicted in figure 2.1-2.

Figure 2.1-2: ECU network of a Mercedes-Benz Model line 221 (S-Class) [Mer09]

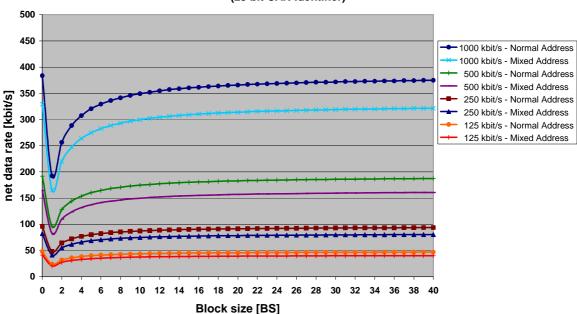

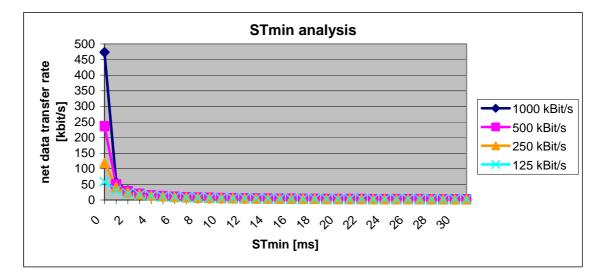

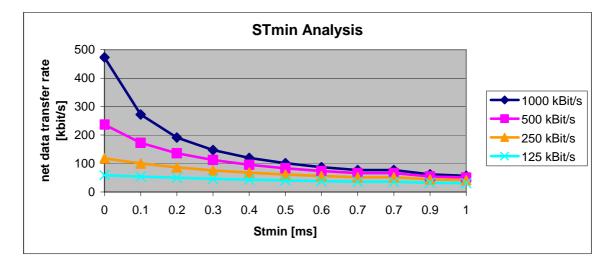

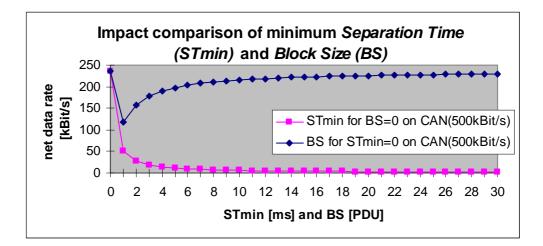

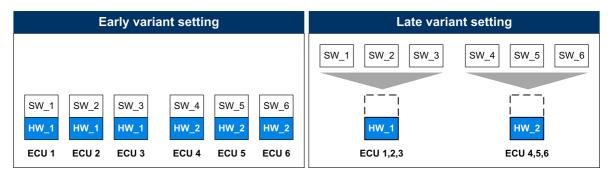

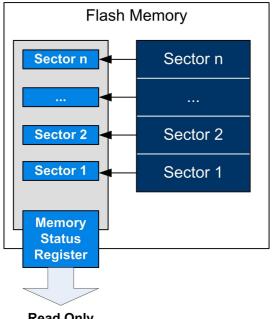

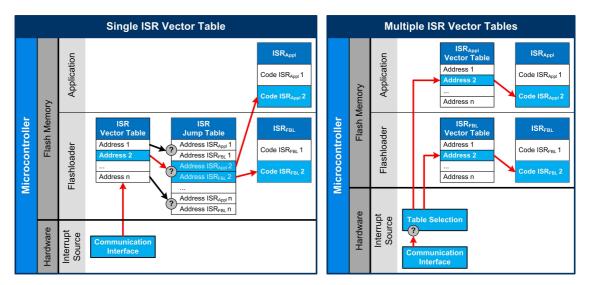

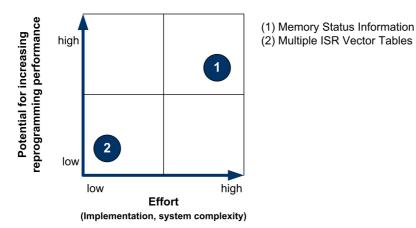

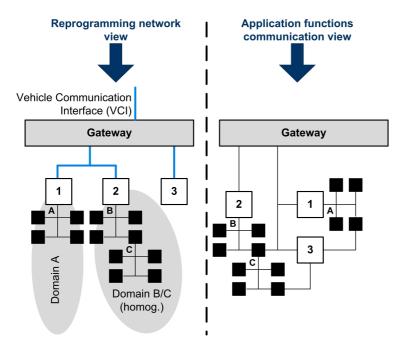

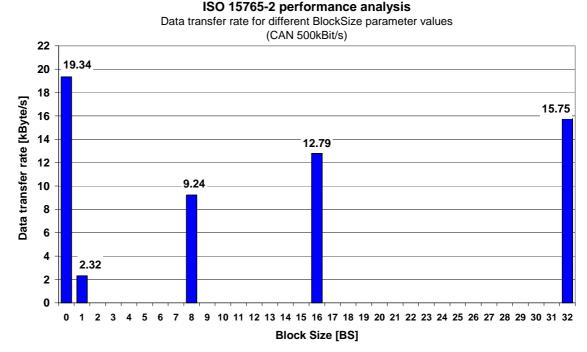

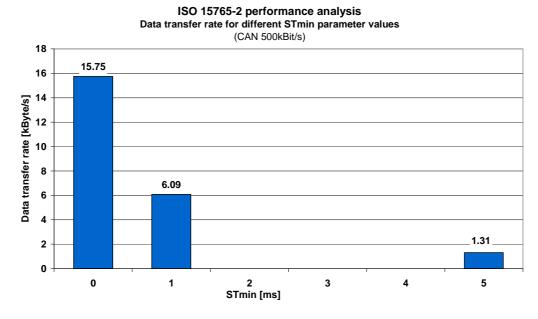

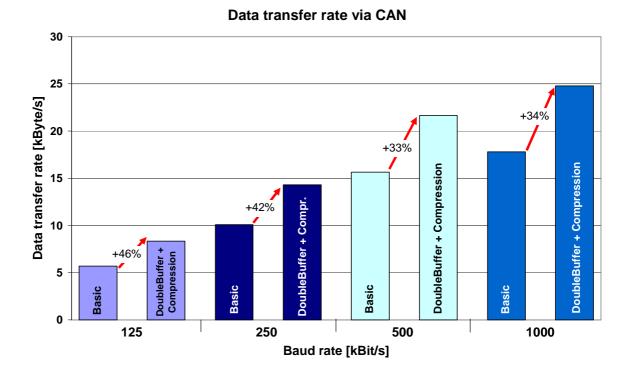

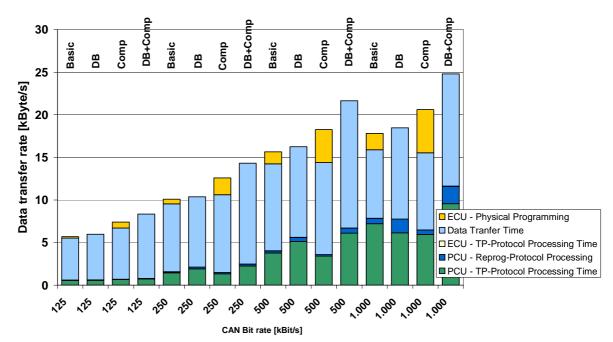

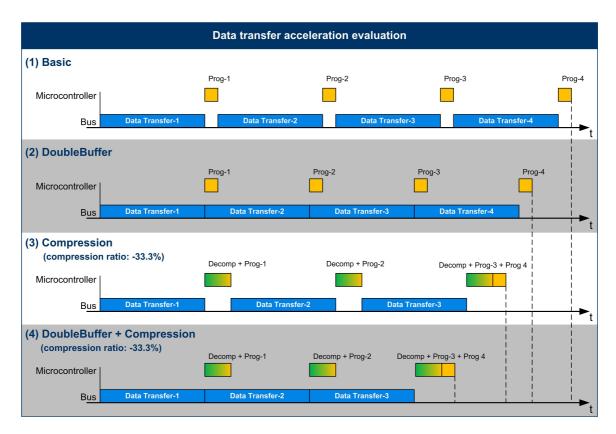

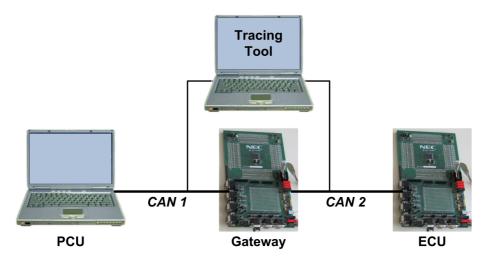

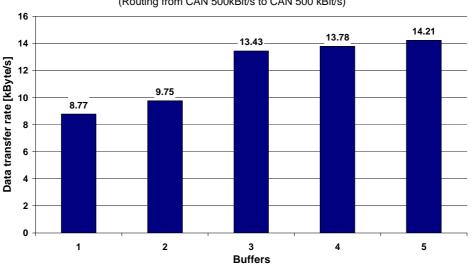

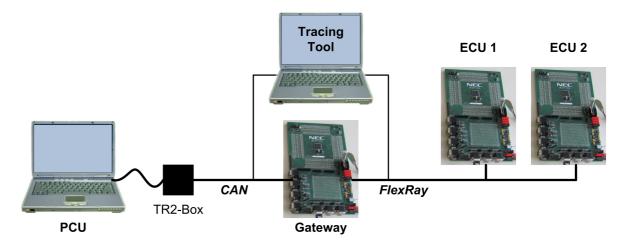

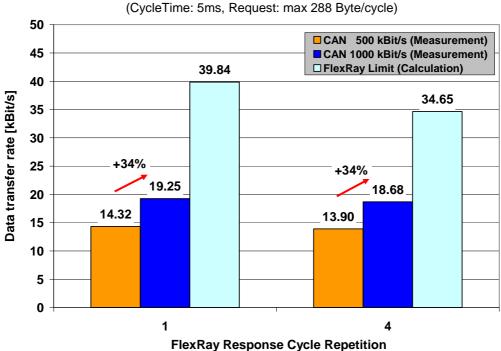

Figure 2.1-3: Mercedes-Benz Model Line 221 (S-Class) network architecture [Mer09-1]