# FACTPLA FUNCTIONAL ANALYSIS AND THE COMPLEXITY OF TESTING PROGRAMMABLE LOGIC ARRAYS

### A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

By

S. I. ABBAS (BSc., MSc.)

DEPARTMENT OF ELECTRICAL & ELECTRONIC ENG.

BRUNEL (THE UNIVERSITY OF WEST LONDON)

UXBRIDGE, MIDDLESEX, U.K., UB8 3PH

MAY 1988

#### ABSTRACT

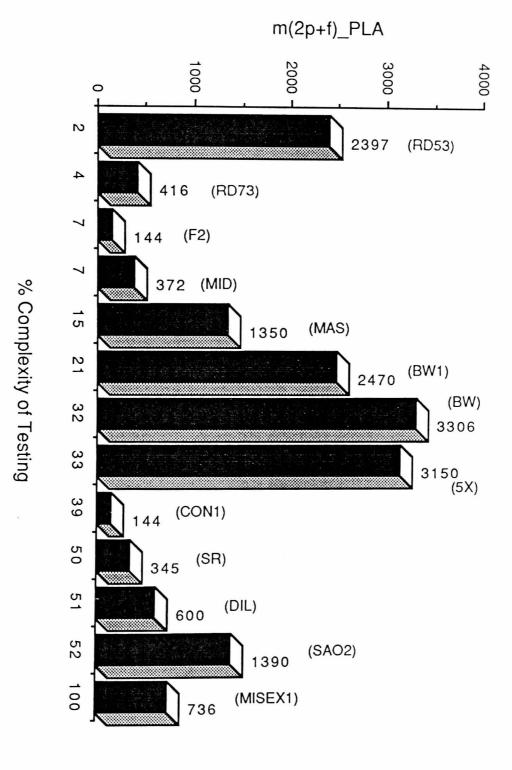

A computer aided method for analyzing the testability of Programmable Logic Arrays (PLAs) is described. The method, which is based on a functional verification approach, estimates the complexity of testing a PLA according to the amount of single undetectable faults in the array structure.

An analytic program (FACTPLA) is developed to predict the above complexity without analyzing the topology of the array as such. Thus, the method is technology invariant and depends only on the functionality of the PLA. The program quantitatively evaluates the effects of undetectable faults and produces some testability measures to manifest these effects.

A testability profile for different PLA examples is provided and a number of suggestions for further research to establish definitely the usefulness of some functional properties for testing were made.

### TO MY PARENTS, BROTHERS & SISTERS

Samir

#### **ACKNOWLEDGMENT**

I should like to express my sincere appreciation and deep gratitude to prof. G. Musgrave for his agreeing to be my supervisor and for his guidance, patience, and continuous encouragement throughout this study.

Thanks are due to Dr. T. Alukadi and Dr. M. Hadjinicolaou for their useful and stimulating discussion and to all my colleagues at Brunel 'CAD group'.

#### CONTENTS

| CHAPTER 1: INTRODUCTION                                 | 1  |

|---------------------------------------------------------|----|

| 1.1 INTRODUCTION                                        | 2  |

| 1.2 FAILURE MECHANISMS                                  | 3  |

| 1.3 TESTING PROBLEMS                                    | 6  |

| 1.3.1 Cost of Functional Testing                        | 8  |

| 1.3.2 The Effects of Undetectable Faults                | 9  |

| 1.4 TESTABLE DESIGN ISSUES                              | 11 |

| 1.4.1 Design For Testability                            | 13 |

| 1.4.2 Testability Analysis                              | 15 |

| 1.5 SUMMARY                                             | 16 |

| CHAPTER 2 : FAULT ANALYSIS IN PROGRAMMABLE LOGIC ARRAYS | 19 |

| 2.1 INTRODUCTION                                        | 20 |

| 2.2 THE STRUCTURE OF PROGRAMMABLE LOGIC ARRAYS          | 21 |

| 2.2.1 PLA Implementation                                | 23 |

| 2.2.2 PLA Folding                                       | 25 |

| 2.2.3 Impact of PLAs on Logic Design                    | 26 |

| 2.3 FAULT MODELING IN PROGRAMMABLE LOGIC ARRAYS         | 27 |

| 2.3.1 Stuck_at Faults                                   | 27 |

| 2.3.2 Bridging Faults                                   | 29 |

| 2.3.3 Crosspoint Defects                                | 33 |

| 2.3.4 The Product Term Fault Model                      | 35 |

| 2.4 TESTING PROGRAMMABLE LOGIC ARRAYS                   | 37 |

| 2.4.1 Using The PLA Logic Model                         | 37 |

| 2.4.2 Using The PLA Personality                         | 38 |

| 2.4.3 Using The PLA Functional Specification            | 39 |

| 2.5 FAULT MASKING IN PROGRAMMABLE LOGIC ARRAYS          | 40 |

| 2.6 MULTIPLE FAULT DETECTION IN PLAS                    | 42 |

|                                                         |    |

| CHAPTER 3 : FAULT MASKING EVALUATION IN PLAS        | 46  |

|-----------------------------------------------------|-----|

| 3.1 INTRODUCTION                                    | 47  |

| 3.2 PRIME IMPLICANT METHOD FOR TEST GENERATION      | 48  |

| 3.3 FUNCTIONAL LEVEL CHARACTERIZATION               | 51  |

| 3.4 REDUNDANT FAULTS IDENTIFICATION IN PLAS         | 56  |

| 3.4.1 Redundant Growth Faults                       | 58  |

| 3.4.2 Redundant Shrinkage Faults                    | 61  |

| 3.4.3 Redundant Appearance Faults                   | 66  |

| 3.5 MASKING INFLUENCES ON MULTIPLE FAULT COVERAGE   | 67  |

| 3.5.1 Masking Evaluation in a Single_Output PLA     | 69  |

| 3.5.2 Masking Evaluation in a Multiple_Output PLA . | 72  |

| 3.6 SUMMARY                                         | 73  |

| CHAPTER 4 : FACTPLA PROGRAM IMPLEMENTATION          | 75  |

| 4.1 INTRODUCTION                                    | 76  |

| 4.2 FAULT DATA STRUCTURE                            | 77  |

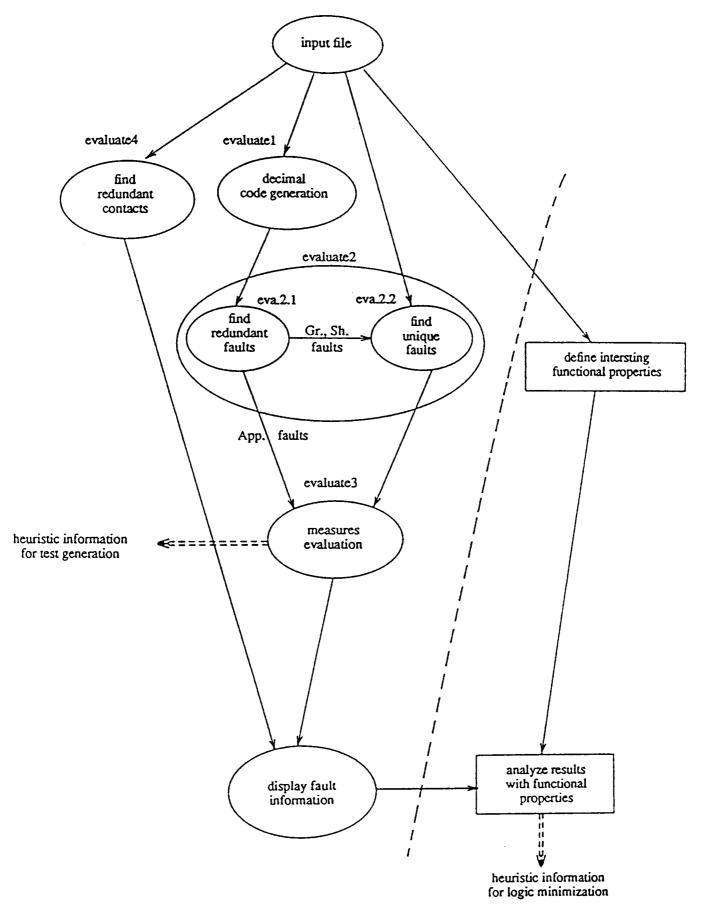

| 4.3 PROGRAM STRUCTURE                               | 78  |

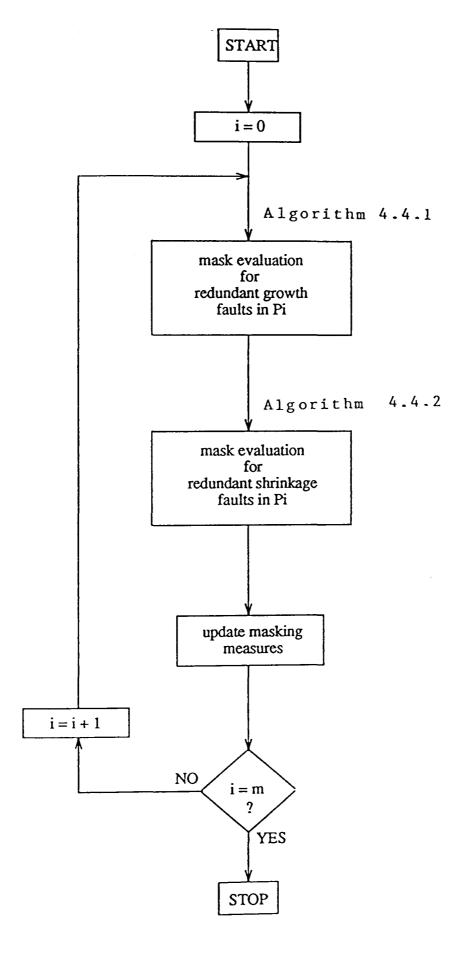

| 4.4 FACTPLA FOR A SIMPLE (n,m,1)_PLA                | 82  |

| 4.4.1 Algorithms For a (n,m,1)_PLA                  | 83  |

| 4.4.2 Application on Switching Theory               | 87  |

| 4.5 FACTPLA GENERALIZATION TO MULTIPLE_OUTPUT PLAS  | 89  |

| 4.6 EXPERMENTAL RESULTS                             | 92  |

| 4.7 SUMMARY                                         | 96  |

| CHAPTER 5 : CONCLUSIONS                             | 99  |

| 5.1 CONCLUDING REMARKS                              | 100 |

| 5.5 FUTURE WORK                                     | 102 |

| REFERENCES                                          | 105 |

| APPENDIX A                                          | 112 |

CHAPTER ONE

INTRODUCTION

#### 1.1 INTRODUCTION

rapid evolution of semiconductor The technology device densities has increased the effort towards higher to prove the design validation, manufacturing quality, and longer term operational reliability. With increasing circuit density, a vast amount of data processing storage are required to perform testing. Examples of this type indicate that a test pattern generation program could for several weeks for complex circuits like that of a Micro Vax computers. This can account for about 60% o f cost of test. It has been noticed that the best the measure of the test effectiveness has involved simulation programs; the most costly part of test preparation in Large Scale Integration (LSI) and Very Large Scale Integration (VLSI) environments. Such programs are usually based on a simple fault model for the circuit test. The cost of the test may increase to such an under extent as to regard the circuit as untestable, i.e., the generation, evaluation cost o f test pattern and application are beyond the budget.

Most automated test generation procedures assume 'single' faults, since multiple faults analysis is in general, much more complicated [1]. The reason for such complexity come from the fact that multiple faults assume some sort of signal independencies that may defeat fault sensitization required to generate the test patterns. This implies that every single fault is detected and repaired before some other fault can occur.

In practice, however, most digital circuits tend to contain various undetectable faults. Due to the phenomenon of masking among faults, the existence of such undetectable faults has a great influence on testing high scale integrated circuits.

In the following review the basic issues and problems in testing digital circuits are briefly discussed. Recent techniques to overcome the testing problem, namely design for testability and testability analysis, are also introduced.

#### 1.2 FAILURE MECHANISMS

The design of a digital system can be viewed as a sequence of transformations of design representations at different levels of abstraction [2]:

- (a) functional (informational) representation,

- (b) logic (gate) representation,

- (c) physical (circuit or geometric) representation.

Thus, when modeling a circuit malfunction, an appropriate model for the malfunction must be established at each level. This is a "failure" in the circuit level, "fault" in the gate level, and "error" in the informational level. However, for ease of computation, the fault model should possess some basic properties:

- 1. easily definable and manipulatable by computer,

- able to reflect a variety of technological failures,

and

3. able to give a satisfactory coverage of the actual failures.

In digital environments, a switching variable can have one out οf two logical values; ZERO and ONE. Hence. fault modeling is easier to handle аt the gate representation and most fault detecting techniques have adopted this policy. Accordingly, the stuck or stuck at fault model represents a typical logical fault model which is frequently considered. In this model, an arbitrary signal line k in the circuit is assumed to be fixed permanently at either logical 0, k stuck at ZERO (k S@ 0), or logical 1, k stuck at ONE (k S@ 1).

For testing purposes, <u>single</u> stuck at fault model, in which the circuit is assumed to contain at most one stuck fault, is widely used. More complex gate\_level fault models are the multiple stuck and bridging faults. In the multiple stuck fault model, it is assumed that signal lines can have values that are fixed and independent of the other signals in the circuits. The bridging fault model assumes that two signal lines are connected together so that a wired logic occurs.

However, the above classes of gate\_level faults have some drawbacks [3]:

there are many switch\_level faults which do not fall into these classes. Some switch\_level shorts and opens can not be modeled by many gate\_level faults because they involve a modification of the function realized by the relevant logic diagram.

- 2. the logic diagram does not always constitute a real model of the circuit diagram. For instance, in MOS technology many stuck\_at faults in a gate\_level representation of a MOS device do not correspond to any physical failures of interest.

- 3. with increasing circuit density, logic\_level representation results in large number of component blocks. Also, when considering bi\_directional switches then as many as 15 logic levels have to be considered. The complexity of testing and the number of test patterns will increase accordingly.

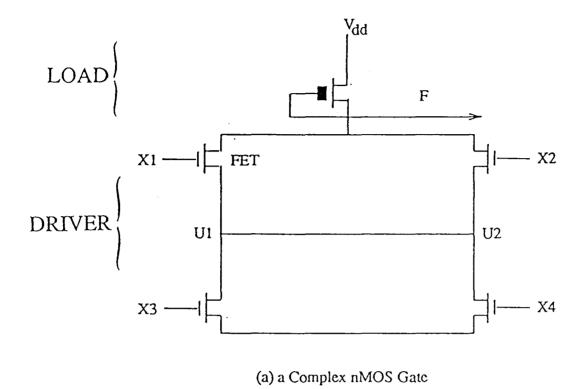

Figure 1.1 illustrates a failure that can not be modeled as a stuck fault. The nMOS complex gate given in Figure 1.1 consists of a LOAD and a DRIVER. If the input to a Field Effect Transistor (FET) is logic 1, then a conducting path between its other leads exists. Otherwise, these leads do not conduct. If, due to some input assignment, a conducting path between the output of the gate and ground exists, then the output of the gate is at logic ZERO. However, if there is no such path, then the depletion transistor in the LOAD section of the gate will pull up the output to  $V_{\rm dd}$  (logic ONE). Obviously, there are 4 possible conducting paths which may force the output to logic ZERO.

Now, if the permanent connection between Ul and U2 in the above gate is broken for some reason, then only two conducting paths remain, i.e.,  $F = \frac{X_1X_3}{1^3} + \frac{X_2X_4}{2^4}$ . This faulty function does not correspond to any stuck fault

(b) original function

(c) modified function

Fig. 1.1 Effect of Circuit \_level Faults

in the equivalent logic diagram of the gate.

Accordingly, fault models, other than stuck and bridging faults, have gained popularity. Current efforts are being directed towards modeling failures at both switch functional levels. An advantage of testing switch level failures is that in some cases it may be possible utilize structural properties (regularity, for the instance) of the circuit to obtain a much simpler test set compared tο the one generated to the gate level representation. However, testing switch level failures involves a much greater amount of complexity. On the other hand, functional level fault models help reduce complexity of testing highly dense circuits. In this case, a very accurate fault model is required so that it can reflect the interconnection structure of the transistor circuit.

#### 1.3 TESTING PROBLEMS

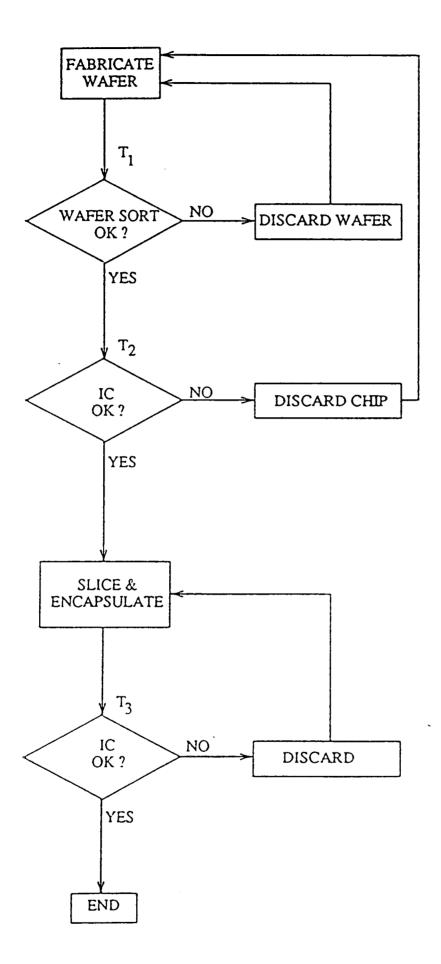

In today's technology, the Integrated Circuit (IC) chip represents the smallest physical element which has to be considered in the manufacturing environments. At the end of the IC fabrication process, the wafer disk (approximately 75mm in diameter) is containing many copies (called die) of the IC arranged in a rectangular matrix. Typically, only a minority, perhaps 30%, of these copies work properly. Hence, the actual step of testing begins at the fabricated wafer [4]. Figure 1.2 shows a simplified flow chart for testing the ICs. Test Tl is performed to

Fig. 1.2 IC Manufacturing & Testing

check whether the fabrication process has been carried out satisfactory.

Having established that the wafer contains an acceptable percentage of good circuits, the actual copies must now be tested (test T2) on wafer. Three different types of IC testing can be recognized:

- 1. wafer sort : each IC on the wafer must be tested to identify the good circuits,

- 2. parametric testing: parameters such as propagation delay and drive currents are checked, and

- 3. <u>functional testing</u>: determine whether or not the IC carries out the function for which it was designed.

Due to access limitations on wafer, parametric and functional testing are restricted at this stage. Hence, the IC must also be tested after it is packaged (test T3), after it is mounted on a board, and perhaps periodically after it is placed in a system. However, among these, functional testing has been shown to be the most expensive part of the process. As the technology progresses towards high levels of integration, the ratio between the number of devices on a chip to the chip input/output pins increases considerably. Such chip 'complexity' has caused a rapid increase in the cost of performing functional testing.

In the following, the problems involved in testing digital circuits are presented in terms of two parameters; the cost of functional testing and the effects of undetectable

faults.

#### 1.3.1 Cost of Functional Testing

The basic procedure of functionally testing digital circuits involves three main activities [5]:

- 1. Test Pattern Generation (TPG): deriving and selecting a set of input stimuli which is either 'exhaustive', 'random', or 'algorithmically' generated.

- 2. Test Pattern Evaluation (TPE): justifying the effectiveness of the test patterns using one of two different techniques; <u>fault simulation</u> and fault insertion.

- 3. Test Application and Fault Finding (TAFF): applying the test pattern to a real circuit by means of sophisticated Automatic Test Equipment (ATE).

Accordingly, the cost of testing digital circuits may be divided into:

- 1. TPG cost: relates to one of two parameters

- (i) the computer time required to run the TPG program plus the capital cost of developing the program (automatic),

- (ii) the number of man hours required for a person to write the test pattern plus the increase in system development time caused by the time taken to develop the tests (manual).

- 2. TPE cost: depends mainly on fault simulation techniques. Such techniques require an accurate model

of the circuit under test and repeated evaluation of circuit signals for each fault taken from the fault list. It has been proved that fault simulation run times represent the most considerable contributor to overall testing cost [5].

#### 3. TAFF cost: depends on

- (i) the cost of Automatic Test Equipments and their interface requirements for different types of circuits,

- (ii) the tester time required to apply the test.

The Automatic Test Equipments have become very expensive and the computing time required to calculate the input patterns to be applied to the circuit has become very costly.

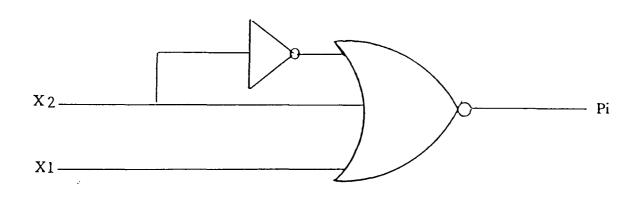

#### 1.3.2 The effect of undetectable faults

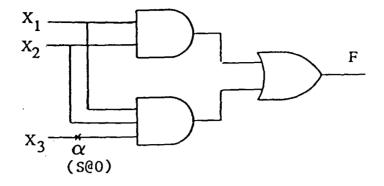

A digital circuit is said to be redundant with respect to some fault if the fault is undetectable, i.e., the function realized by the circuit with the fault present is equal to the function realized by the circuit without the fault [1]. In sketch (a) of Figure 1.3, the fault  $\alpha$  S@O (or S@I) is not testable since the output F is equal to logic 'ONE' if and only if  $\alpha_1 = \alpha_2 = 1$  regardless of whether this fault is present or not. Most testing methods are based on the assumption that the network under test is irredundant. Therefore, a great amount of computation may be wasted in trying to find tests for undetectable (or redundant) faults. Beside, the existence of undetectable faults in any circuit has a great influence on two of the

(a) Undetectale fault  $\alpha$

(b) Fault  $\alpha$  Masks Fault  $\beta$

(c) Direct Graph Representation

Fig. 1.3 Illustrations of undetectable Faults in Digital Circuits

most important aspects in functional testing:

#### (i) Fault Masking

In a general digital circuit, a non\_detectable fault may mask the detection of a normally detectable fault for a given test pattern. An example of fault masking is shown in sketch (b) of Figure 1.3. The fault  $\alpha$  (S@1) is undetectable at the output node F because of the inconsistent assignment at inputs  $X_1$ ,  $X_2$ , and  $X_3$ . The fault  $\beta$  (S@0) is detectable at F by the input test  $\beta$  (110), which is the only test available for this fault. However, the presence of  $\alpha$  (S@1) prevents (masks) the detection of  $\beta$  (S@0). The above masking phenomenon is defined below:

Definition 1.3.1. A redundant fault  $f_i$  masks a testable fault  $f_j$  under the test T if and only if T detects  $f_i$  but does not detect the combined fault  $f_i$ .

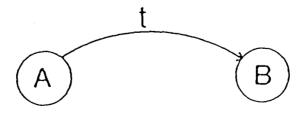

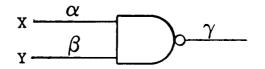

Fault masking phenomenon may also be described by a direct graph (see sketch c of Figure 1.3). Generally, each node in the graph represents a fault (single or multiple) and an arc goes from node A to node B with label t if fault A masks faults B under test t, i.e., B is detected but AB is not. If the 'masking graph' is designed for a given test set, i.e., a complete single fault test set, the labels of its arcs may be omitted [29]. Note that fault masking may occur in irredundant circuits as well. As an illustration, consider the following NAND gate:

The test "X=0, Y=1" detects the single fault "line  $\alpha$  S@1". If  $\alpha$  S@1 and  $\gamma$  S@1 are both present, then the above test will not detect the fault  $\alpha$  S@1. This masking is not a problem as the test "X=1, Y=1" detects the fault  $\gamma$  S@1.

Nevertheless, in a general combinational circuit, the existence of loops of successively masking faults is greatly affects the ability of single fault test sets to cover multiple faults as well.

#### (ii) Multiple Fault Detection

In a general digital circuit, there are many more multiple faults than single faults. A circuit with k lines may contain up to (3<sup>k</sup> -1) possible multiple faults [1]. Accordingly, the consideration of various multiple faults would be extremely impractical. on the other hand, the single fault model does not accurately cover various failures which can occur in highly dense circuits. However, previous research on multiple faults has come to the assumption that a complete single fault test set also detects most of the multiple faults [1]. The validity of this assumption is greatly affected by the amount of undetectable faults and the possibility of fault masking occurrence.

#### 1.4 TESTABLE DESIGN ISSUES

Undoubtly, the discussion given in the last section has indicated that it is not enough just to design a circuit, after it is built it has to be tested easily. Furthermore, it has been justified that testing costs

contribute considerably (50% - 60%) in overall product cost. Current trends for increasing circuit density have significantly decreased system hardware cost. The implication of such trends had led to a situation in which:

- testing is becoming more difficult since the number of pins per IC is not increasing in proportion to the number of gates per IC. Thus, the ability to 'control' and 'observe' signal values for the logic on chip is reduced, and

- 2. the percentage of system cost due to testing is increasing drastically.

It appears, therefore, that the only economical method to reduce testing costs is to include circuitry on each chip to facilitate testing. The expenditure, in the design stage, of adding such circuit overheads will result in overall reduction in cost. Two key concepts are involved in all strategies of designing testable circuits; controllability (a measure of the ability to set and reset every node internal to the circuit), and observability (a measure of the ability to observe the state of any node in the circuit). These circuit attributes reflect the degree of circuit testability. However, there exist two main techniques which relate to circuit testability:

Design For Testability (DFT): addresses the testing problem during design by building testability in the circuit by design, and 2. Testability Analysis: a DFT method that approximates the difficulty of testing before generating the test patterns.

#### 1.4.1 Design for testability

These techniques improve control and observation properties of the digital circuits. They may be divided into two main categories:

- Ad Hoc: directed towards correcting specific design 1. features that create testing problems. The most direct way to do this is to introduce test points, that is, additional circuit inputs and outputs to be used in the testing mode. These points allow the internal signals to be controlled and observed during testing. Such technique is seen to be specific and not generally applicable to VLSI and WSI due to the IC pin limitations. On the other hand, it has been estimated that the complexity of test pattern generating and fault simulation is proportional to the number of logic gates to the third power [7]. Therefore, the partitioning of large circuits and the individual testing of the sub circuits should reduce the overall testing cost. However, this method still unhelpful if the sub circuits contain many memory devices which require initialization.

- 2. <u>Structured</u>: applying a set of design rules which are generally applicable. Basically, these techniques have been introduced to control and observe the

devices, therefore, the test generation memory problem could be reduced to the one of just testing the combinational logic. Scan techniques (Scan Path, Scan Set, Random Access Scan, and Level Sensitive Scan Design LSSD) permit access to internal nodes of circuit without requiring a separate external connection for each node accessed. Scan Path is the most recognizable approach to describe the concept of these techniques. In the testing mode of Scan Path circuits, all registers or flip flops are converted into shift registers and connected as scan path for shifting in test patterns and shifting out test responses to a tester. The IBMLSSD uses this approach. However, due to the nature of serial transmission this approach involves a time delay for applying the tests and receiving the responses. Furthermore, expensive test equipments and storage for a large number of test patterns and responses are required. Alternatively, Built in Self Testing (In Chip Tester or Built in Logic Block Observation) uses some silicon area to eliminate the disadvantages associated with Scan techniques. On the other hand, this method suffers many drawbacks. For instance, the extra silicon area devoted for the test circuitry reduces reliability and computational capacity of the chip, as well as efficient automated test procedure is required. A review of most DFT techniques is well presented in a paper by Williams and Parker [7] .

#### 1.4.2 Testability Analysis

Having established the philosophy that additional overheads and general design constraints are very significant in the design method, it is vital that the designer has all the necessary information to make his design judgments. For instance, it is desirable to limit "extra additions" to those necessary to insure the adequate testability of the design. Therefore, a need for a 'testability measure' has become widespread. It is easy to argue that the use of an Automatic Test Pattern Generation (ATPG) program may provide a measure for the circuit testability. For example, parameters such as time of the program, the number of test patterns, and the fault coverage may constitute the above measure. However, two difficulties are associated with such direct approach:

- the large expense involved in running the ATPG program, and

- 2. the lack of information about how to improve the testability of a circuit with poor testability measure.

Alternatively, testability analysis programs have been developed to estimate the design testability by predicting the cost (running time) of generating the test patterns. These programs tend to quantify the circuit properties of controllability and observability prior to determine its testability without actually running any ATPG program.

THERES (Rescability Measure Program [8]), SCOAP (Sandia)

Controllability Analysis Program [9]), TESTSCREEN [10].

VICTOR (VLSI Identifier of Controllability, Testability,

Observability, and Redundancy [11]), and CAMELOT (Computer

Aided Measure for Logic Testability [12]) are the most

popular testability measure programs.

#### 1.5 SUMMARY

In the light of the above discussion, the very scale digital circuits make testing extremely difficult, and when test patterns can not be obtained within allowed computation time, it will be difficult to achieve a high rate of test coverage. Furthermore, multiple fault coverage must also be adequate since these faults represent an important parameter in VLSI environment. Testability analysis programs have been offered solutions to the problems of test complexity and coverage. The information obtained by such programs may be used to develop some design constraints for achieving easily testable designs. For instance, advance knowledge of all redundant faults and their masking influences could used to estimate the complexity of testing, multiple fault coverage capability of a single fault test set and, hence, of testability for a given digital circuit. t he degree Clearly, the philosophy behind any test strategy may serve systematically obtain such knowledge. Functional testing of 2\_level AND\_OR networks seems to be very attractive in this context.

The above concept represents the theme o f the work established in this thesis as applied to programmable logic arrays; one of the most popular structures in VLSI design. FACTPLA (Functional Analysis and the Complexity of Testing PLAs) is a fast, compact and systematic program which has been developed to identify redundant faults and quantify their masking effects in general PLAs. contact fault model has been adopted as it represents the most dominant failure model in these arrays. The program also indicates the way with which more realistic test patterns may be chosen for a PLA, i.e., which should be included in the test set in order to cover as many multiple faults as possible.

Chapter 2 of this thesis introduces PLAs, as an increasingly powerful tool for LSI and VLSI design. Various types of faults that are apt to occur in a PLA are analyzed and the contact fault model is justified. A brief review of the previous strategies for testing PLAs is also discussed.

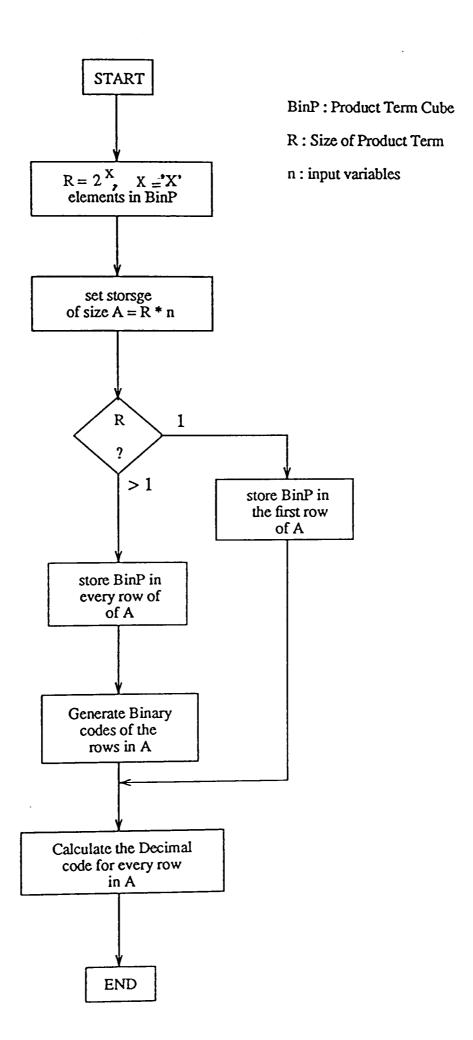

The theoretical strategy for the FACTPLA program is presented in Chapter 3. The method of prime implicant testing of irredundant 2\_level AND\_OR networks, as suggested by Kohavi [13], is elaborated prior to analyze the effects of undetectable faults in a PLA. This is analyzed and based upon the functional specification of a PLA (as a set of product terms), therefore generating testability criteria for the array structure. A simple hueristic is used by adopting the decimal code of the

product term as an ordered set of minterms. The policy of choosing the realistic tests for detectable faults is also justified.

Chapter 4 presents the implemented FACTPLA algorithms for predicting the impact of redundant contact faults on difficulty of testing the PLA. The applications and complexity of such algorithms are also discussed.

Suggestions to direct a future research towards deriving a more testable PLA structure and generalizing the applications of the FACTPLA program are summarized in Chapter 5.

## CHAPTER TWO AULT ANALYSIS IN PROGRAMMABLE LOGIC ARRAYS

#### 2.1 INTRODUCTION

Considerable technological achievement over the last few years has produced an increasing level of integration of components onto a single Integrated Circuit (IC) chip. Very Large Scale Integration (VLSI) plays a major role in the development of complex digital systems.

Standard ICs have been produced tο meet several requirements of both simple combinational circuits and the complex sequential networks. more There are applications, however, that require a circuit which is not available in standard IC form. The concept of custom or semi custom design has been introduced provide flexibility and easy design changes. Ιn practice, different digital semi\_custom ICs can be classified as belonging to one of the following main groups [2]

- (i) Gate Arrays (or Uncommitted Logic Arrays, ULAs)

- (ii) Cell Based Systems

- (iii) Programmable Logic Devices ( Matrix Logic)

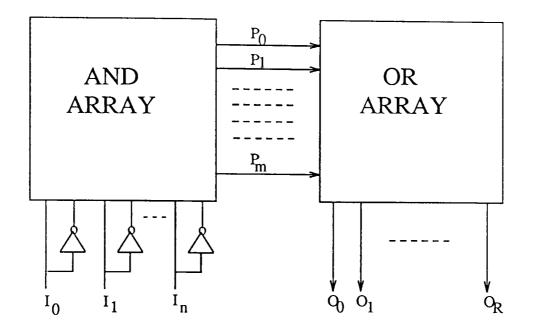

Programmable Logic Devices basically capable are o f implementing arbitrarily complex logic functions in sum of products (SOP) forms. Depending on the manufacturer, best known examples of these devices are the familiar PROM Only Memory) FPLA (Programmable Read and Programmable Logic Array). Recently, PAL (Programmable Array Logic), FPGA (Field Programmable Gate Array) FPLS (Field Programmable Logic Sequencer) have been introduced and added to the category of these devices.

Figure 2.1 represents an overall architecture which summarizes the comparison between PROM, FPLA and PAL. It is obvious that all these devices perform similar logic functions, the differences are determined by whether the AND matrix, the OR matrix or both are programmable.

#### 2.2 THE STRUCTURE OF PROGRAMMABLE LOGIC ARRAYS

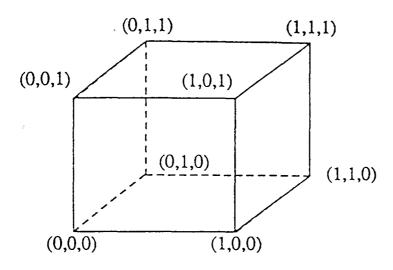

Basically, the PLA is a logical element designed to produce sum of products expressions. It allows more efficient use of the silicon area by representing a set of logic functions in a compressed yet regular form. A PLA implements a two stage combinational logic through a pair of adjacent rectangular arrays. Thus, conceptually a PLA may be viewed as a collection of 2\_level AND\_OR or NAND NAND or NOR NOR networks.

The PLA is an important building block for VLSI circuits. is commonly used to design instruction decoders of Ιt microprocessors, and combinational circuitry finite state machines. The key technological advantage of using a PLA in an IC technology relies on the straightforward mapping between the symbolic representation and its physical implementation. combinational logic function can be described by a logic cover. For PLAs this logic cover is represented by a matrices, called input and output matrices. o f symbolic \_ physical mapping is obvious in Figure 2.2. this Figure, each input variable of the logic function is represented by a column in the input matrix in sketch (a).

(a) PROM: AND array pre\_programmable. Fully decoded n inputs yield to all m = 2 possible product terms.

OR array user\_programmable. Any combination of the

m products can be ORed onto one of the R outputs.

(b) FPLA: AND array user\_programmable. Generate a chosen products of m (<2) products from n inputs.

OR array user\_programmable. Any combination of the n products (<2) can be ORed onto one of the R outputs.

(c) PAL: AND array user\_programmable. Generate a chosen products n of m (<2) products from n inputs.

OR array pre\_prograamble. Groups of products are ORed onto the R outputs according to a pre\_arranged pattern.

Fig. 2.1 a Comparison of Programmable Logic Devices

In sketch (b) of Figure 2.2, each variable corresponds to a pair of columns in the left part of the physical implementation. Every implicant of the logic function is represented by a row in the symbolic representation. The input part of each row represents a logical product of some input variables. Finally, every output of the logic function corresponds to a column in the right part of the physical array.

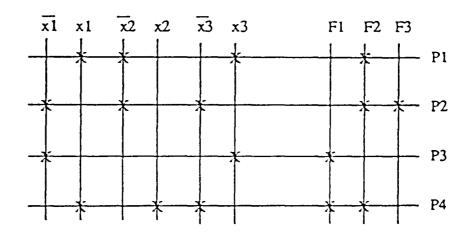

The implementation of a particular logic function performed by "programming" the PLA, i.e., by placing (or connecting) an appropriate device at the intersection points (between the rows and columns) specified by 'l' or 101 in the symbolic representation. The grid (intersection) points between the input/output columns and the product lines (rows) are called crosspoints. part of the PLA structure shown in Figure 2.2(b) is called the SEARCH or PRODUCT TERM array, while the right part READ or SUMMING array. A cross (contact) in the called the presence of an the SEARCH array represents variable (uncomplemented or complemented) in the relevant product term, while a cross in the READ array represents the presence of a product term in some output function. Accordingly, every PLA will have specific personalities fusible links) which define the overall structure personality.

(a) A Simple PLA (Symbolic)

(b) the PLA Representation

Fig. 2.2 Symbolic\_Physical Representation in PLAs

PLAs are sized or specified by the following description  $n \; * \; m \; * \; p$

where

n : number of input variables,

m : total number of unique p\_terms,

p: number of output functions.

Thus, in a general (n,m,p)\_PLA structure, there are m(2n+p) crosspoints.

Partitioning the inputs to a PLA is performed with the aid of a Bit Partitioning Network (BPN). Single and Double decoders are the most common BPN used in PLAs [6].

#### 2.2.1 PLA Implementation

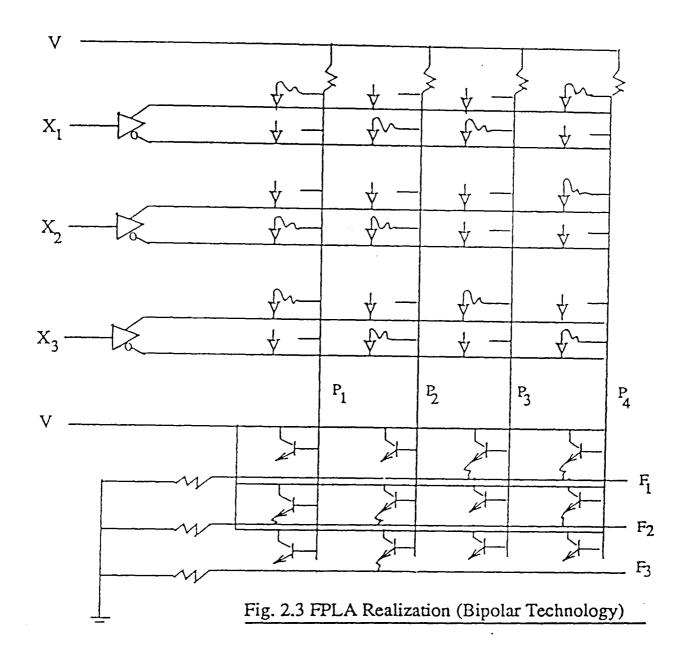

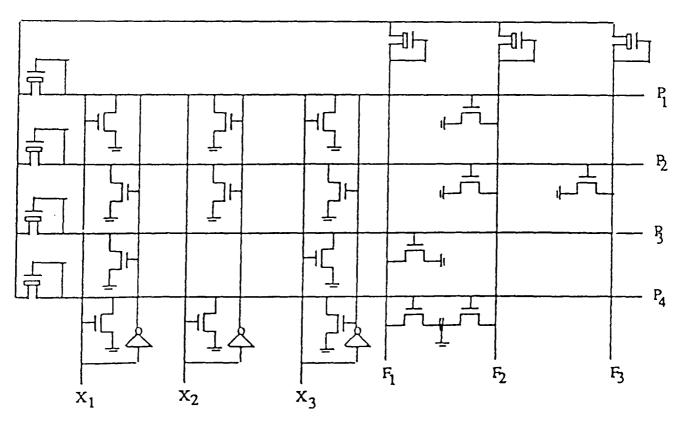

PLAs are compatible with different technologies. For example, in the AND\_OR bipolar transistor implementation, the AND matrix is implemented with diodes, and the OR matrix is implemented with bipolar transistors. This provides the designer with the ability to program his array by blowing fusible links within the array.

In another fabrication method, the implementation is possible with MOSFET technology where the presence or absence of gate connections define the function realized. This is the case with NMOS technology where NAND gates can be made as well as NOR gates. However, in MOS technology, it is convenient to exploit the use of NOR gates rather than NAND gates (in terms of performance and ease of design). Thus, the NOR\_NOR NMOS PLA implementation is most common in VLSI MOS circuits [2].

However, a simple schematic diagram (identical to the physical representation) has been adopted to represent the PLA implementation of switching functions. For instance, the bipolar FPLA realization and the MOSFET implementation of the PLA shown in Figure 2.2 is illustrated in Figure 2.3 and 2.4 respectively.

For fault analysis and test generation purposes, the personality of a PLA has been defined using two different procedures for input and output columns [14]. In other words, the functionality (personality) of a PLA can be represented by a 0 l matrix defined as follows:

definition 2.2.1 given a row and an "output" column in a fault free PLA, if there is a cross between the two (or, there is no cross), then a 1\_contact (correspondingly, a 0\_contact) is said to exist between the row and the column.

definition 2.2.2 given a row and an "input" column in a fault free PLA, if there is a cross between the two (or, there is no cross), then a 0\_contact (correspondingly, a l\_contact) is said to exist between the row and the column.

The personalized crosspoints between input lines and rows will be referred to as <u>input contacts</u>, while the personalized crosspoints between output lines and rows will be called <u>output contacts</u>.

Fig. 2.4 nMQS NOR\_NOR PLA (MOSFET Technology)

The personality matrix for the PLA structure shown in Figure 2.2 is given below:

| _ | $\bar{x}_1$ | х<br>1 | $\bar{x}_2$ | х <sub>2</sub> | $\bar{x}_3$ | х <sub>3</sub> | F 1 | F 2 | F 3 |   |

|---|-------------|--------|-------------|----------------|-------------|----------------|-----|-----|-----|---|

|   | 1           | 0      | 0           | 1              | 1           | 0              | 0   | 1   | 0   | • |

|   | 0           | 1      | 0           | 1              | 0           | 1              | 0   | 1   | 1   |   |

|   | 0           | 1      | 1           | 1              | 1           | 0              | 1   | 0   | 0   |   |

|   | 0           | 1      | 1           | 0              | 0           | 1              | 1   | 1   | 0   |   |

## 2.2.2 PLA Folding

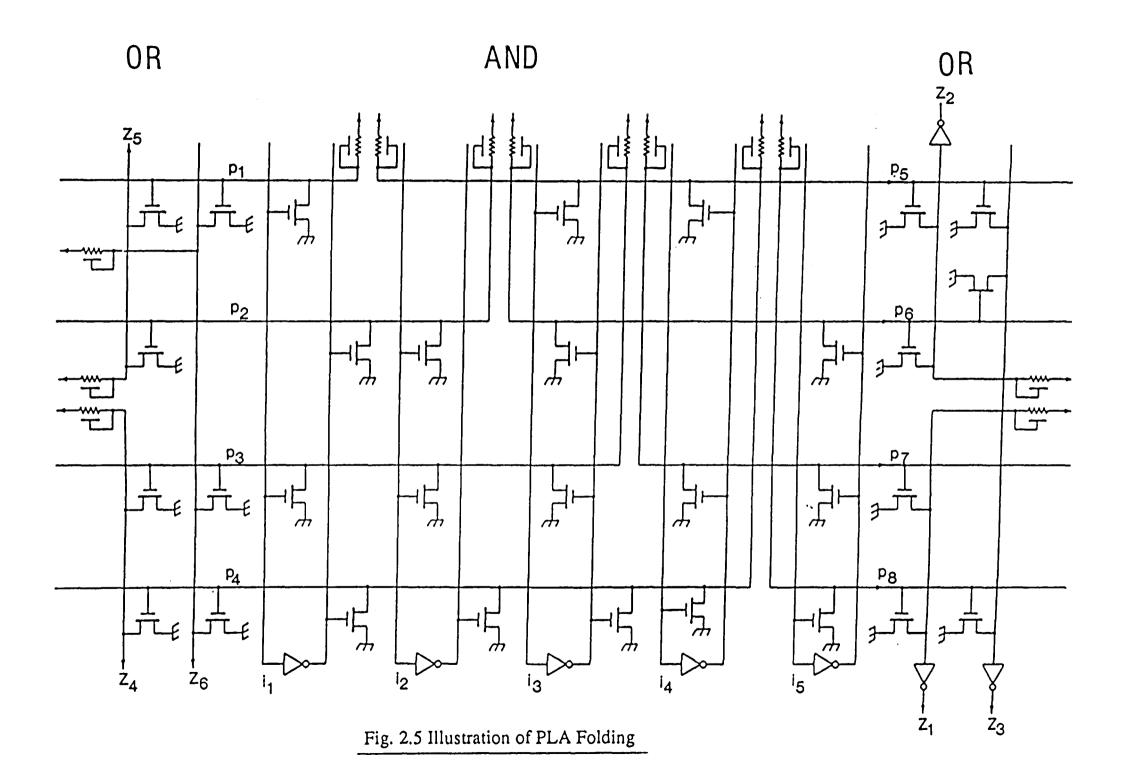

Being general purpose and programmable, the PLA is not always a dense layout for specific functions. Most PLA personality matrices are very sparse, so that a straightforward mapping to physical design will result in a significant waste of the silicon area. It is possible to recover some of this lost area by topological manipulation of the array. This kind of manipulation is known as "folding", but it has the disadvantage of reducing the permutability of the inputs and outputs at the same time as reducing the area [2].

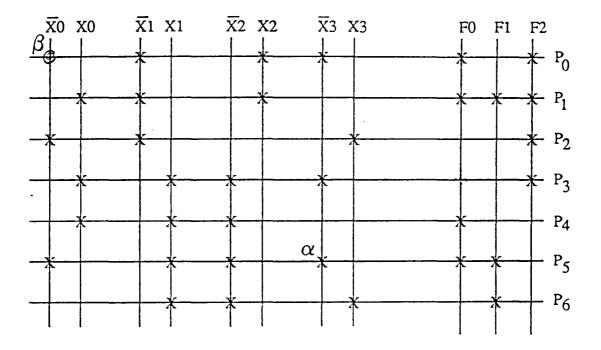

Row and column folding of a PLA are techniques which attempt to reduce the area by exploiting its sparsity. Figure 2.5 shows a 5\_input, 6\_output, 8\_product terms PLA using an 'equivalent' area for a 5\_input, 4\_output, 4\_product terms PLA plus six pull\_ups. It is easy to realize that the OR plane is folded on both sides of the AND plane which is situated in the middle. All rows and some columns have been split to allow for more product

terms and output functions, thereby resulting in a denser PLA. It should be noticed, however, that the realization of such structure imposes certain decomposability properties on the output functions. For example,  $Z_2$  does not depend on inputs  $i_1$  and  $i_2$ ;  $Z_5$  is independent of  $i_3$ ,  $i_4$ ,  $i_5$  and so on. Therefore, the design of compact PLA structures requires very complex decomposability and functional separability algorithms.

### 2.2.3 Impact of PLAs on Logic design

In additional to cost effectiveness and optimum memory features, PLAs introduce some other design advantages:

## l. Fast and smaller system design.

The design and implementation time can be reduced considerably due to the programmability and flexibility of the arrays.

### 2. Easy design changes - edit flexibility.

The uncomplemented or complement values of any input variable may be selected by some programming method. However, if both values are programmed (selected) in a product term, this term will never be selected since  $X.\bar{X}=0$ . In FPLAs, the above feature may be used to deactivate (remove) any previously programmed product term. Moreover, unprogrammed inputs represent don't care assignment, therefore additional input variables can be added to the old product term at any time by programming the desired don't care conditions. Also, a sum of products expression can be availabled by adding new product terms. This can be

done by further a programming process in the OR plane of the PLA.

### 2.3 FAULT MODELING IN PROGRAMMABLE LOGIC ARRAYS

When testing digital circuits, most of the physical failures are modeled at different description levels using various types of fault models. For the analysis of faults in PLAs, the simple schematic diagram shown in Figure 2.2, is used. In that Figure, stuck at faults, shorts, and crosspoint defects are the most likely fault behavior to occur. In the rest of this section, the relationships among these faults are presented prior to justify the validity of crosspoint defects as the basic fault model for PLAs.

## 2.3.1 Stuck at Faults

With this fault model, one of the lines in the PLA is stuck permanently to one of the two logic values; it is commonly caused by a short to ground or to power.

Depending on the type of the implementational circuitry, the effect is considered as one or more lines of the equivalent logical model being stuck at 0 (S@O) or stuck at 1 (S@1). For example, for a PLA constructed with NOR technology, the value on a product line (or on an output line) is a NOR function of all the devices (contacts) on it. Thus, all stuck at faults in a general PLA structure can be represented by three fault categories in the equivalent 2\_level NOR\_NOR network. These fault categories are described below:

## (a) Stuck at faults on input (bit) lines.

One of the input leads of the NOR gates in the first level is stuck at logic ZERO or logic ONE. The number of inputs to each NOR gate in this level is determined from the personality of the relevant product line in the search array. For fault detection purposes, only input lines S@O of the NOR gate have to be considered [1].

In Figure 2.2, if an input line L is stuck at ZERO with only one contact on it, then a literal corresponding to this contact must have belonged to some product line P. Accordingly, P may be activated by a proper input stimuli and, hence, the effect of the S@O fault will be equivalent to the missing contact between lines L and P. Therefore, the fault can be sensitized and the effect is propagated through one of the outputs containing P.

On the other hand, if there exist more than one contact on L, then L S@O fault will be equivalent to a multiple contact fault whose components are all single missing contact faults on the same input column. These fault components are equivalent to single S@O faults occurring simultaneously at the same logic level. It is well known that stuck at faults can not mask each other if they occur at the same logic level [16]. Therefore, the above fault is still detectable. However, if L has no contacts on it, then no sensitive path exists, and the fault is redundant.

## (b) Stuck at Faults on product (word) lines.

These faults are considered as stuck at faults on the input leads of the NOR gates in the second logic level.

It is obvious from the previous discussion that a fault of this type is equivalent to some crosspoint defect where a contact at the crosspoint is missing.

## (c) Stuck at Faults on output (function) lines.

In this case, both S@O and S@l faults must be considered. The faults are equivalent to missing and extra contact faults along the faulty output line. However, in a single output PLA, the output line has contacts on all its crosspoints with the product lines. Thus, all tests for the missing of these contacts cause the output line to have logical value O. Accordingly, an output line S@O fault is not guaranteed to be detected by such tests.

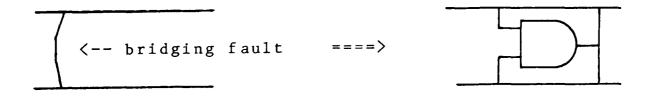

## 2.3.2 Bridging Faults

This is a short between two adjacent or crossing lines of the PLA. The commonly used stuck at fault fails to model logic circuit shorts [15]. Bridging faults are defined to model these circuit malfunctions. When two neighboring lines are connected accidentally, a wired logic is performed at the connection. Since there are two types of wired logic functions, namely the wired logic AND and the wired logic OR, therefore, there are two types of Bridging faults. For instance, in NMOS technology, an AND function between the shorted lines occurs:

Since most logic circuits are built by one of the logic families, only one type of bridging fault, either AND or OR will be considered at a time. However, if the shorted lines have the same personality then the resultant fault effect is undetectable since both lines assume the same logic value. Nevertheless, such fault has no influences on the functional operation of the circuit and, hence, the short is not important. Therefore, the key factor for investigating the effects of shorts is to assume different logic values on the affected lines. The set of all possible shorts in a PLA structure may includes the following:

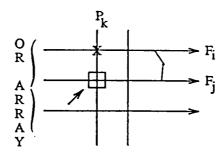

## (a) shorts between output lines.

The short is testable if there exist a device at the crosspoint between one of the shorted lines and one of the product lines, say  $P_k$ , such that no device between  $P_k$  and the other shorted line:

Any test pattern detecting the extra contact defect at the crosspoint between  $P_k$  and  $F_j$  is qualified to detect the short under consideration. Depending on the implementational circuitry, the short is detected on output  $F_i$  (ORed short) or on output  $F_j$  (ANDed short).

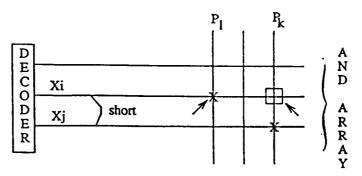

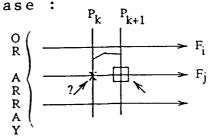

(b) shorts between input lines (one or two decoders). Let  $X_i$  and  $X_j$  be the two shorted lines, then with a single decoder: only one of the input lines has logic value ONE (decoder output):

If  $X_i = 1$ , then two possible cases may be considered:

- (i)  $X_j$  becomes logical ONE (ORed short). Hence, the short is detected by a test pattern for the extra contact defect at the crosspoint between  $X_j$  and product line  $P_k$ , such that  $X_j$  has a contact with  $P_k$ .

- (ii)  $X_i$  becomes logical ZERO (ANDed short). Hence, the short is detected by a test pattern for the missing contact defect at the crosspoint between  $X_i$  and product line  $P_1$ , such that  $X_j$  has no contact with  $P_1$ .

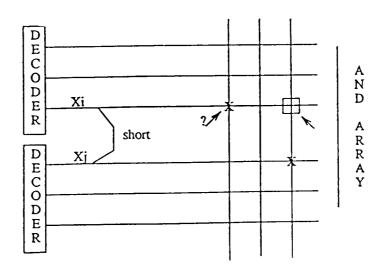

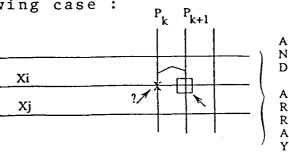

with two decoders: consider the following case:

- (i) if the short is ORed, the fault is detected in the same manner described in case (i) of the single decoder.

- (ii) if the short is ANDed, the fault is detected in the same manner described in case (ii) of the single decoder if and only if  $X_j = 0$ . However, if  $X_j = 1$ , a test pattern other than those belonging to the contact defects test set is needed.

## (c) shorts between product lines (AND plane).

Consider the following case:

- (i) if the short is ANDed, the fault is detected by a test pattern for the extra contact defect at the crosspoint between  $X_i$  and  $P_{k+1}$ .

- (i) if the short is ORed, the fault is detected by a test pattern for the missing contact defect at the crosspoint between  $X_i$  and  $P_k$  provided that  $P_{k+1} = 1$ .

# (d) shorts between product lines (OR plane).

Consider the following case:

(i) if the short is ORed, the fault is detected by a test  $pattern \quad for \quad the \quad extra \quad contact \quad defect \quad at \quad the \\ crosspoint \ between \ P_{k+1} \quad and \quad F_j \, .$

(i) if the short is ANDed, the fault is detected by a test pattern for the missing contact defect at the crosspoint between  $P_k$  and  $F_j$  if and only if  $P_{k+1}=0$ .

# (e) crossline shorts (AND or OR planes).

In this case, the short occurs between the metalization and diffusion layers of the chip. An extensive analysis in [16] and [17] shows that a crossline short is equivalent to a multiple stuck fault at some logic level of the logical diagram. Therefore, these faults are guaranteed to be detected by some crosspoint defect tests.

Undoubtly, the above analysis reveals the influences of layout and personality of a PLA on the coverage of stuck\_at and short fault. However, it has been concluded that any complete single crosspoint fault test set for a PLA is also a very good test for most stuck and bridging faults [16].

### 2.3.3 CROSSPOINT DEFECTS

This fault is the absence (missing) or the unnecessary presence (extra) of a cross connection or device between a bit line (input column) and a product line or between a product line and a sum (output) line. Recall the definitions of crosspoint contacts given in section 2.2.1, crosspoint defects may also be defined as follows:

definition 2.3.1 a single O\_contact (1-contact) <u>fault</u> is said to exist in a PLA structure if due to some failure, a 0-contact (1\_contact) of the fault free PLA becomes a 1\_contact (0\_contact) in the faulty PLA.

This type of fault is usually assumed for PLAs because it is more accurate than the other two types. The justifications for using the contact fault model may be summarized below:

- fault collapsing can be performed within the contact 1. fault model [18]. Extra contact fault, at crosspoint of an already selected input variable AND plane, dominates a missing contact fault in the OR plane for the same row. For example, NOR NOR technology, the relevant product line is forced to zero as can be seen in Figure 2.6; showing such arrangement and its equivalent an representation. Thus, a test for this particular qualified as a test for the "existence" of is the product term P in the map of the output function.

- number of (single) crosspoint faults 2. the crossline bridging faults is a function of the area of the PLA, while the number of the other (single) is linear in the number of input, output, and product lines. Since crossline bridging faults are stuck at faults (see previous equivalent to some section), then the number of the contact faults is by largest of all the three types. Hence, the far size (length) of a single contact fault test set may largest. Accordingly, a higher fault be the cover will be achieved by adopting this model.

- 3. the contact fault model allows efficient generation of compact, technology invariant tests. The

X: normal contact

@:extra contact (fault)

## (a) modified personality of a faulty PLA

(b) equivalent representation in NOR\_NOR technology

Fig. 2.6 Fault Collapsing in PLAs

structural regularity, and the ability of representing contact faults at a higher, functional\_level are good justifications.

## 2.3.4 THE PRODUCT TERM FAULT MODEL

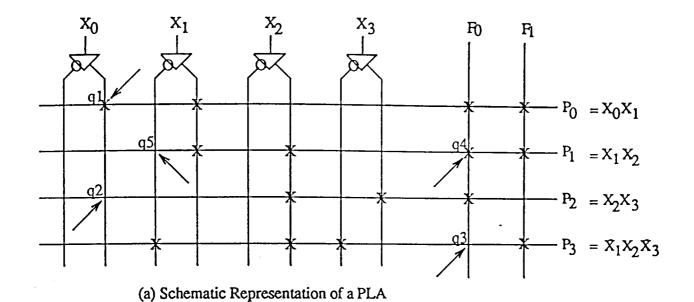

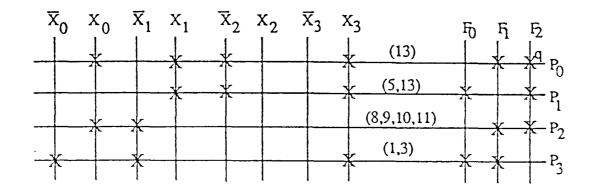

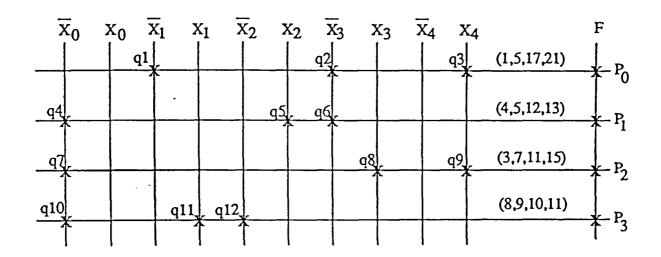

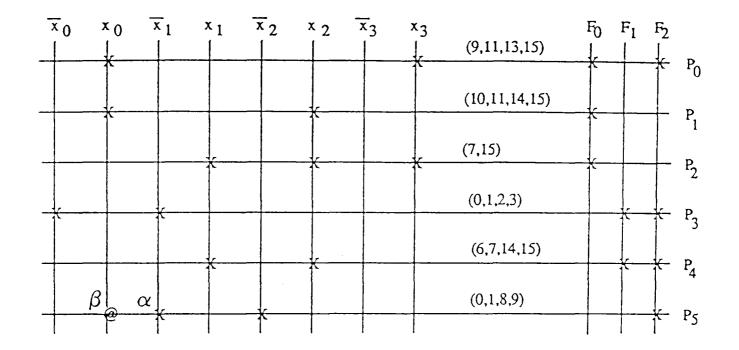

As physical failures, crosspoint defects in a PLA may be viewed as incorrect wire connections on the equivalent logical diagram of the PLA. These connections are, in fact, the programming points (crosspoints) of the search and read arrays of the PLA. Figure 2.7(a) shows a simple schematic diagram of a 4 input PLA implementing two switching functions:

$$F_0 = X_0 X_1 + X_1 X_2 + X_2 X_3$$

$F_1 = X_0 X_1 + X_1 X_2 + \overline{X}_1 X_2 \overline{X}_3$

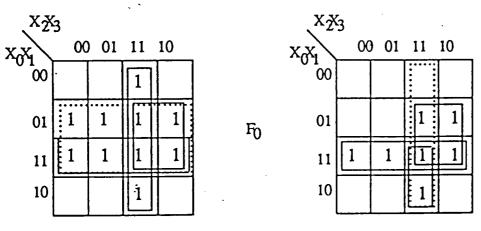

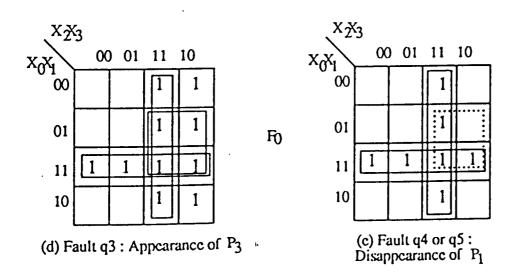

With the aid of Figure 2.7, the product term fault model is described below:

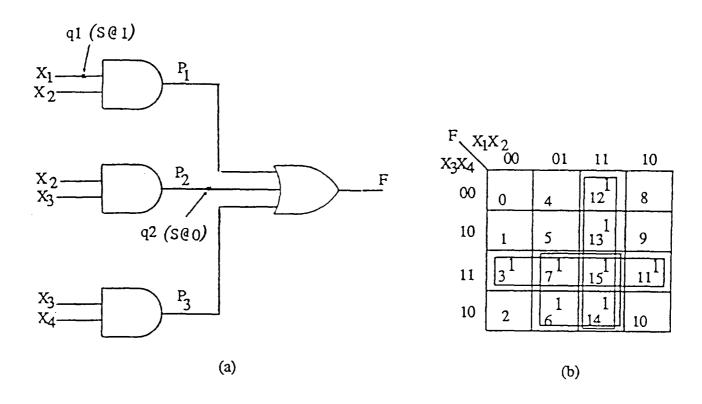

### (1) Growth Faults, G

If an input literal is disconnected from an AND gate, the implicant generated by this gate will "grow" since it becomes independent of some input variable. The effect is equivalent to a missing contact fault in the search array. In Figure 2.7(a), a missing contact fault (ql) in the search array causes the implicant  $P_0$  ( $X_0$ ) to grow to ( $X_1$ ) as is illustrated in Figure 2.7(b).

## (2) Shrinkage Faults, S

If an input literal becomes incorrectly connected to an AND gate, then the corresponding implicant "shrinks".

(b) Fault q1: Growth of  $P_0$  (c) Fault q2: Shrinkage of  $P_2$ .

Fig. 2.7 Effects of Contact Faults on PLA Product Terms

For example, an extra contact fault (q2) causes the implicant  $P_2$  ( $X_2X_3$ ) to shrink to ( $X_0X_2X_3$ ) as shown in Figure 2.7(c).

## (3) Appearance Faults, A

If an AND gate becomes incorrectly connected to an OR gate, then an implicant "appears" on the map of the corresponding output. This is equivalent to an extra contact fault in the read array. The effect of the extra contact fault (q3) is shown in Figure 2.7(d)

## (4) Disappearance Faults, D

If an AND gate becomes incorrectly disconnected from an OR gate, then the corresponding implicant "disappears" from the map of the relevant output function. Thus, a missing contact fault (q4) will cause the disappearance of the implicant  $P_1$  as shown in Figure 2.7(e).

## (5) Vanish Faults, V

If  $X_j$  ( $\bar{X}_j$ ) is an input variable already connected to some AND gate, then an incorrect connection of  $\bar{X}_j$  ( $X_j$ ) to the same AND gate will cause the corresponding implicant to "vanish". The effect is identical to the disappearance of an implicant from the map of the output function.

To summarize, therefore

- an <u>input</u> 0\_contact fault is the same as a growth fault,

- 2. an <u>output</u> 0\_contact fault is equivalent to an appearance fault,

- 3. an <u>input l</u> contact fault is equivalent to either a vanish or shrinkage fault, and

- 4. an <u>output</u> 1\_contact fault is the same as a disappearance fault.

## 2.4 TESTING PROGRAMMABLE LOGIC ARRAYS

The increasing popularity, in terms of structural regularity and flexible means of implementing logic circuits, of Programmable Logic Arrays (PLAs) has imposed the necessity to establish efficient test procedures for these arrays.

Several approaches have been reported to generate a minimum or near minimum test set for a PLA. They all are affected, to some extent, by the basic fault model they use and by the size of the PLA. In the following subsections, a brief discussion on the use of various fault models to generate tests for PLAs is presented.

### 2.4.1 Using The PLA Logic Model

Muelhdrof [19] and Cha [20,21] have used classical stuck at fault test generation algorithms after modeling the PLA as a functionally equivalent logic network. For example, in MOSFET Technology, NOR gates are usually used to implement the required function. Accordingly, it is possible to employ a program that will use a stuck at zero (S@O) criterion for all input lines of all NOR gates, and both S@O and S@l faults for all output lines of all NOR gates to generate a complete test set. The procedure always involves the selection (activation) of one product

always involves the selection (activation) of one product line by assigning suitable input values (activity pattern contains 0, 1, and X: do not care) on the input columns of the PLA.

It is obvious that the computational time of the above test scheme increases considerably with the size of the PLA due to the large number of component blocks produced by adopting such a scheme.

## 2.4.2 Using The PLA Personality

Ostapko [22] used an abstract matrix representing the AND OR personality of the PLA. In this method, for every single crosspoint defect, it is necessary to determine the equivalent bit pattern change that results from that defect. Thus, given a PLA personality, crosspoint fault detection is the same as testing that the ZEROS and ONES of the personality matrix are functionally correct. row in the personality matrix is regarded as a multi\_part cube where the number of the cube parts depends number of decoder networks. The method uses global cube ordering and cube operations to derive the tests. The resulting bit change can be analyzed to see whether or not it would be detected. Thus, during the test generation process the method requires repeated fault simulation to determine the fault cover.

Eichelberger [23] associated with every <u>used crosspoint</u> defect a stuck at fault and established the necessary and sufficient conditions to sensitize a test path through the OR plane of the PLA. The method uses a matrix representing

the PLA without expansion into equivalent logic blocks. It exploits the concept of redundant testing and expands its application to generate tests for PLAs.

As the complexity of the PLA increases, random testing becomes inefficient due to the large number of used crosspoints. The probability of detecting a missing crosspoint with a random pattern is not better than  $1/2^n$ , where n is the number of used crosspoints [23].

### 2.4.3 Using The PLA Functional Specification

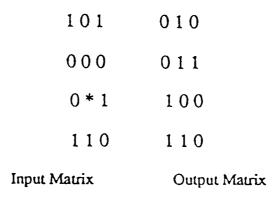

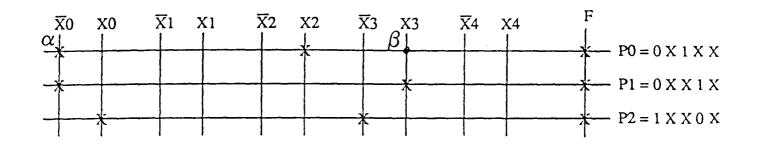

Somenzi [18], Smith [17], and Bose [14] have used the cubical notation (see Appendix A) to represent the PLA personality and to specify the set of the product terms. Figure 2.8(a) shows a PLA specification matrix of the following switching function:

$$F_1 = X_1 X_3 \bar{X}_4 + X_2 \bar{X}_3 + \bar{X}_1 X_3$$

$F_2 = X_1 X_3 \bar{X}_4 + X_2 \bar{X}_3 + \bar{X}_2 X_3 X_4$

In [18], fault simulation is required to establish an Excitation Cube, EC, representing the fault effect. The EC is obtained by assigning proper logic values at the faulty bit of the cube under consideration (see Figure 2.8(b)). Fault effect propagation is performed by selecting those conditions in EC which cause one of the outputs to depend on the fault to be covered. The necessary condition for preventing fault propagation is defined as a Masking Function MF; which is obtained always by deleting the faulty cube from the PLA specification matrix as shown in Figure 2.8(c).

A complete test set for a particular crosspoint defect is given by

EC - MF

where (-) denotes the "set difference" operation, i.e., to obtain those conditions in EC not covered by MF (see Appendix A).

The methods described in [14] and [17] use the same policy given in [18] as they analyze a crosspoint defect at a higher level. The effect of actual physical failures is viewed in terms of changes in the product term configuration on a Karnaugh Map, that is growth, shrinkage, appearance, and disappearance of the product terms.

In [17], fault simulation and backtrack procedures are required to perform fault sensitization to the outputs and consistency assignments to the inputs. On the other hand, the method described in [14] involves mass computations to perform the necessary comparisons between the cubes representing the product terms. The complexity of the algorithms employed by this approach grows geometrically with the number of the product terms in the PLA.

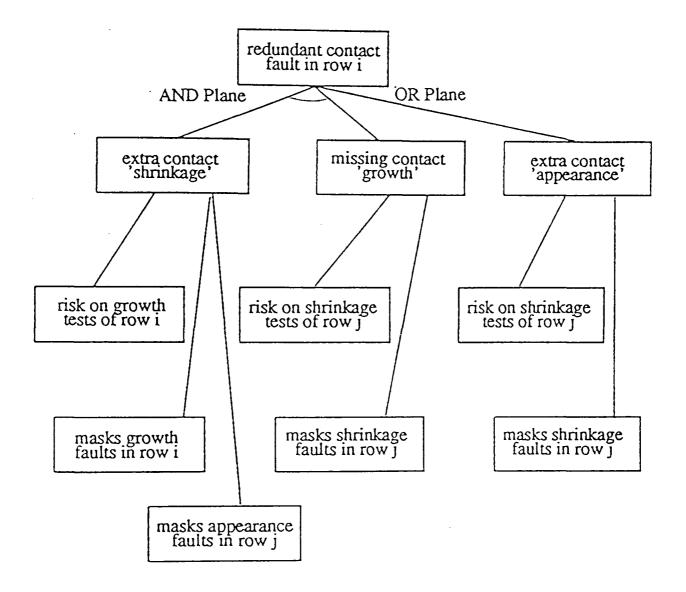

#### 2.5 FAULT MASKING IN PROGRAMMABLE LOGIC ARRAYS

An important problem in fault detection is to verify whether a single fault test set is able to detect all multiple faults. A test derived for the detection of some fault may fail this purpose in the presence of another

fault [29]. Similarly, a set of diagnostic tests derived for a general PLA structure is not necessary a valid set, if a fault occurrence in the structure is preceded by the occurrence of some undetectable (redundant) faults. If a testable fault is masked, the output may indicate no fault during testing yet give erroneous response during normal operation. The above phenomenon, called "masking" among faults, has a great impact on fault detection in PLAs.

definition 2.5.2. A single contact fault  $(q_1)$  is said to be <u>masked</u> by another single contact fault  $(q_2)$  for an input vector  $X_t$ , if  $X_t$  tests  $q_1$  but does not test the simultaneous fault  $q_1q_2$ .

Referring to the logical view of the contact fault model, the following properties specify all the necessary conditions under which masking might take place in a PLA.

In these properties let

G: denotes the set of all growth faults,

A: denotes the set of all appearance faults,

S: denotes the set of all shrinkage faults,

V: denotes the set of all vanish faults,

D: denotes the set of all disappearance faults, and

[]: denotes the "set union" operation (see appendix A)

property 2.5.1 For a given test vector  $X_t$ , a detectable fault from the set  $(G\bigcup A)$  existing on some product line  $L_i$  of the PLA, can be masked only by 'one' fault from the set  $(S\bigcup D\bigcup V)$  also existing on the same product line  $L_i$ .

property 2.5.2 For a given test vector  $X_t$ , a detectable fault from the set  $(S \bigcup D \bigcup V)$  existing on some product line  $L_i$  of the PLA, can be masked only by a fault from the set  $(G \bigcup A)$  existing on some product line other than  $L_i$ .

The above two properties are based on lemmas 2 and 3 respectively as defined by Agarwal [25] where equivalent relationships have been proved.

## 2.6 MULTIPLE FAULT DETECTION IN PLAS

The problem of multiple fault detection in PLAs is mostly directed to the evaluation of the single fault test set capabilities to detect multiple faults. The evaluation is based on a rather general assumption; an irredundant PLA structure.

Agarwal [25] has proposed a modeled network, called Stuck At Equivalent, SAE, network, which represents the complete PLA structure. Each single crosspoint defect (contact fault) is functionally equivalent to some stuck at fault in the modeled network. The SAE network is shown to be a 3\_level, internal fanout free with respect to any output line, network. In an irredundant, internal fanout free network, every multiple stuck at fault of size 2 or 3 (number of simultaneous faults) is covered by any test set that covers only the single stuck at faults of the network [26,27]. Accordingly, it has been stated that:

"Every complete single contact fault test set of an irredundant PLA covers every multiple fault of size 2 or 3" [25].

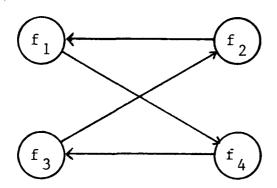

For multiple contact faults of size 4 and larger, the concept of the 4-way masking cycle is involved. This phenomenon occurs when four components ( $f_1$ ,  $f_2$ ,  $f_3$ , and  $f_4$ ) of a multiple fault of size 4 or more, are distributed such that  $f_1$  masks  $f_4$ ,  $f_4$  mask  $f_3$ ,  $f_3$  masks  $f_2$ , and  $f_2$  masks  $f_1$ . This phenomenon may be described by the following direct graph:

An irredundant PLA with n inputs, m product terms, and  $\,p\,$  outputs has been proved to have the following property:

"Out of  $\binom{m(2n+p)}{r}$ , r>4, different contact faults of size r, at most  $\binom{m}{2}$ .  $\binom{m}{2}$ .  $\binom{m(2n+p)-4}{r-4}$  faults are not covered by every complete single contact fault test set of the PLA".

At the worst case, the maximum number of contact faults of size 4 with 4-way masking is  $\binom{m}{2}$ .  $(n + p/2)^4$ , as reported in [25].

A close investigation to the above coverage Figures shows that for an irredundant PLA with n=16, m=48, and p=8, there are two cases to be considered:

case (i) r=4: the number  $\binom{m}{2}$ .  $(n + p/2)^4$  is a mere .03% of the total  $\binom{m(2n+p)}{4}$ .

Thus, 99.97% of all multiple contact faults of size 4 are to be covered by each single contact test set.

case (ii) r>4: in this case, if r becomes large the bound  $\binom{m}{2} \cdot (n + p/2)^4 \cdot \binom{m(2n+p)-4}{r-4}$  becomes greater than  $\binom{m(2n+p)}{r}$ . Thus, a practical use of the above property is only convenient for values of r not exceeding 8.

Similar evaluations have been described in [28] and [29] by Rajski and Tyzer. They quantitatively predicted the multiple contact fault coverage capability of a single contact fault test set in a PLA. The problem is studied from the point of view of the theory of combinations. They have shown that some of the multiple faults of size r,  $r \geqslant 4$ , which contain a 4-way masking could be detected by a single fault test set of the PLA. The validity of this point depends on the types and locations of the fault components other than those involved in the 4-way masking cycle.

## 2.7 SUMMARY

Test sets derived for the detection of single crosspoint defects in a PLA can not be safely used, if the PLA contains undetectable crosspoint faults. This is due to the phenomenon of masking among faults. The necessary conditions under which fault masking might take place in PLAs are presented using the product term fault model. The work presented in [25,28,29] is based on an "irredundant" PLA. The attempt was to predict the ability of single fault test sets to detect multiple faults. The

coverage results given in the above papers, however, can not be used for PLAs having redundant faults, unless the PLA is converted to a crosspoint irredundant structure for testing purposes.

No known method exists to convert a general PLA structure to an irredundant one without using extra hardware. For example, the control input procedure described by Ramanatha [30] implies that a number of control inputs (extra input columns) may be added to obtain a crosspoint irredundant PLA structure.

Other techniques have been proposed to augment a PLA for improving its testability [31-37]. They all are based on the idea of adding extra hardware to achieve high fault coverage and to overcome the problems of undetectable faults. Therefore, an extra silicon area must be devoted to serve for testing purposes, and faults in this additional test circuitry (mostly sequential) must also be considered.

In the following Chapter, the influences of undetectable contact faults in PLAs are analyzed. The prime implicant method for testing irredundant two level AND\_OR networks [16] is elaborated for the sake of such analysis.

## CHAPTER THREE

## FAULT MASKING EVALUATION IN PROGRAMMABLE LOGIC ARRAYS

#### 3.1 INTRODUCTION

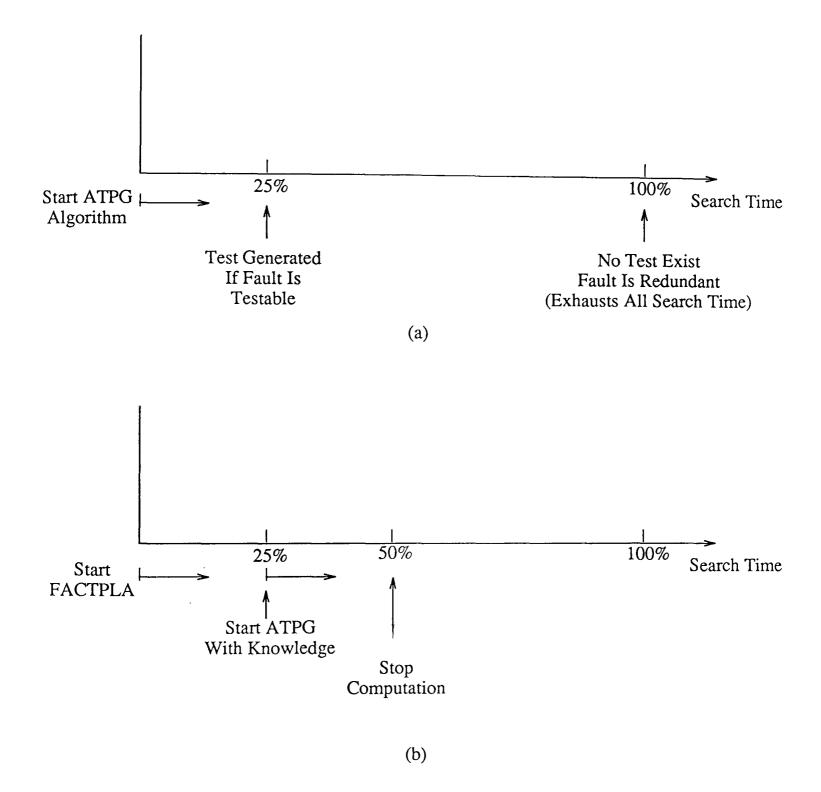

The existence of undetectable faults represents one of the most important aspects in functional testing. Within the test generation process, even an exhaustive search may fail to find a test for a fault, i.e., no test exists. The fault is undetectable (or redundant) and the effort has been wasted. Therefore, efficient test generation requires advance knowledge of all redundant faults. In this context, the complexity of testing a digital circuit may be considered as related to the following parameters:

- (a) The total number of redundant faults. This number has a great influence on the computational time of any automated test procedure.

- (b) The multiple fault coverage capabilities of the single fault test set.

Redundant faults may be determined by analyzing the functional characteristics of the circuit, while multiple fault coverage may be approximated by considering the limitations on the single fault test patterns to detect multiple faults as well. Obviously, the above parameters are closely related, that is, the ability of a single fault test set to cover multiple faults decreases drastically as the number of redundant faults increases.

In the following section, a simple method for testing irredundant two level AND\_OR networks is presented.

The method is shown to be a good vehicle for analyzing and predicting the effects of undetectable faults in PLAs.

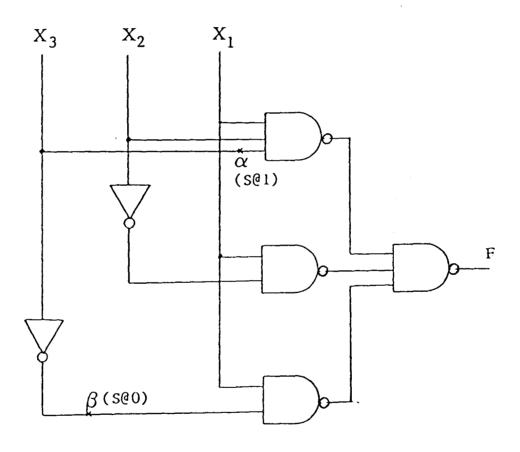

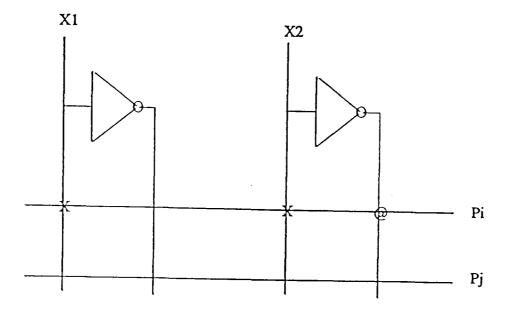

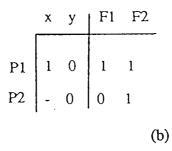

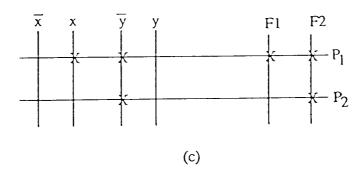

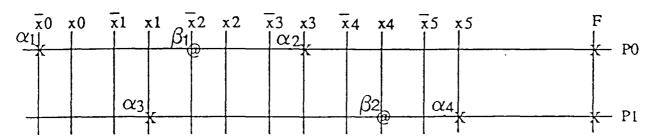

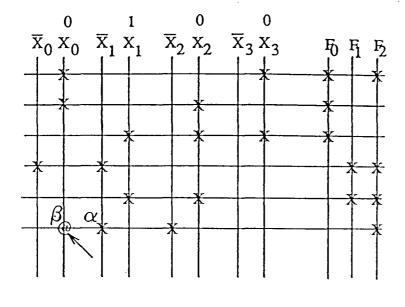

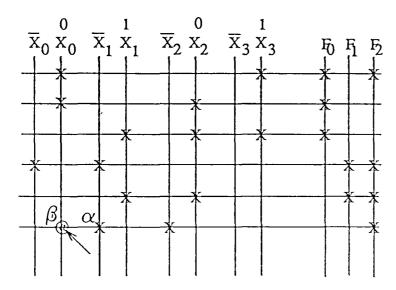

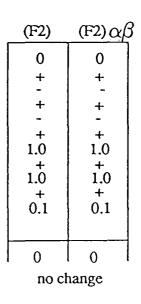

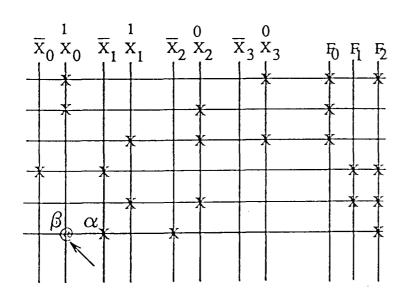

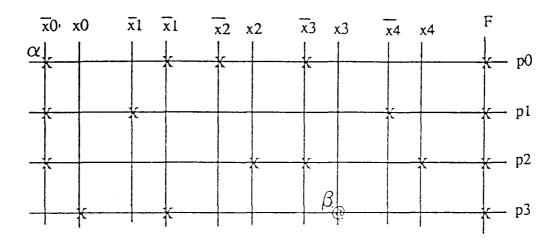

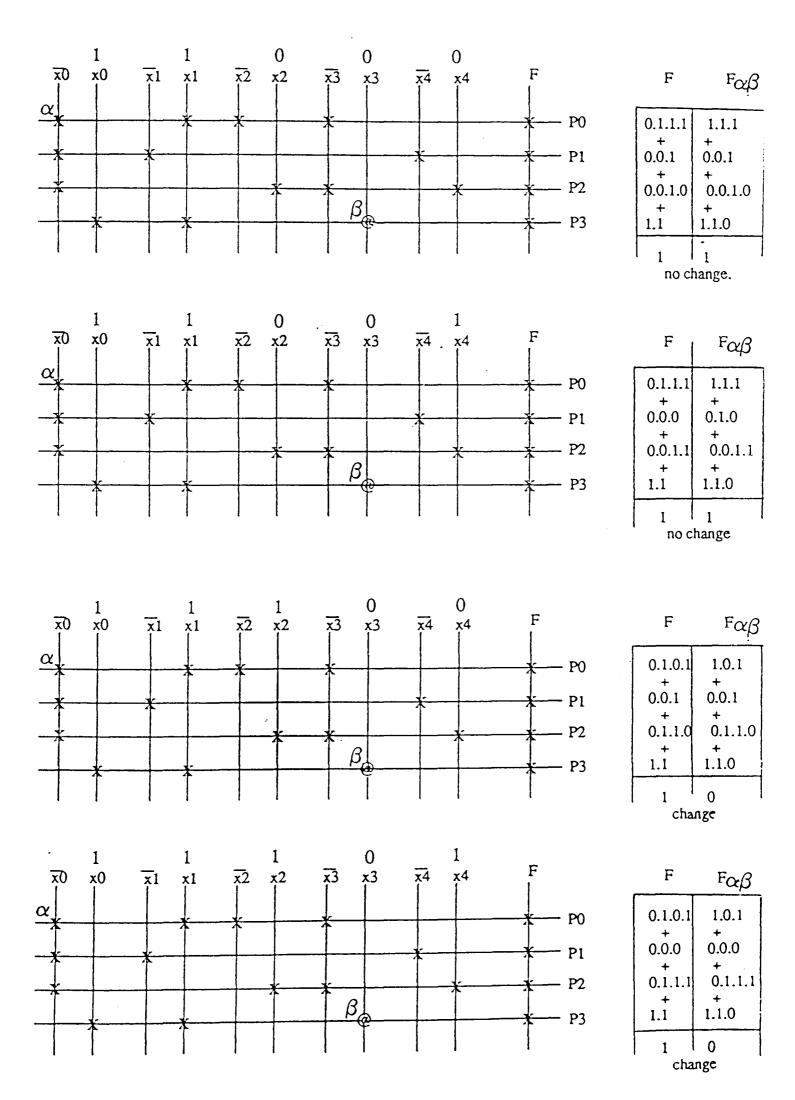

#### 3.1 PRIME IMPLICANT METHOD FOR TEST GENERATION

KOHAVI [13] has shown how a minimal set of tests for an irredundant 2\_level AND\_OR network may be derived from the set of prime implicants of the function under consideration. Based on the classical stuck at fault model, a complete test set can be generated without analyzing the topology of the circuit. Sketch (a) of Figure 3.1 shows an example of an irredundant 2\_level AND\_OR circuit. Karnaugh Map representation is shown in sketch (b). It is well known that for a fanout free combinational circuit, any set of tests which detects all stuck faults on primary inputs will detect all stuck faults in the rest of the circuit [1]. Thus, only stuck at ZERO (S@O) and stuck at ONE (S@I) faults on input leads of the AND gates need to be considered.

It is obvious that the AND gates in Figure 3.1(a) have one to one correspondence with the prime implicants. Thus, a stuck at fault in an AND gate will reveal some functional change in the corresponding prime implicant. This change manifests itself as a growth or disappearance of the relevant prime implicant.

Any input to an AND gate s@l causes a "growth" in the corresponding prime implicant. Figure 3.1(c) illustrates the effect on the prime implicant  $P_1$  due to  $q_1$  ( $X_1$  S@l), i.e.,  $P_1$  ( $X_1$  X<sub>2</sub>) grows to ( $X_2$ ) causing a logical change in

| F X <sub>1</sub>                         | X <sub>2</sub> | 01             | 11      | 10 | F X <sub>1</sub> | X <sub>2</sub>              | 01 | 11      | 10 |

|------------------------------------------|----------------|----------------|---------|----|------------------|-----------------------------|----|---------|----|

| ∞<br>•                                   | 0              | 4              | 121     | 8  | 00               | 0                           | 4  | 12      | 8  |

| 10                                       | 1              | 51             | 131     | 9  | 10               | 1                           | 5  | 1<br>13 | 9  |

| 11                                       | 31             | 7 <sup>I</sup> | 151     | 11 | 11               | [ <sub>3</sub> <sup>1</sup> | 71 | 15      | 11 |

| 10                                       | 2              | 1              | 1<br>14 | 10 | 10               | 2                           | 6  | 1 14    | 10 |

| (c) Growth of P1 (d) Disappearance of P2 |                |                |         |    |                  |                             |    |         |    |

Fig.3.1 Prime Implicant Method for Functional Testing

the map of the output function.

Definition 3.1.1 The set of extra minterms contributed by a growth fault is called the growth term.

Obviously, there are n growth terms (or faults) associated with the prime implicant which is corresponding to an n input AND gate.

<u>Definition 3.1.2</u> Any minterm that is covered by a growth term and does not belong to the function under consideration is called a free minterm.

Since the prime implicant grows to contain a growth term, then any free minterm that is covered by the growth term will detect this particular growth fault. It can be seen from Figure 3.1(c) that any minterm that belongs to the set  $\{4,5\}$  is qualified as a test for  $q_1$ . Hence, a possible minimal growth test set for the circuit example given in Figure 3.1(a) could be  $\{5,10\}$ .

On the other hand, if a s@O fault occurs on an AND gate output, then it affects the behavior of the network as if the corresponding prime implicant was deleted from the map of the output function. This effect is shown in Figure 3.1(d) where the fault  $q_2$  (s@O) causes the prime implicant  $P_2$  to vanish.

<u>Definition 3.3.3</u> For a given output function, any minterm that is covered by a prime implicant is said to be <u>unique</u> if it is not covered by any other prime implicant of the function under consideration. Otherwise, it is said to be bound.

Clearly, every unique minterm belonging to some implicant is qualified as a test for the existence of the relevant implicant. Thus, choosing a unique minterm 'arbitrary' from each prime implicant in the circuit example of Figure 3.1 yields the complete disappearance test set { 12,3,6 }.

The minimal test set to detect all single stuck at faults for the above circuit is the union of the growth and disappearance test sets; that is { 3,5,6,10,12 }.

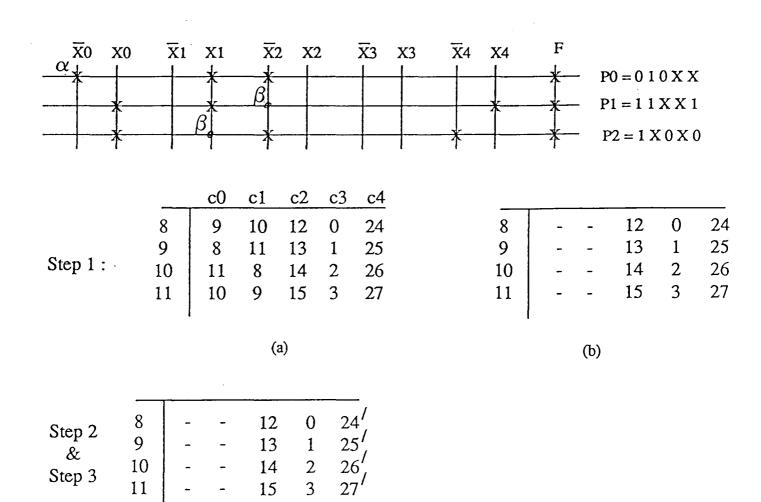

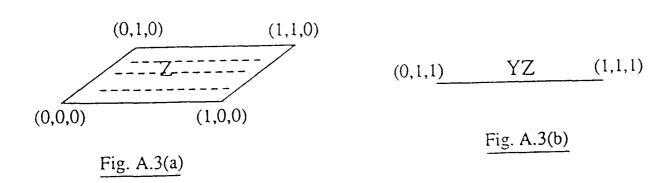

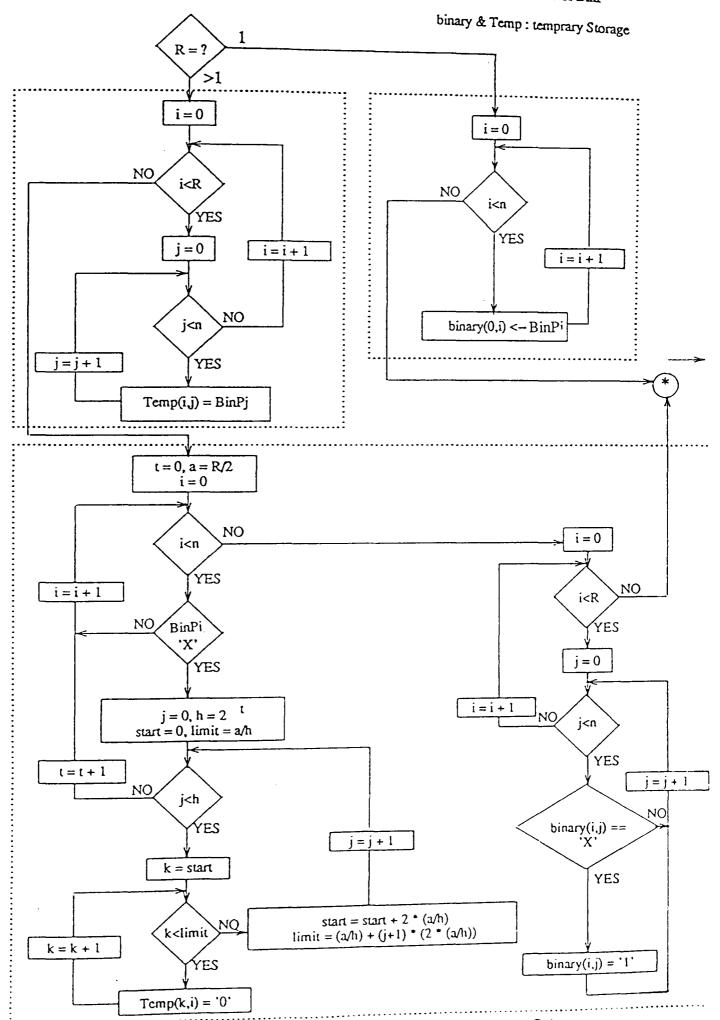

Obviously, the above testing method is not applicable to a general PLA structure since it does not account for all possible contact faults. For instance, shrinkage and faults are not covered by such Nevertheless, this method may be expanded, using for the minterms, to identify redundant faults and evaluate their masking effects on normally detected faults in PLAs. Therefore, an analytic program can be designed to evaluate a difficulty measure for testing a PLA without analyzing the topology of the array structure. In this Chapter, the theoretical concept for such FACTPLA: Functional Analysis and the referred to as Complexity of Testing PLAs, will be established. The described approach is shown to be technology invariant and applicable to the folded versions of The PLA. mathematical notion of the set theory is used to describe the program, and some aspects o f operations on sets that are used in this Chapter are given in Appendix A.

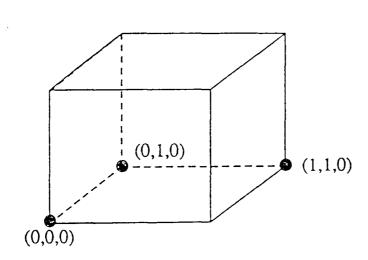

#### 3.3 FUNCTIONAL LEVEL CHARACTERIZATION

In some cases, it may be possible to make use of the functional characteristics of a general digital circuit in order to explore some of its structural properties. For instance, the regularity of a PLA structure may introduce some useful properties at a higher level. The similarity between PLAs and the familiar sum of products expressions is used for this purpose. For a general sum of products expression, the cubical notation is used to represent the possible binary codes, or n\_tuples, of each product term in a general multidimensional space (see Appendix A). Karnaugh Map can be considered as an attempt to project this multidimensional space onto a 2\_dimensional space. It is obvious that the actual dimensionality is determined by n; the number of input variables.

In the sequel, the notion of sets is used such that all the sets are assumed to be 'finite', i.e, having only a finite number of elements. The number of elements in a finite set A is called the 'cardinality' of A and is denoted by |A|. Furthermore, it is very convenient to assume that all the sets are subsets of a fixed universal set (denoted by U). In the context of this thesis, however, the elements of U are the decimal codes of all the minterms found in the multidimensional space determined by n. In other words

$$U = \{ x : 0 \le x \le 2^{n-1} \}$$

Also, the definitions of the set 'union', 'intersection', and 'proper subset' operations (denoted by  $\bigcup$ ,  $\bigcap$ , and  $\bigcap$

respectively) are given in Appendix A. Now, some basic definitions which are used in the rest of this thesis are presented.

Clearly, the size of any product term is equal to  $2^{i}$ , where  $i \geqslant 0$ .

Definition 3.3.2 Two minterms covered by a product term are said to be <u>adjacent</u> if they differ in only one bit, i.e., the difference between their decimal codes is  $2^{i}$ , where  $i \geq 0$ .

<u>Definition 3.3.3</u> Let A and B be two sets of the same cardinality such that

$A = \{ x : x > 0 \}, B = \{ y : y > 0 \}.$

If, for every i, element  $x_i$  in A is adjacent to element  $y_i$  in B, then set A is said to be <u>adjacent</u> to set B or vice versa. On the other hand, if A and B do not have the same cardinality then a 'set adjacency' operation, denoted by (ADJ), may by defined as follows:

A (ADJ) B = {  $x_i : |x_i - y_j| = 2^k$ , where  $y_j :$  the 'first' element in B adjacent to  $x_i$  }, and

B (ADJ)  $A = \{ y_i : | y_i - x_j | = 2^k, \text{ where } x_j : \text{ the 'first'}$  element in A adjacent to  $y_i \}$ , for k > 0.

Obviously, the set  $\{A\ (ADJ)\ B\}$  is not necessary equal to the set  $\{B\ (ADJ)\ A\}$ .

Example. Let  $A = \{0,1,3,5,6,7,8\}$  and  $B = \{8,10,13,21,31\}$ . Then  $A (ADJ) B = \{0,5,8\}$ , and

$$B (ADJ) A = \{ 8, 10, 13, 21 \}$$

Generally, any given minterm (m) is adjacent to a set of minterms (S). This set may be generated using the following expression [24]:

$$S = m + [2^{(i-1)}][(-1)^{m/2}^{(i-1)}] -----(1)$$

for i=1,2,... where

n : the number of the input variables which define the multidimensional space containing m, and  $m/2^{\left(i-1\right)} \ \text{is defined as an integer divide.}$

Recall the possible modifications that are apt to occur for a product term due to some physical failure, the following property hold.

property 3.3.1 For any product term P of size R, there are (i)  $n - Log_2R$  possible Growth faults (= Vanish faults) (ii)  $2Log_2R$  possible Shrinkage faults. where n is the number of input variables.

# proof

(i) A product term P of size R may grow to contain a growth term g<sub>t</sub> of size R also. Each minterm in g<sub>t</sub> is adjacent only to one minterm in the original product term P. Now, if R=1 (canonical term), then the number of possible growth terms (faults) in P = the number of all possible adjacent minterms = n. Thus, for a given value of n, if R increases, the number of the growth terms (or faults) decreases. This relationship can be described by the following Table

Since each entry in the above Table represents a number of growth faults, then it is obvious that the number of growth faults = n - i ------ (2) Now,  $R = 2^i$ , then  $Log_2R = i$  ----- (3) from (2) and (3) we have the number of growth faults =  $n - Log_2R$ .

(ii) In this case, the number of shrinkage faults in any product term does not depend on the dimensionality of the space defined by n. A product term P of size R may shrink to half of its original size. The shrunk term (the rest of the minterms in P) constitutes an implicant of size R/2. Hence, the total number of possible shrunk terms (or shrinkage faults) in P can be arranged in the following Table:

| i | $R=2^{i}$ | possible | implicants | o f | size | R / 2 |

|---|-----------|----------|------------|-----|------|-------|

| 1 | 2         | 2        |            |     |      |       |

| 2 | 4         | 4        |            |     |      |       |

| 3 | 8         | 6        |            |     |      |       |

| 4 | 16        | 8        |            |     |      |       |

From this Table, it is easy to realize that the total number of possible shrinkage faults in P = 2 \* i =  $2 \text{Log}_2 R$ .

It should be noticed that for i=0 the product term contains only one minterm, i.e., P contains the maximum number of literals. This means that all input variables are personalized in this product term, and this case is excluded from the definition of shrinkage faults.

The above property is general to a PLA structure specified as a set of n\_tuple cubes. If, for a given product term cube, the number of the X\_component is k, then the size R (as defined above) of this cube is  $2^k$  (hence,  $k = Log_2R$ ). By definition, shrinkage faults occur due to the incorrect connections of the unpersonalized (X\_component) input variables (complement or uncomplemented) to some product line.

Thus, all possible shrinkage in the product cube =  $2 * the number of X_components = <math>2 * Log_2R$

Obviously, the number of all possible growth faults will be equal to the number of the non  $X_{\rm components}$ . Thus, if n represents the number of all input variables to the PLA, then

all possible growth in the product cube = n - k =  $n - Log_2 R$

Example. let  $P_i$  be the cube ( 1XX10X0X ), where n=8, K=4. Therefore,  $R=2^k=16$  and possible growth faults in  $P_i=n-k=4$ , possible shrinkage faults in  $P_i=2\log_2 R=8$ .

### 3.4 REDUNDANT FAULTS IDENTIFICATION IN PLAS