# CONSTRUCTION OF A SUPPORT TOOL FOR THE DESIGN OF THE ACTIVITY STRUCTURES BASED COMPUTER SYSTEM ARCHITECTURES

By

Sabah Mohamad Amin MOHAMAD, B.Sc, M.Sc., Dip.Comp, AMBCS, MACM

Thesis submitted in fulfillment of the requirements of the degree of Doctor of Philosophy in Computer Science.

> Department of Computer Science, BRUNEL The University of West London, Uxibridge, Middlesex, ENGLAND 1986

To the Lord for his guidance,

To the memory of my father, for his efforts and sacrifices, To my wife for here patience, encouragement and love, To my mother who taught me the love of knowledge, To my brothers and sisters.

### ACKNOWLEDGEMENTS

I would like to express my deepest gratitude to

#### Dr. Ladislav J. Kohout

for his time spend in guiding me in this research and for demonstrating that cooperative research can be so enjoyable. Without his unfailing energy and enthusiasm, I would not be able to complete this thesis.

I wish to thank

#### Dr. C. F. Reynolds

for his most helpful comments and encouragement.

I would like also to thank *Professor W. Bandler* of Florida State University Computer Science Department for his interest in my thesis.

Special thanks to my friends Dr. M. Ohiorenoya of Benn University, Institute of Computer Science, Mr. H.T. George of Brunel University, Electrical Engineering Department, and Professor J.C. Cavoras of Glasgow University for their helpful discussions and encouragement.

Finally, I would like to express my sincere gratitude for the financial support of the Iraqi Government for the period of this research.

The typesetting, formatting and art-work of this thesis have been prepared with  $IAT_EX$  the document preparation system running on an IBM PC/XT and was produced on an IMAGEN Imagestation laser printer.

IAT<sub>E</sub>X is a trademark of Addison-Wesley Publishing Company, T<sub>E</sub>X is a trademark of the American Mathematical Society, IBM PC/XT is a trademark of International Business Machine Corporation, IMAGEN is a tradmark of Imagen Corporation.

Brunel University, Department of Computer Science, S.M.A. Mohamad, "Construction of A Support Tool for The Design of Activity Structures Based Computer System Architectures".

#### ABSTRACT

This thesis is a reapproachment of diverse design concepts, brought to bear upon the computer system engineering problem of identification and control of highly constrained multiprocessing (HCM) computer machines. It contributes to the area of meta/general systems methodology, and brings a new insight into the design formalisms, and results afforded by bringing together various design concepts that can be used for the construction of highly constrained computer system architectures.

A unique point of view is taken by assuming the process of identification and control of HCM computer systems to be the process generated by the Activity Structures Methodology (ASM).

The research in ASM has emerged from the Neuroscience research, aiming at providing the techniques for combining the diverse knowledge sources that capture the 'deep knowledge' of this application field in an effective formal and computer representable form. To apply the ASM design guidelines in the realm of the distributed computer system design, we provide new design definitions for the identification and control of such machines in terms of realisations. These realisation definitions characterise the various classes of the identification and control problem. The classes covered consist of

- 1. the identification of the designer activities,

- 2. the identification and control of the machine's distributed structures of behaviour,

- 3. the identification and control of the conversational environment activities (i.e. the randomised/adaptive activities and interactions of both the user and the machine environments),

- 4. the identification and control of the substrata needed for the realisation of the machine, and

- 5. the identification of the admissible design data, both user-oriented and machineoriented, that can force the conversational environment to act in a self-regulating manner.

All extent results are considered in this context, allowing the development of both necessary conditions for machine identification in terms of their distributed behaviours as well as the substrata structures of the unknown machine and sufficient conditions in terms of experiments on the unknown machine to achieve the self-regulation behaviour.

We provide a detailed description of the design and implementation of the support software tool which can be used for aiding the process of constructing effective, HCM computer systems, based on various classes of identification and control. The design data of a highly constrained system, the NUKE, are used to verify the tool logic as well as the various identification and control procedures. Possible extensions as well as future work implied by the results are considered.

## TABLE OF CONTENTS

| 1 INTRODUCTION                                                                  | 1  |

|---------------------------------------------------------------------------------|----|

| 1.1 Motivation                                                                  | 1  |

| 1.2 Terminology and Definitions                                                 | 9  |

| 1.3 The Thesis Synopsis                                                         | 13 |

| 1.3.1 Presentation of the Thesis:                                               | 13 |

| 1.3.2 CHAPTER 2:                                                                | 14 |

| 1.3.3 CHAPTER 3:                                                                | 14 |

| 1.3.4 CHAPTER 4:                                                                | 15 |

| 1.3.5 CHAPTER 5:                                                                | 15 |

| 1.3.6 CHAPTER 6:                                                                | 16 |

| 1.3.7 CHAPTER 7:                                                                | 16 |

| 1.3.8 CHAPTER 8:                                                                | 17 |

| 2 AN OVERVIEW OF THE EXISTING TECHNIQUES FOR CONSTRUCTING                       |    |

| HIGHLY CONSTRAINED COMPUTER SYSTEMS WITHIN THE SCIENCE                          |    |

| PARADIGM                                                                        | 18 |

| 2.1 General Discussion                                                          | 18 |

| 2.1.1 Abstract Features of Computer Systems Enforcing The Protection Constraint | 24 |

| 2.1.2 An Overview of The Ticket-Oriented Protection Constraint                  | 27 |

| 2.2 The Software Engineering Approach                                           | 29 |

| 2.3 The Computer Architecture Approach                                          | 35 |

| 2.4 The Knowledge Engineering Approach                                          | 44 |

| 2.5 Hints For A Successful Computer System Design                               | 46 |

| 2.5.1 Dedicated Language Dedicated Architecture Approach:                       | 48 |

| 2.5.2 Non-Dedicated Language Dedicated Architecture Approach:                   | 49 |

| 2.5.3 Dedicated Language Non-Dedicated Architecture Approach:                   | 51 |

| 2.5.4 Non-Dedicated Language Non-Dedicated Architecture Approach:               | 52 |

| 2.6 Concluding Remarks                                                          | 52 |

| 3 AN OVERVIEW OF THE EXISTING THEORETICAL APPROACHES FOR                        |    |

| CONSTRUCTING HIGHLY CONSTRAINED COMPUTER SYSTEMS WITHI                          | N  |

| THE SCIENCE PARADIGM                                                            | 54 |

| 3.1 Milestones                                                                  | 54 |

| 3.2 Critique of Analytical Modelling                                            | 56 |

| 3.2.1 The Analytical Models of The Queueing Theory                              | 58 |

| 3.2.2 The Simulation Models of The Queueing Theory                              | 67 |

| 3.2.3 The Empirical Modelling of The Queueing Theory                            | 71 |

| 3.3 Conclusions                                                                   | . 71      |

|-----------------------------------------------------------------------------------|-----------|

| 4 INTRODUCING ACTIVITY STRUCTURES: A METHODOLOGICAL                               |           |

| PROACH FOR CONSTRUCTING HIGHLY CONSTRAINED EFFECTIVE                              | COM-      |

| PUTER SYSTEMS                                                                     | 73        |

| 4.1 Introduction                                                                  |           |

| 4.2 The Cornerstones                                                              |           |

| 4.3 General And Meta Systems Paradigms Versus Activity Structures                 | . 76      |

| 4.4 From Neuroscience Research To Computer System Design                          |           |

| 4.5 Activity Structures versus The Other Neuroscience Modelling Disciplines       | . 79      |

| 4.6 The Concepts of The Design Methodology of Activity Structures                 |           |

| 4.6.1 The Selection Step:                                                         | . 82      |

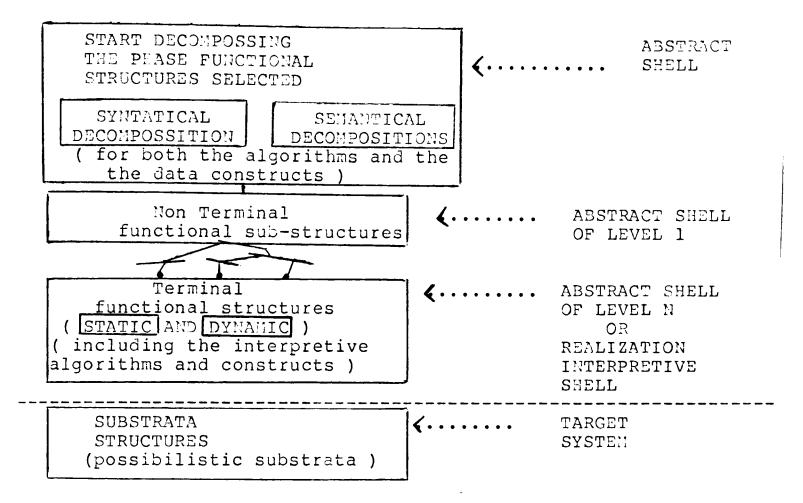

| 4.6.2 The Decomposition Step:                                                     | . 83      |

| 4.6.3 The Representation Step:                                                    | . 87      |

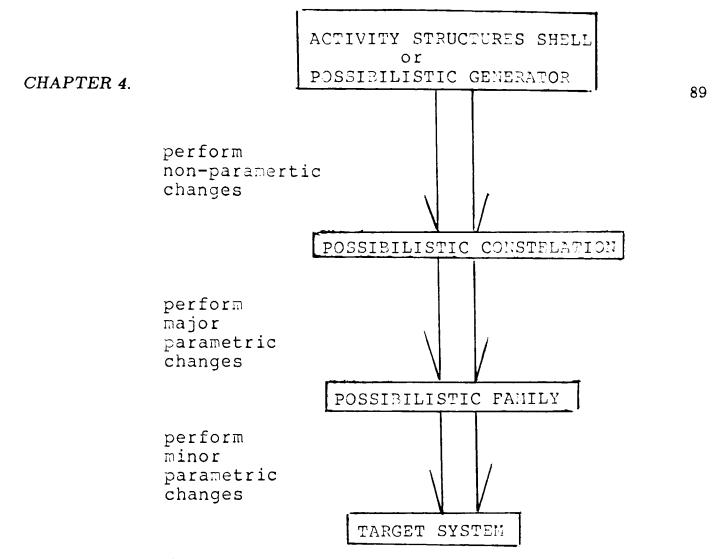

| 4.6.4 The Exploration Step:                                                       | . 88      |

| 4.7 Describing Computer Systems via Activity Structures                           | . 90      |

| 5 AN ABSTRACT SHELL FOR THE ACTIVITY STRUCTURES-BASED CO                          | M-        |

| PUTER SYSTEM DESIGNS                                                              | 99        |

| 5.1 Introduction                                                                  | . 99      |

| 5.2 Representing The Shell Conversational Environment                             | . 100     |

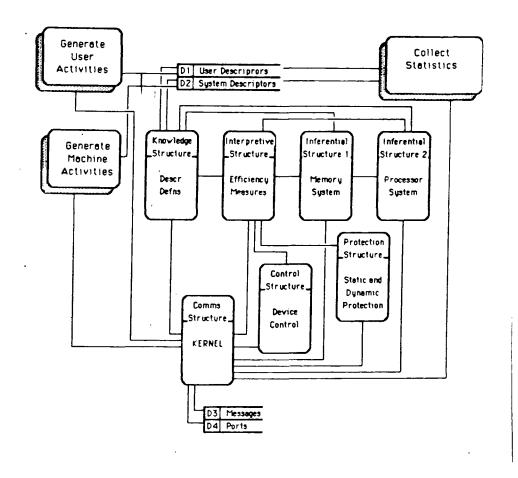

| 5.2.1 Generating User Activities:                                                 | . 101     |

| 5.2.2 Generating the computer machine activities:                                 | . 105     |

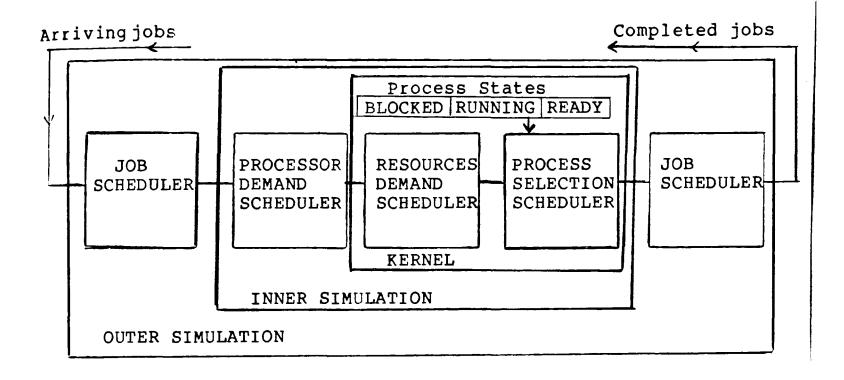

| 5.2.3 Towards Simulating the User and Machine environments:                       | . 109     |

| 5.3 The Functional Structures of The Inner Shell                                  | . 112     |

| 5.3.1 The knowledge representation structures:                                    | . 113     |

| 5.3.2 The inferential structures:                                                 | . 116     |

| 5.3.3 The control structures:                                                     | . 119     |

| 5.3.4 The protection structures :                                                 | . 123     |

| 5.3.5 The communication structures :                                              | . 127     |

| 5.3.6 The interpretive structures :                                               | . 130     |

| 5.4 Performance Probes of The Shell                                               | . 132     |

| 5.5 The Implementation Language of The Shell                                      | . 134     |

| 6 THE IMPLEMENTATION DETAILS OF THE SIMULATION OF AN ACTI                         | <b>V-</b> |

| ITY STRUCTURES BASED COMPUTER SYSTEMS POSSIBILISTIC GE                            | N-        |

| ERATOR                                                                            | 137       |

| 6.1 An Overview                                                                   | . 137     |

| 6.2 The Designer First Activity: Selecting Components Of A Possiblistic Generator | . 138     |

| 6.3 The Designer Second Activity: Decomposing The Possibilistic Generator         | . 142     |

| 6.3.1 Producing Possibilistic Constellation by the Non-Parametric Changes         | . 143     |

| 6.3.2                                                                  | 2 Producing Possibilistic Family by the Parametric Changes                             | 145             |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|--|

| 6.4                                                                    | The Designer Third Activity: Representing The Possibilistic Family                     | 147             |  |

| 6.4.                                                                   | 1 The Generation of the Conversational Environment:                                    | 148             |  |

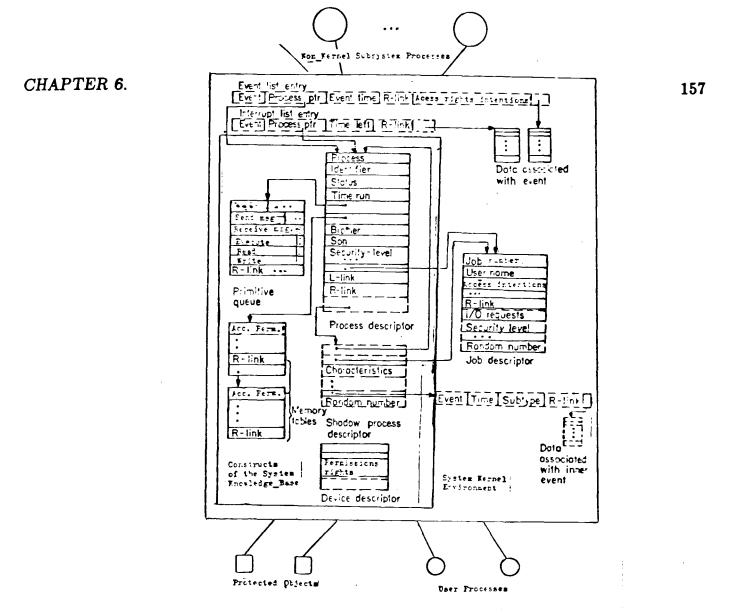

| 6.5                                                                    | The Implementation Details of The Functional Structures                                | 156             |  |

| 6.5.3                                                                  | 1 The Implementation of Knowledge Representation Structures:                           | 156             |  |

| 6.5.2                                                                  | 2 The Interpretive Structures: An Implementation Outline                               | 162             |  |

| 6.5.3 The Communication Structures: The possibilistic generator kernel |                                                                                        |                 |  |

| 6.5.4                                                                  | 4 The Inferential Structures:                                                          | 171             |  |

| 6.5.5                                                                  | 5 The Control Structures: The I/O control                                              | 185             |  |

| 6.5.6                                                                  | The Protection Structures                                                              | 195             |  |

| 7                                                                      | EXPLORING THE DYNAMIC BEHAVIOUR OF THE ACTIVITY STRUC                                  | -               |  |

| ]                                                                      | TURES BASED POSSIBILISTIC GENERATOR OF COMPUTER SYSTEMS                                | 199             |  |

| 7.1                                                                    | <b>An</b> Overview                                                                     | 19 <del>9</del> |  |

| 7.2                                                                    | A Framework for The Behavioural Description of The Activity Structures Based Com-      |                 |  |

|                                                                        | puter Designs                                                                          | 203             |  |

| 7.3                                                                    | Strategy for The Behavioural Description And Performoance Measurement                  | 207             |  |

| 7.4                                                                    | A Brief Overview of The Nuke System                                                    | 210             |  |

| 7.5                                                                    | Collecting The Nuke-Oriented Design Data for The Study of Behaviour of The Possibilis- |                 |  |

|                                                                        | tic Generator                                                                          | 211             |  |

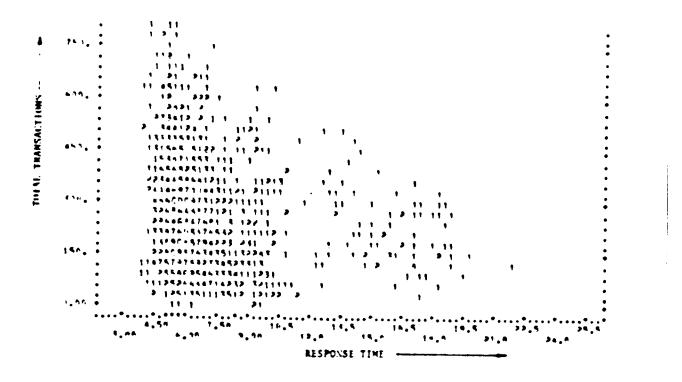

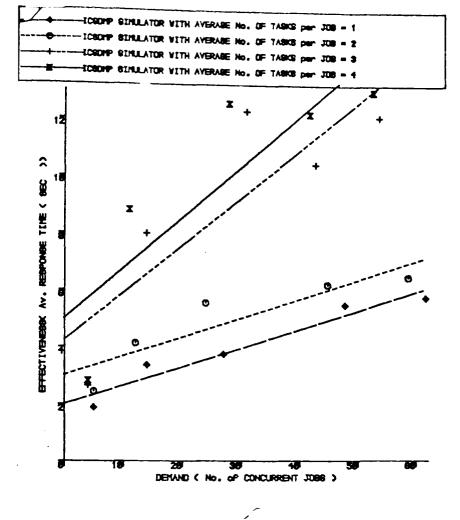

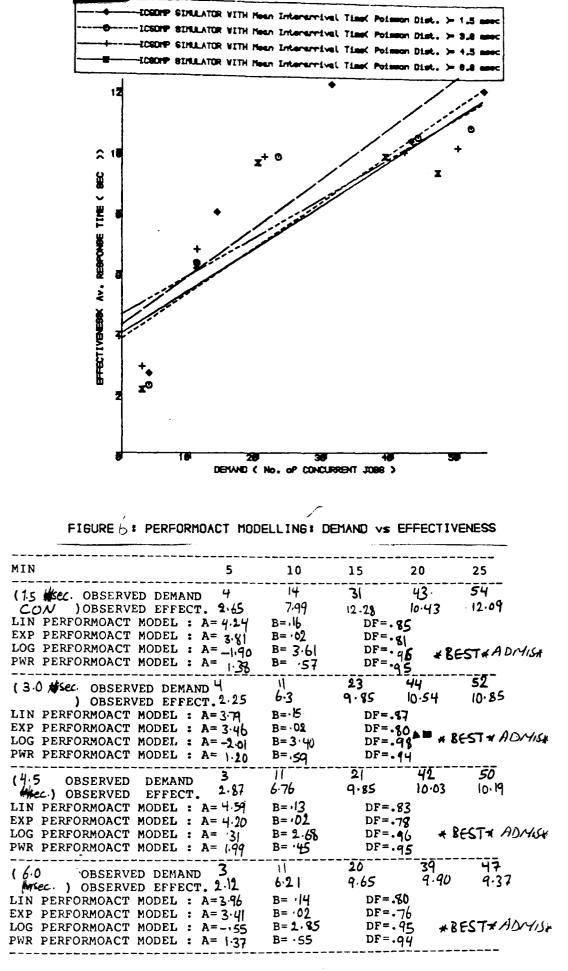

| 7.6                                                                    | Performoact Modelling: Towards Analysing The Behaviour of The Possibilistic Simulator  | 217             |  |

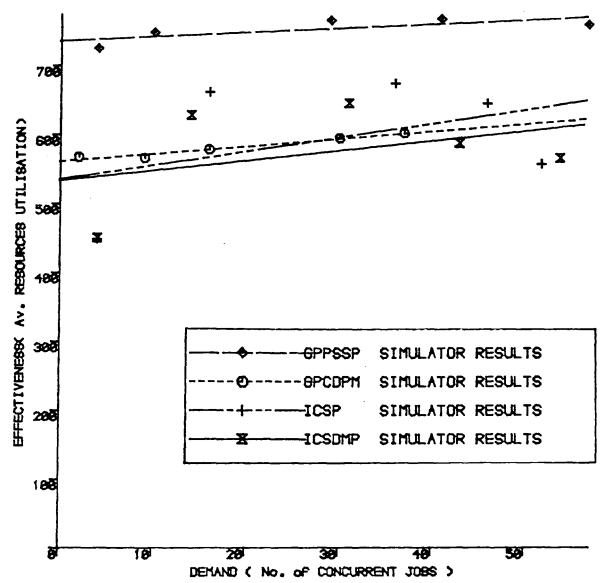

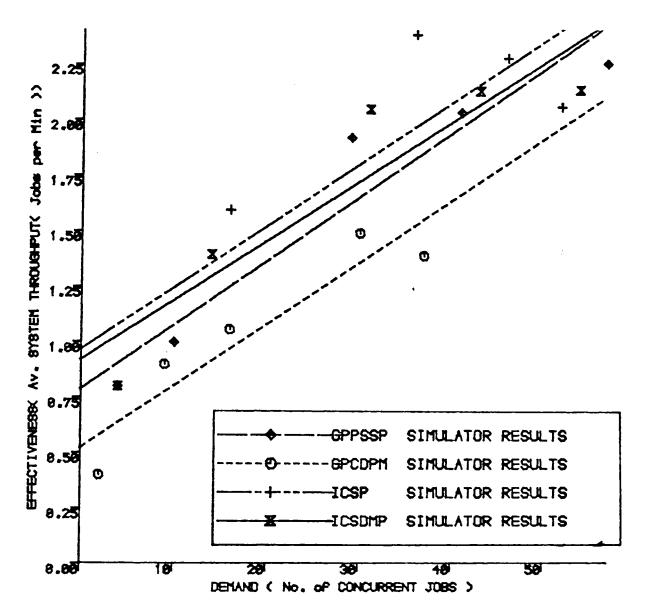

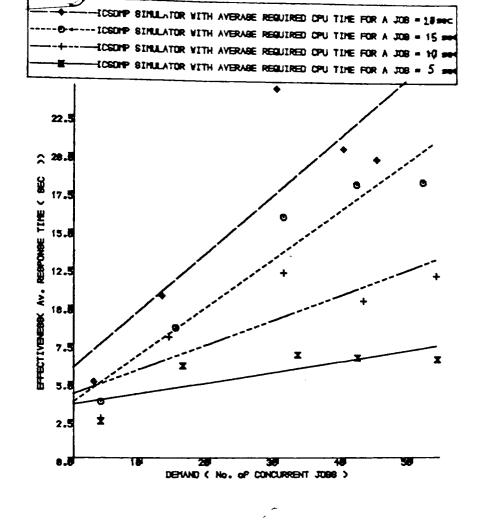

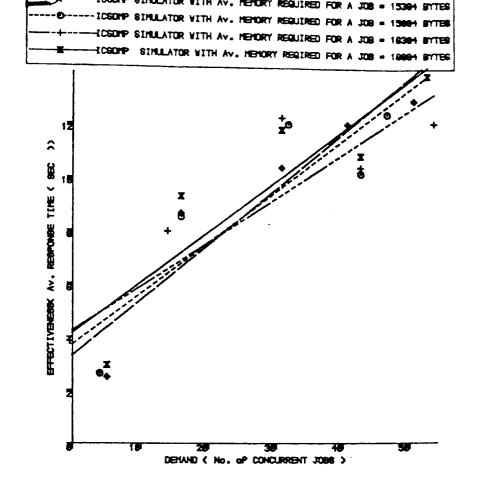

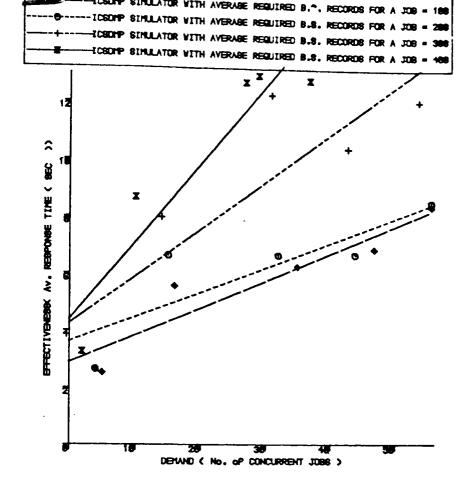

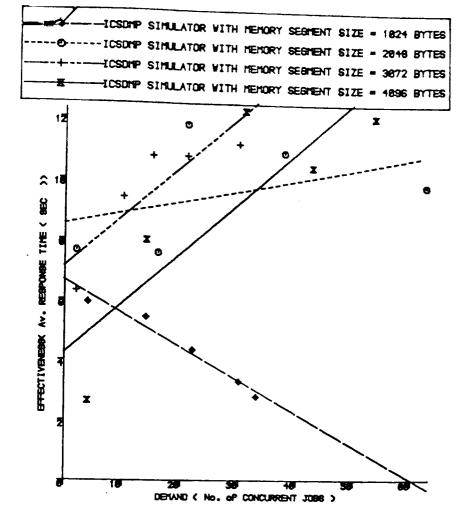

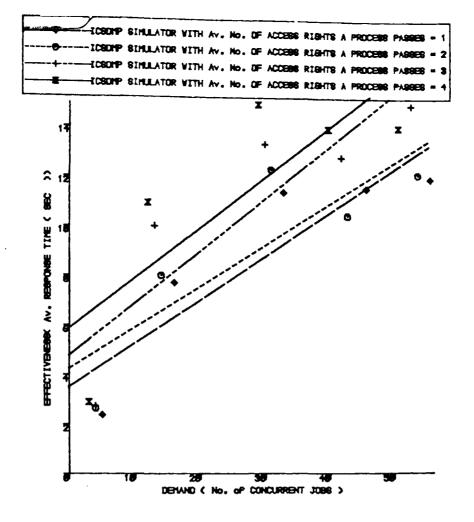

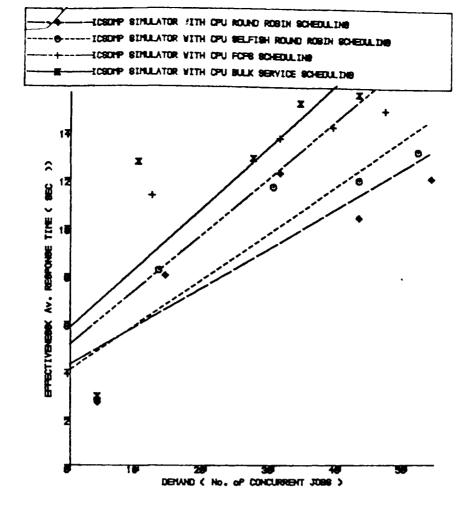

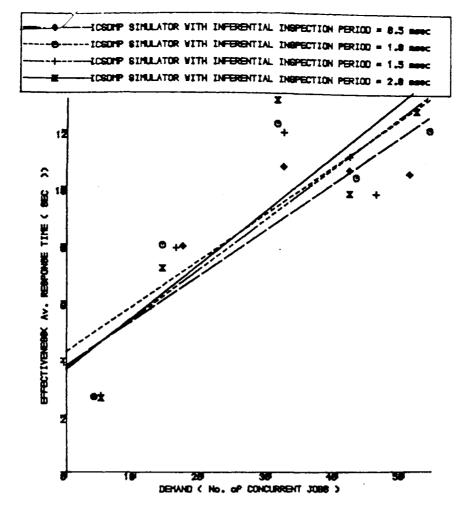

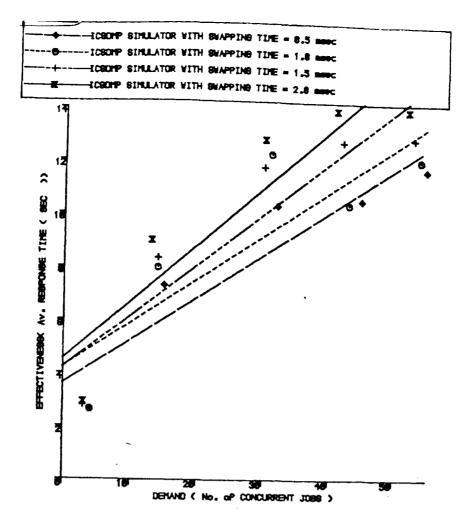

| 7.6.1                                                                  | Towards Experimentations: The Reduction Oriented Changes                               | 218             |  |

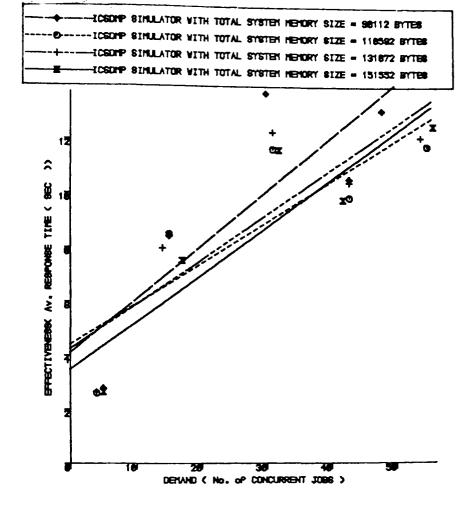

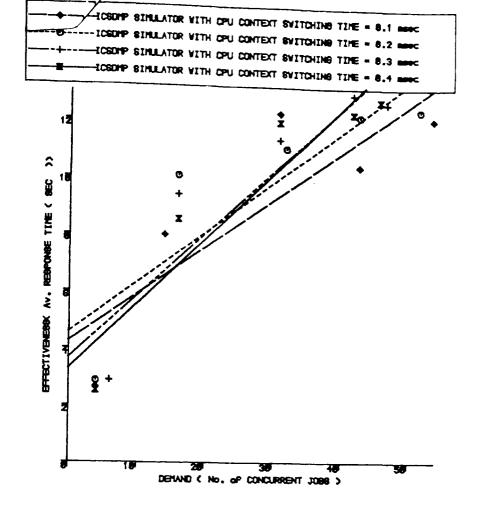

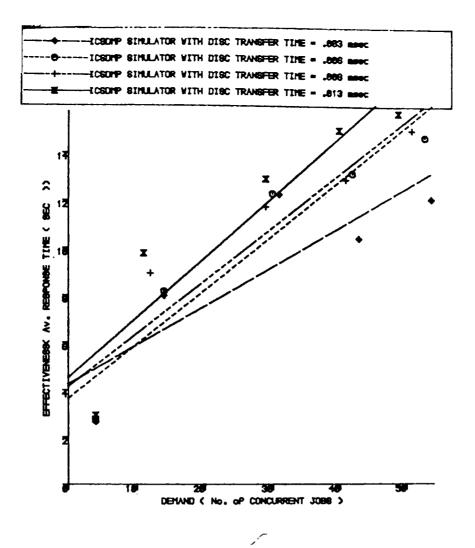

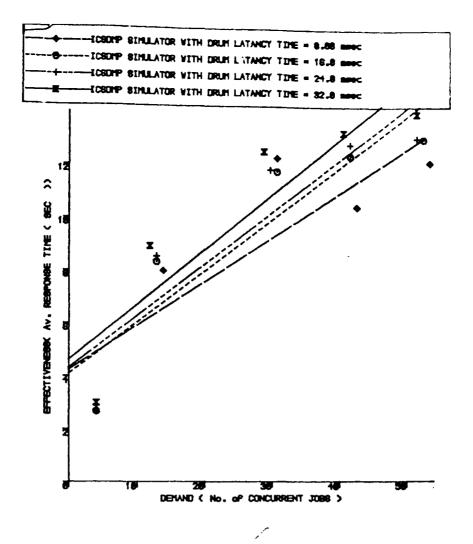

| 7.6.2                                                                  | 2 The results of experiments of performoact modelling:                                 | 229             |  |

| 7.7                                                                    | The Use of Admissible Models and The Validation Issue                                  | 233             |  |

| 8                                                                      | SUMMARY, CONCLUSIONS AND FUTURE RESEARCH                                               | 239             |  |

| 8.1                                                                    | Summary And Conclusions                                                                | 239             |  |

| 8.2                                                                    | Future Research                                                                        | 244             |  |

| F                                                                      | REFERENCES                                                                             | 248             |  |

|                                                                        |                                                                                        |                 |  |

APPENDIX

.

٠

## LIST OF FIGURES

| 1.1           | The essential elements of successful computer design methodologies                     | 6          |

|---------------|----------------------------------------------------------------------------------------|------------|

| 2.1           | The black box: The Traditional Design Methods                                          | 20         |

| 2.2           | The conventional approaches of software engineering that can be used for computer sys- |            |

|               | tems construction.                                                                     | 31         |

| 2.3           | The Hierarchy of Uses: Software Engineering-based Design Method                        | 34         |

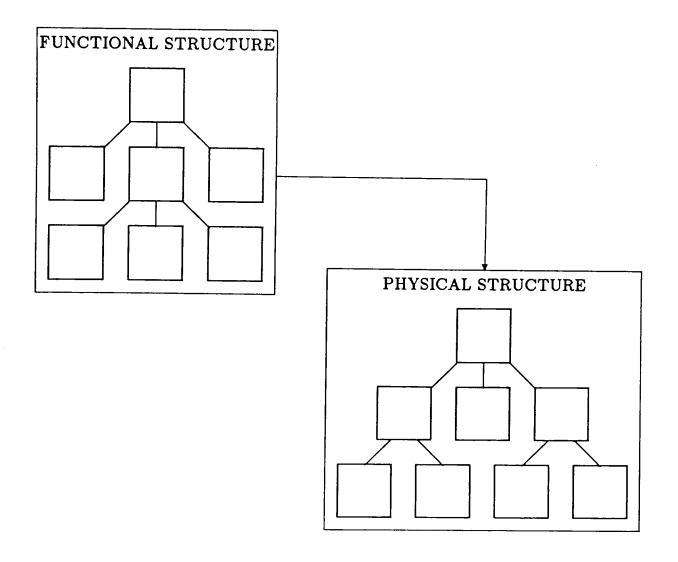

| 2.4           | The Matching Problem Between Structures                                                | 36         |

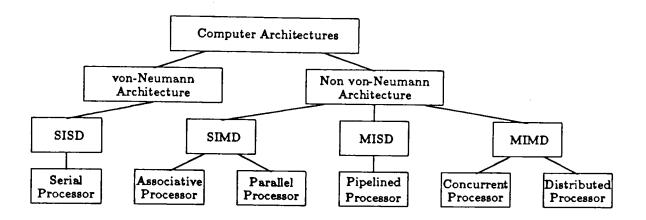

| 2.5           | Flynn's Computer Performance Architectures                                             | 37         |

| 2.6           | Major research efforts at the US supercomputers centres                                | 37         |

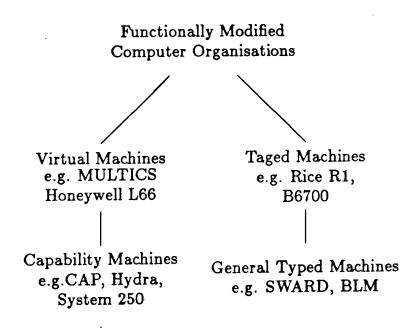

| 2.7           | Functionally Modified Flynn's Architectures                                            | <b>4</b> 0 |

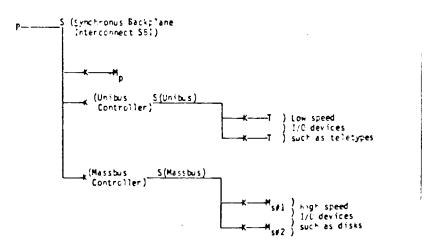

| 2.8           | The PMS Description of the VAX-11/770 computer system                                  | 42         |

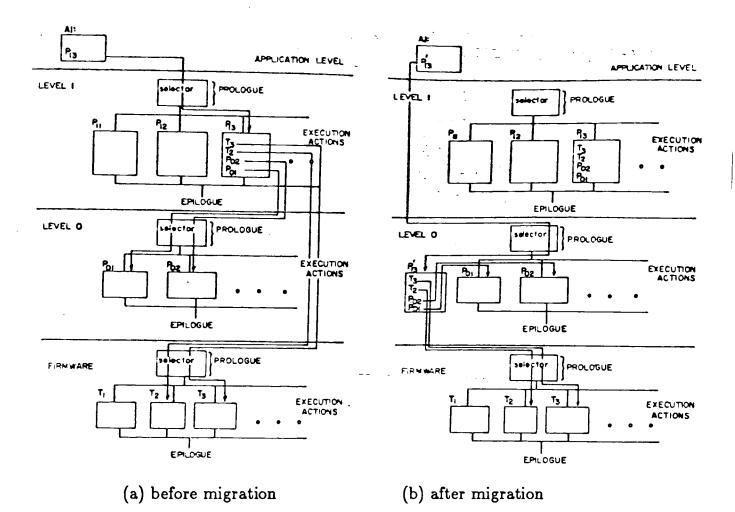

| 2.9           | An Example of a Vertical Migration Process.                                            | 44         |

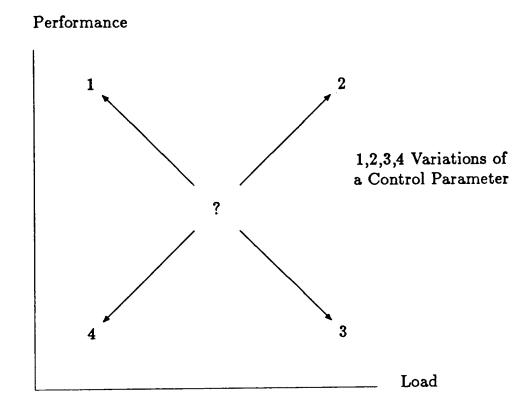

| 2.10          | Reiner Adaptive strategy.                                                              | 45         |

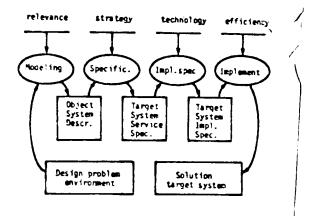

| 2.11          | The main phases of the design process                                                  | 48         |

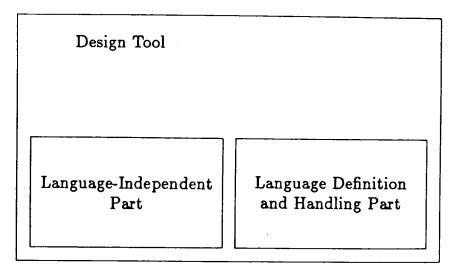

| 2.12          | Design and Synthesis Tools Structure.                                                  | 49         |

| 0.1           |                                                                                        | • • • •    |

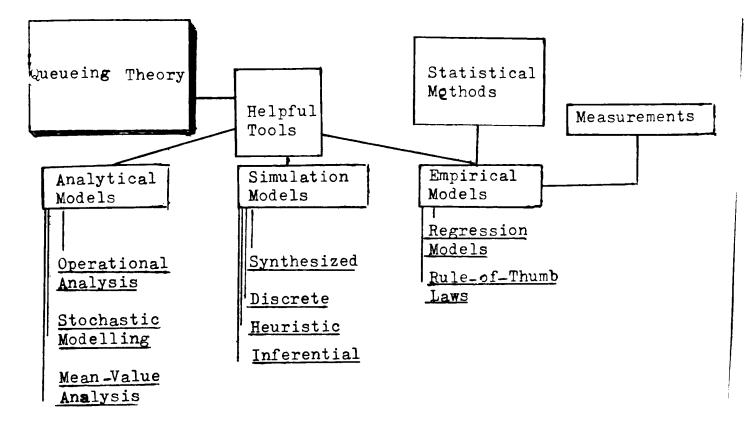

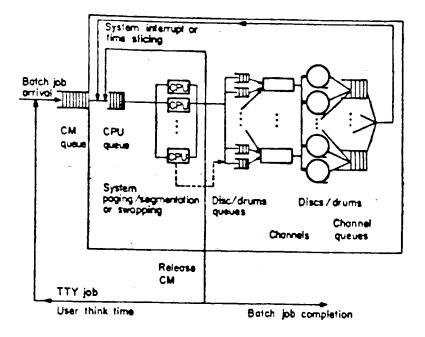

| 3.1           | Queueing Theory Based Models                                                           | 58         |

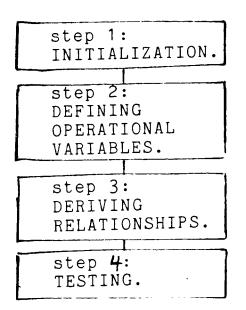

| 3.2           | The Operational Method.                                                                | 62         |

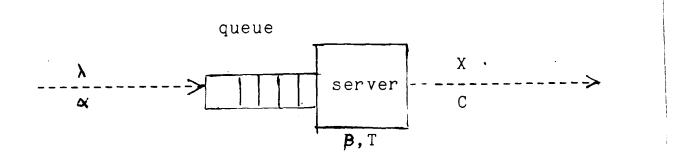

| 3.3           | Single Server System                                                                   | 64<br>63   |

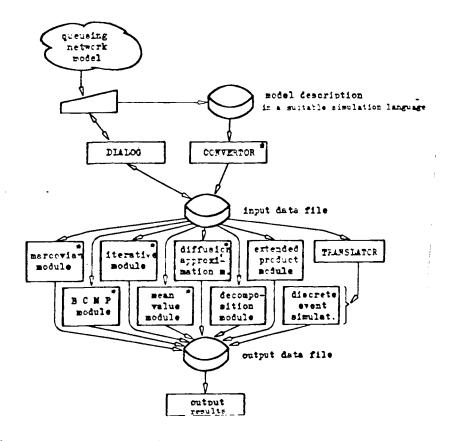

| 3.4           | An Example of Queueing Networks Simulation Tools                                       | 68         |

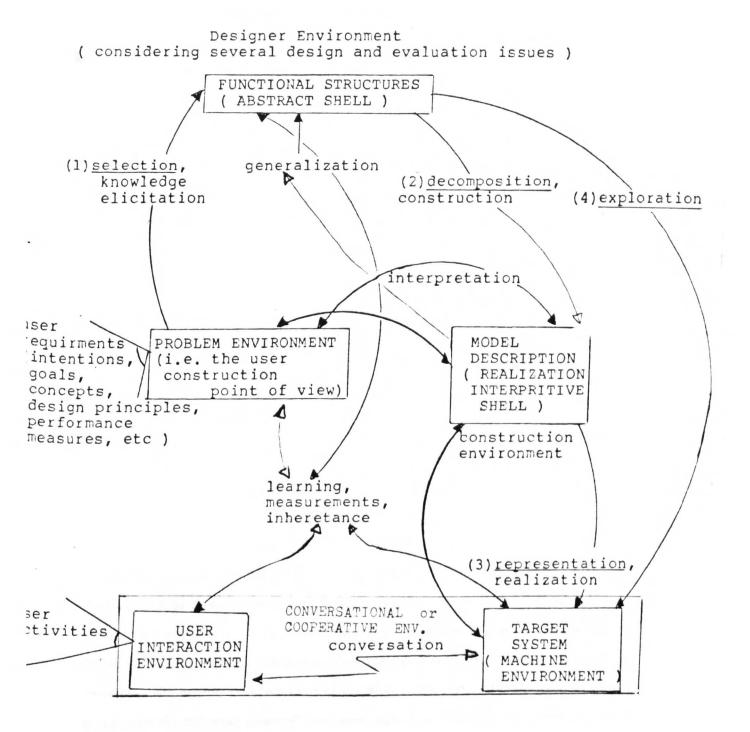

| 4.1           | The Design Scheme of Activity Structures                                               | 81         |

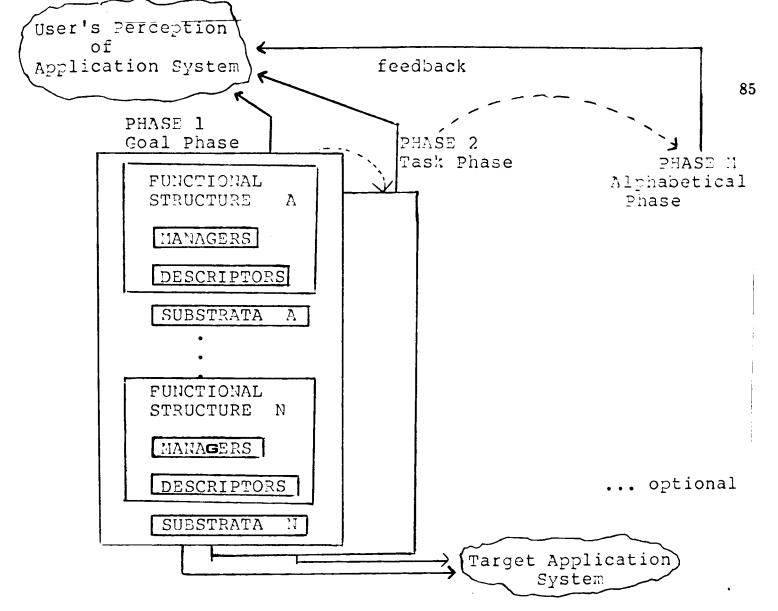

| 4.2           | Partitioning the Development Cycle of Activity Structures.                             | 85         |

| 4.3           | Activity Structures Forms Before and After Realisation                                 | 86         |

| 4.4           | The various exploration changes on a shell                                             | 89         |

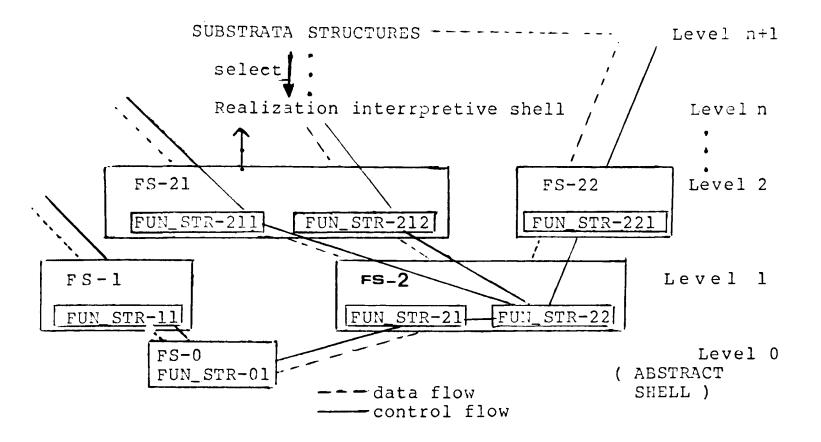

| 4.5           | The Syntactic Decomposition of a functional structure.                                 | 92         |

| 4.6           | The Semantical Statical Description of a functional structure                          | 92         |

| 4.7           | Example of Coroutines achieving Concurrency and Synchronisation.                       | 95         |

| 5.1           | Barber's Model: User Productivity versus the job Satisfaction (Barber 1979, p. 29)     | 102        |

| 5.2           | A General-Purpose Computer Machine Substrata                                           | 103        |

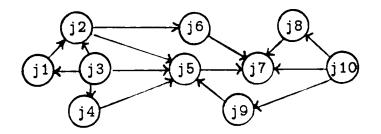

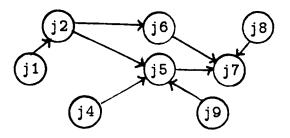

| 5.3           | An Example of a jobs connection settings                                               | 107        |

| 5. <b>4</b> · | Performing The Adaptive-Technique Steps: an example                                    | 108        |

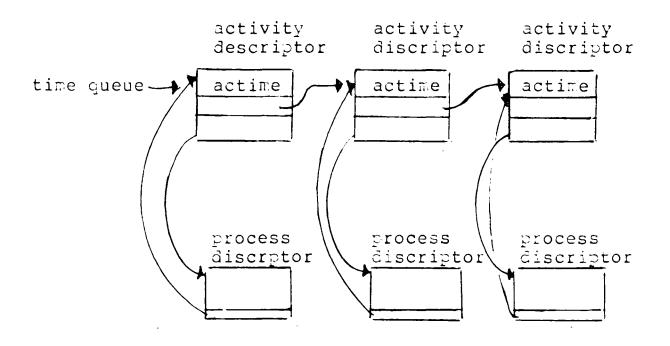

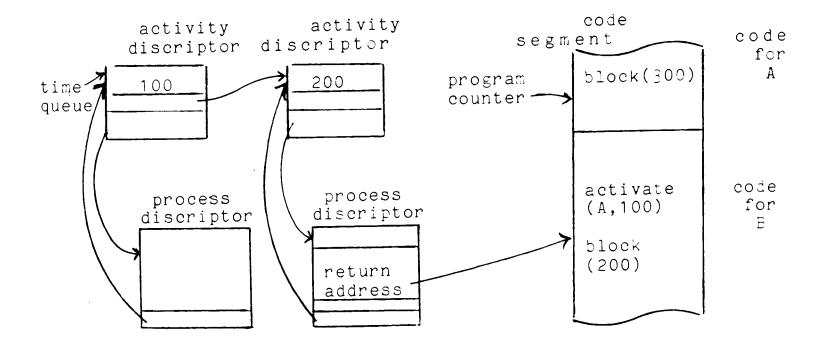

| 5.5           | Activity descriptors and process descriptors                                           | 110        |

| 5.6           | Activity list servicing example                                                        | 111        |

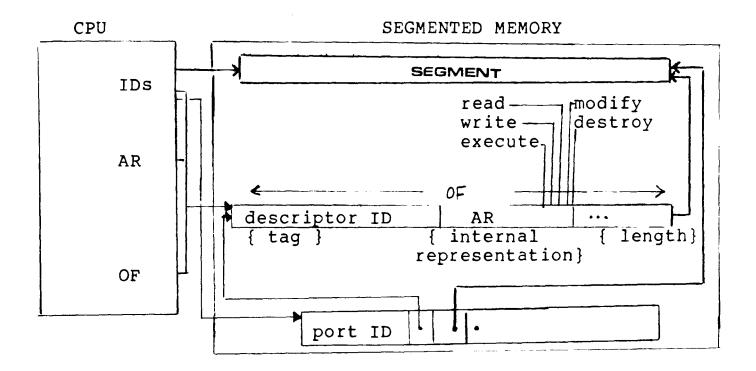

| 5.7           | Featuring the mechanism for generating our descritor-oriented architecture             | 115        |

| 5.8           | The memory based inferential mechanism                                                 | 117        |

| 5.9           | The shape of the user loss function (the user intention service policy)                | 118        |

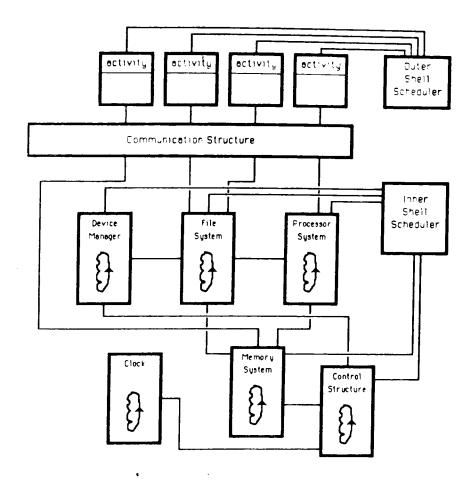

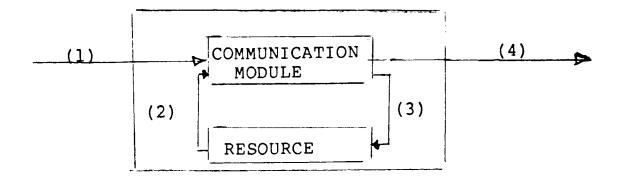

| 5.10          | Kernelised communication distributed modules of a general-purpose computer system      | 120        |

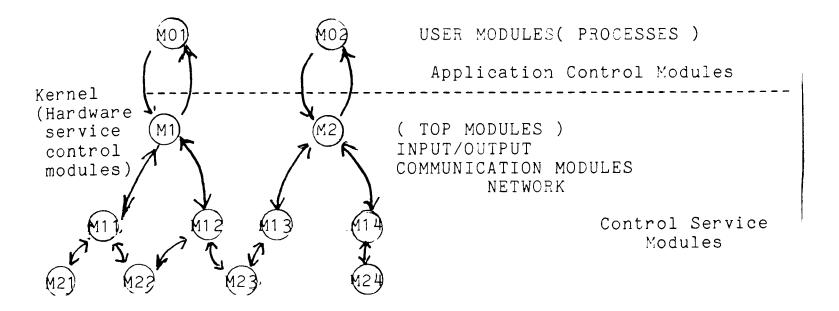

| 5.11 | An abstract view of a communication modules network                                          | 122 |  |  |  |

|------|----------------------------------------------------------------------------------------------|-----|--|--|--|

| 5.12 | The internal structure of a communication module                                             |     |  |  |  |

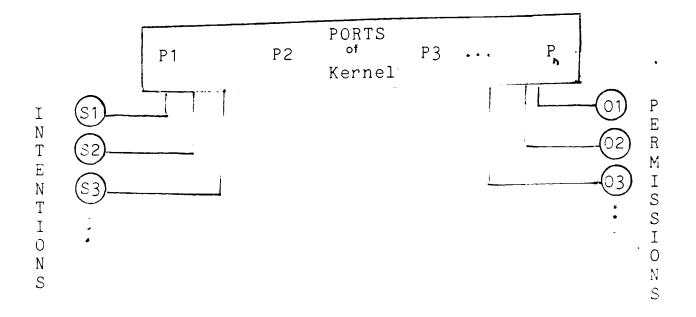

| 5.13 | The Basic Components of our Protection System                                                |     |  |  |  |

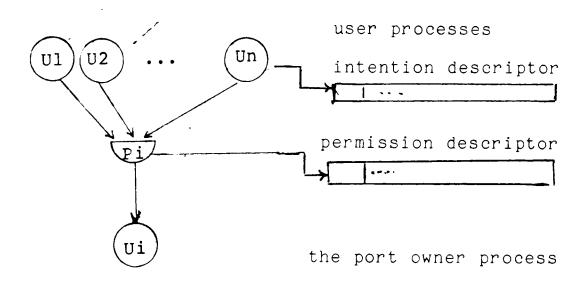

| 5.14 | The Port-Oriented Protection System                                                          |     |  |  |  |

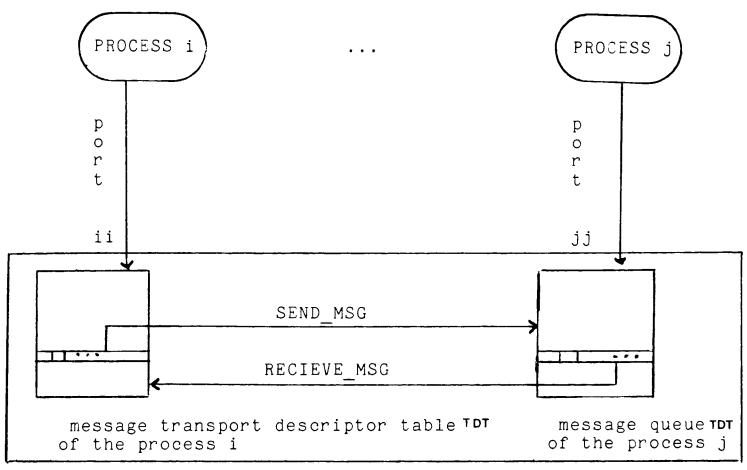

| 5.15 | Interprocess communication mechanism- Communication Parteners                                |     |  |  |  |

| 5.16 | An abstract view of our communication data structures                                        |     |  |  |  |

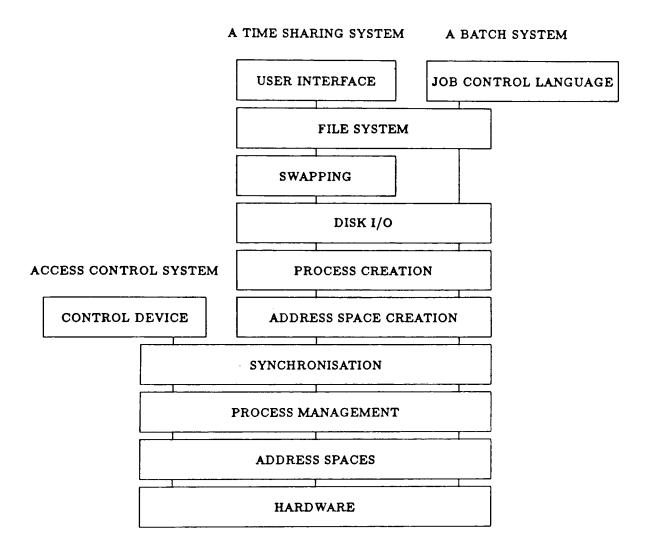

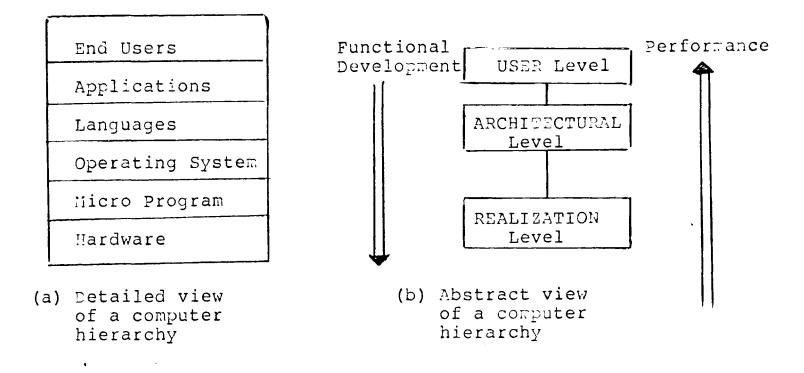

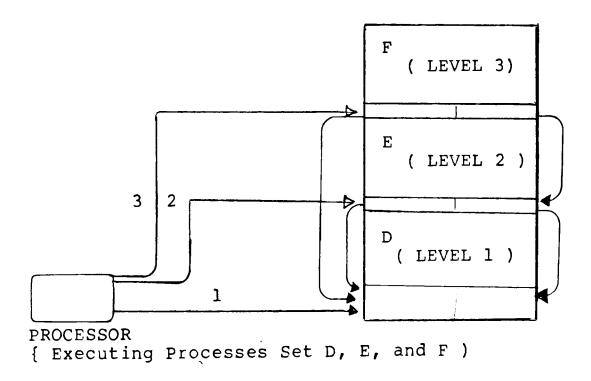

| 5.17 | Hierarchical layers of a computer system                                                     | 131 |  |  |  |

| 6.1  | Fitting the processes of the class of highly constrained systems to the different functional |     |  |  |  |

|      | structures of our generator.                                                                 | 140 |  |  |  |

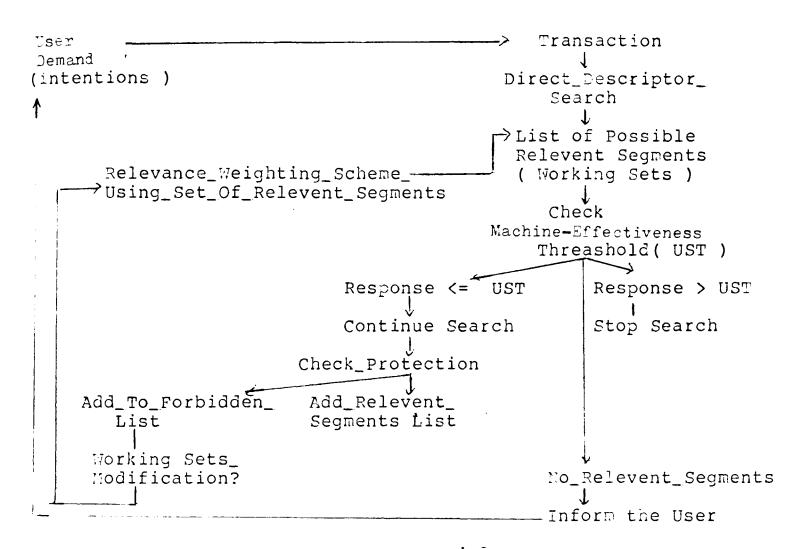

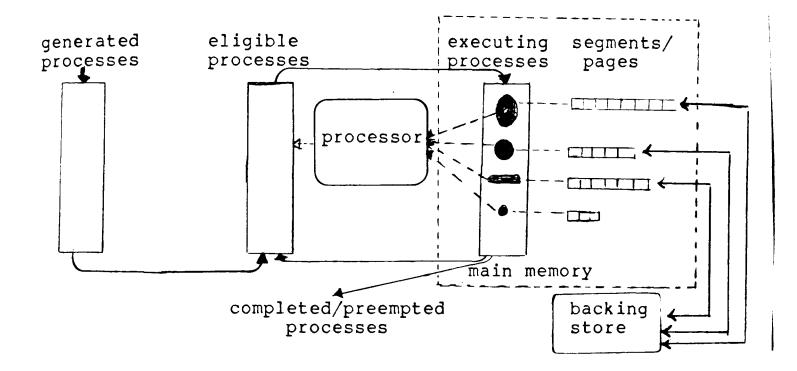

| 6.2  | Schematic view of the scheduling components of                                               | 149 |  |  |  |

| 6.3  | The essential descriptors of the possibilistic generator                                     | 157 |  |  |  |

| 6.4  | Processes Flow in the Two Inferential Components.                                            | 172 |  |  |  |

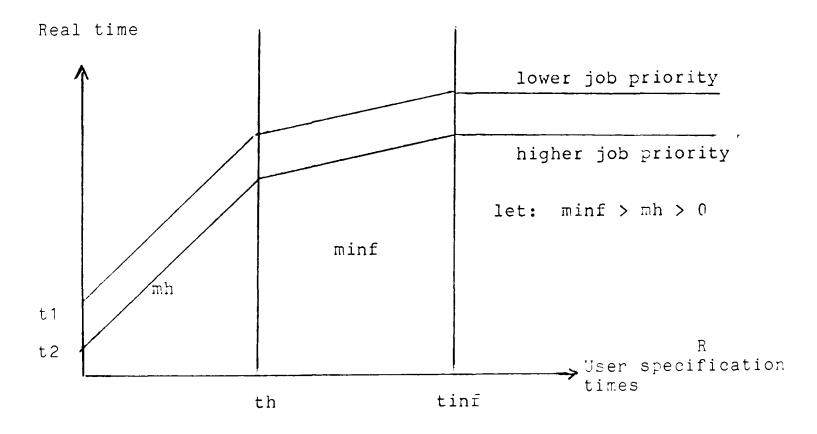

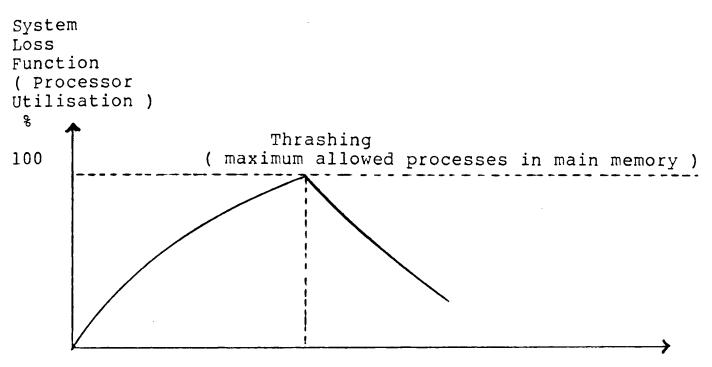

| 6.5  | The System Loss Function                                                                     | 173 |  |  |  |

| 6.6  | Our PLS stack structure                                                                      | 175 |  |  |  |

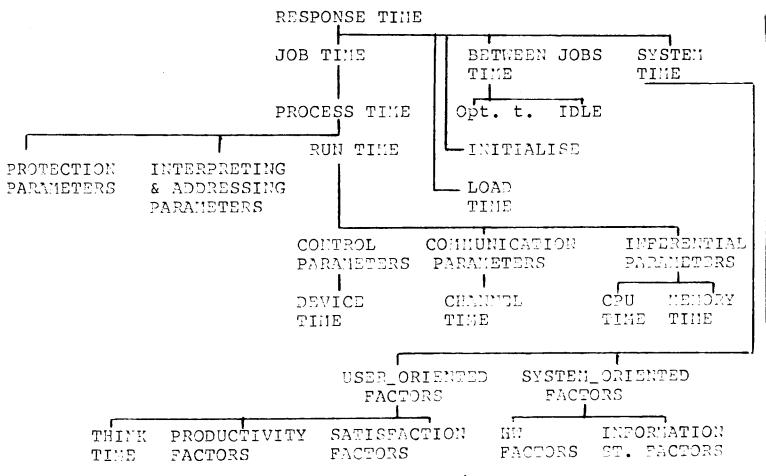

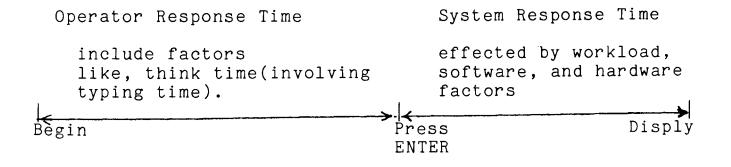

| 7.1  | Factors affecting the response time measure                                                  | 201 |  |  |  |

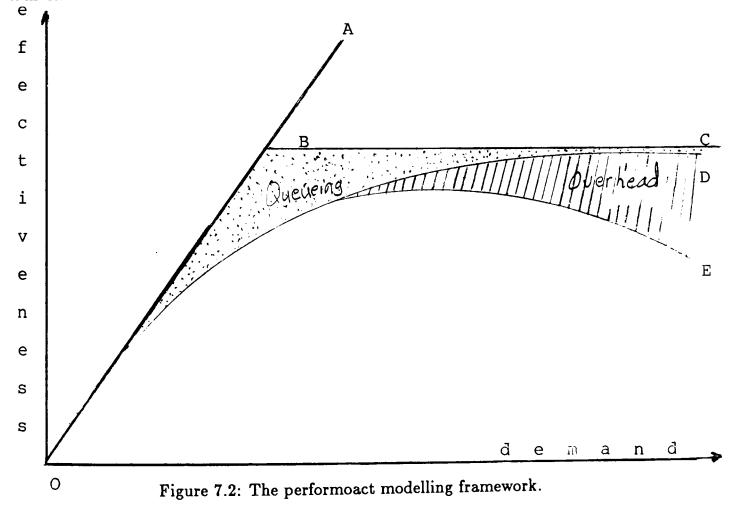

| 7.2  | The performoact modelling framework                                                          | 205 |  |  |  |

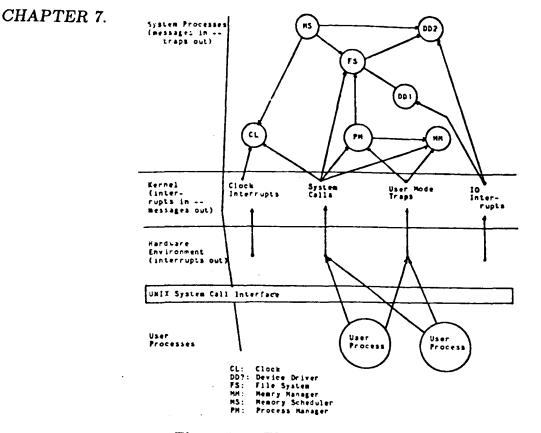

| 7.3  | The Nuke Functional Framework                                                                | 211 |  |  |  |

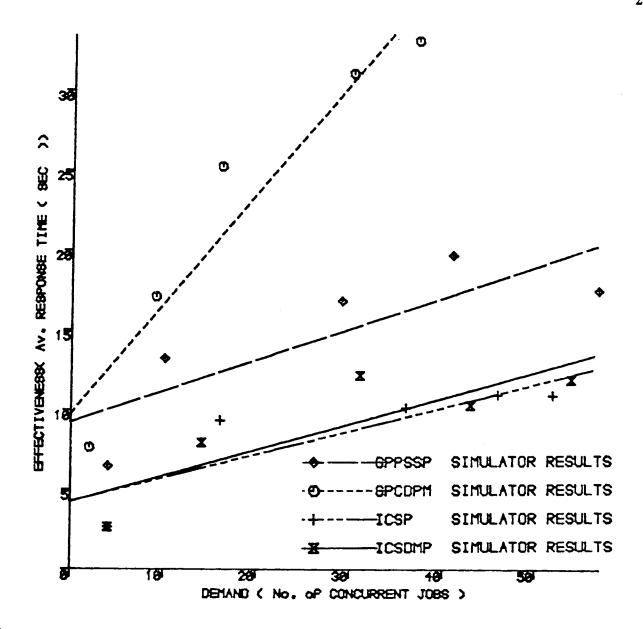

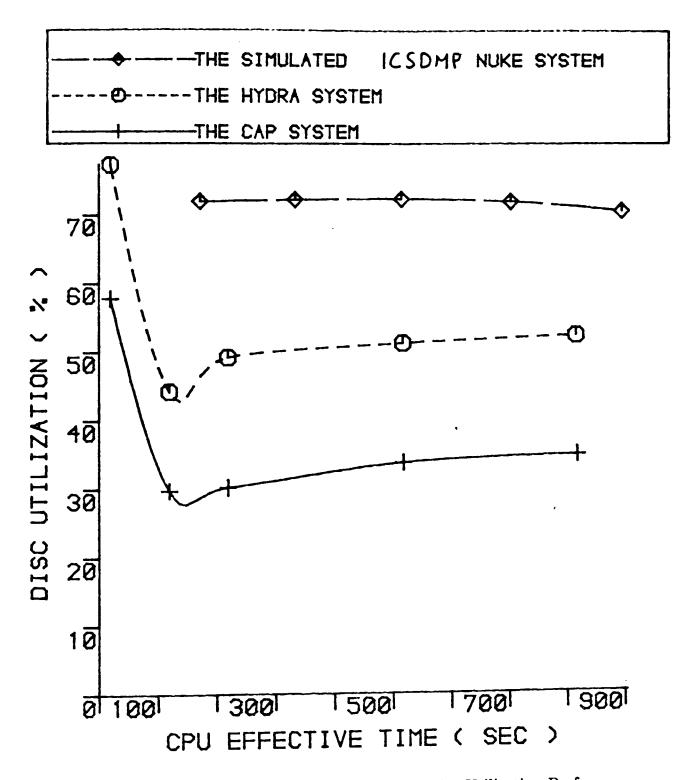

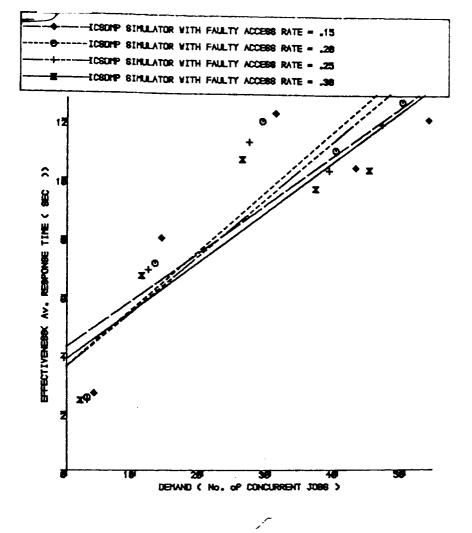

| 7.4  | PERFORMOACT Modelling: Reductions Effects using Average Resource Utilisation                 | 220 |  |  |  |

| 7.5  | PERFORMOACT Modelling: Reductions Effects using Average System Throughput                    | 221 |  |  |  |

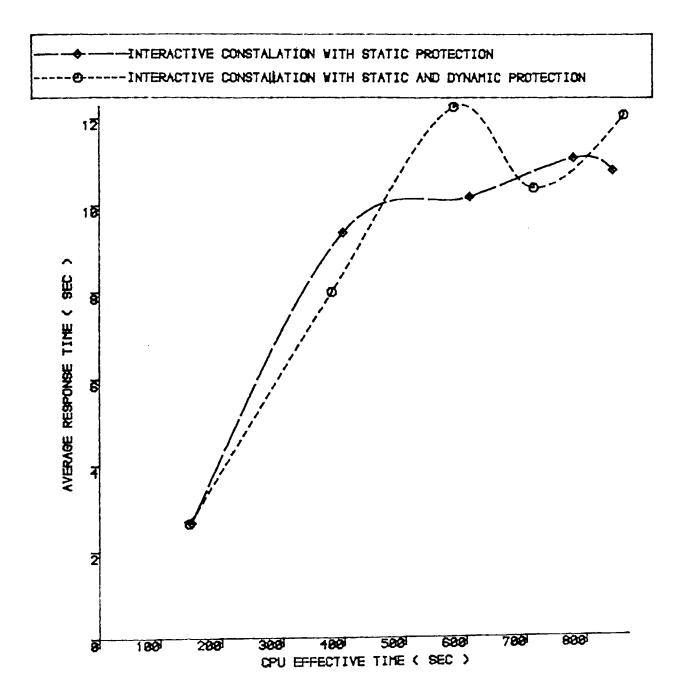

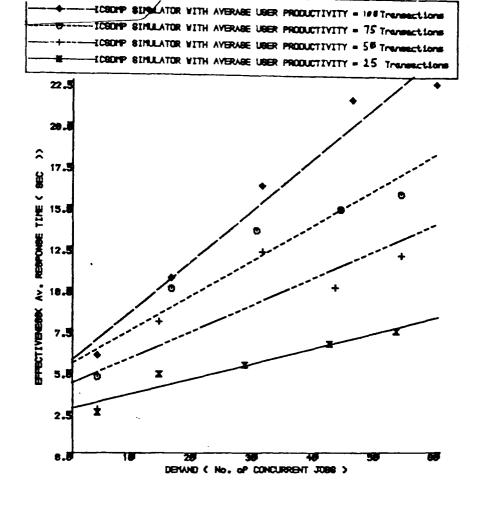

| 7.6  | PERFORMOACT Modelling: Reductions Effects using Average Response Time                        | 222 |  |  |  |

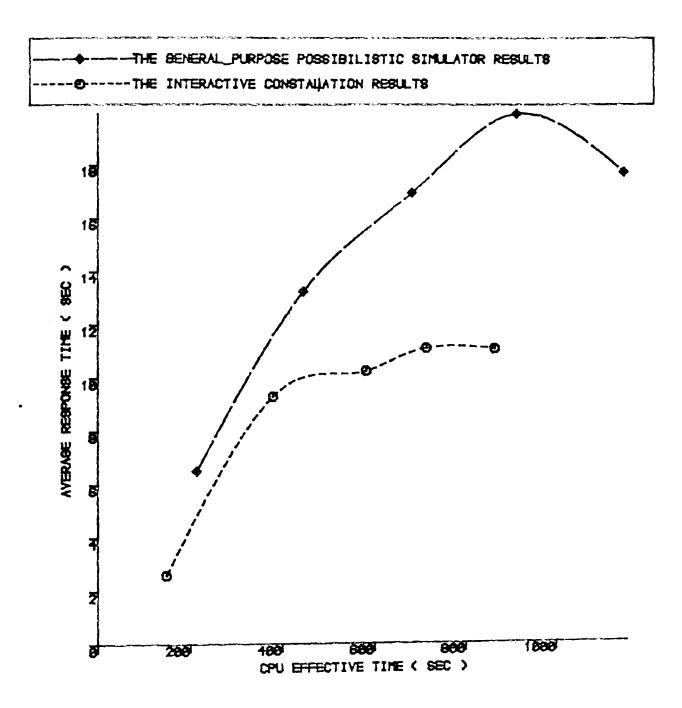

| 7.7  | Adding Dynamic Memory Protection to The Interactive Constellation                            | 226 |  |  |  |

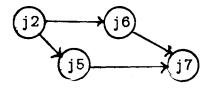

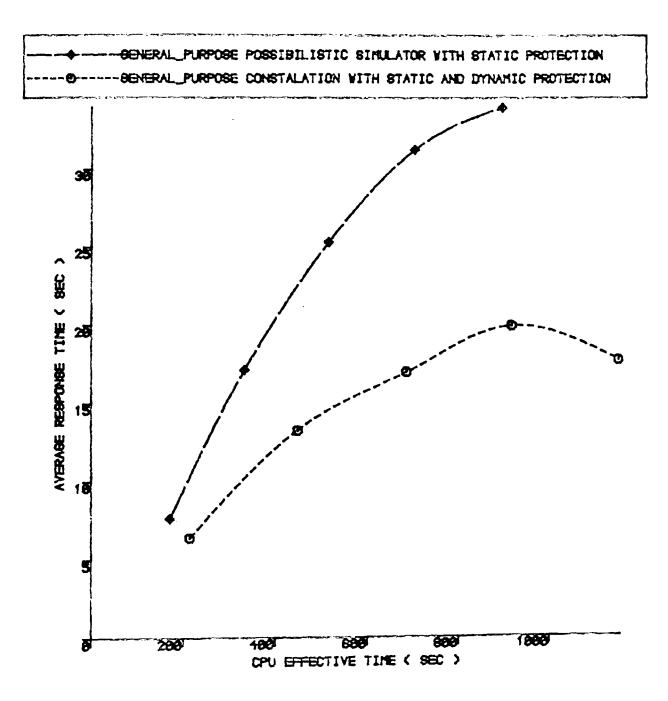

| 7.8  | Reducing The General Purpose Simulator to An Interactive Constellation                       | 227 |  |  |  |

| 7.9  | Reducing GPPS to a GPC with Dynamic Memory Protection                                        | 228 |  |  |  |

| 7.10 | The transaction structure and its contribution to the response time index                    | 229 |  |  |  |

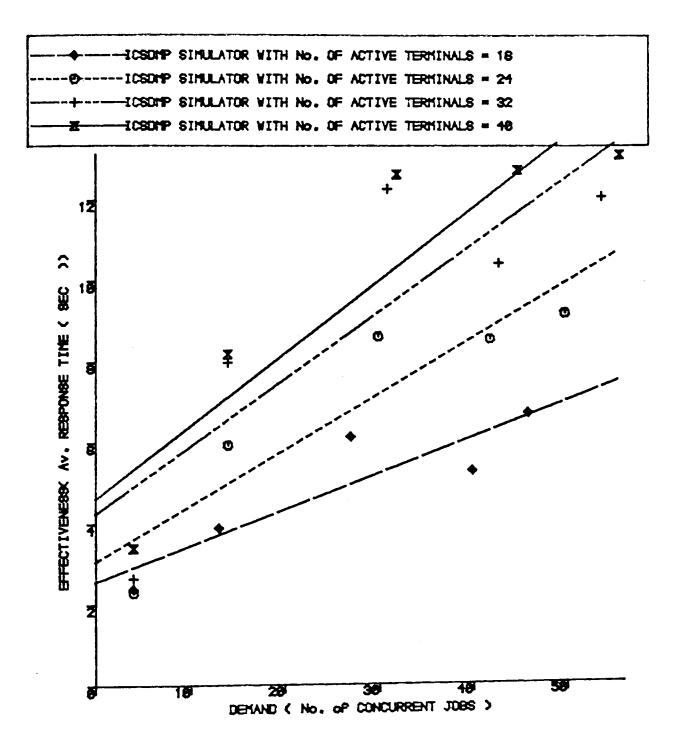

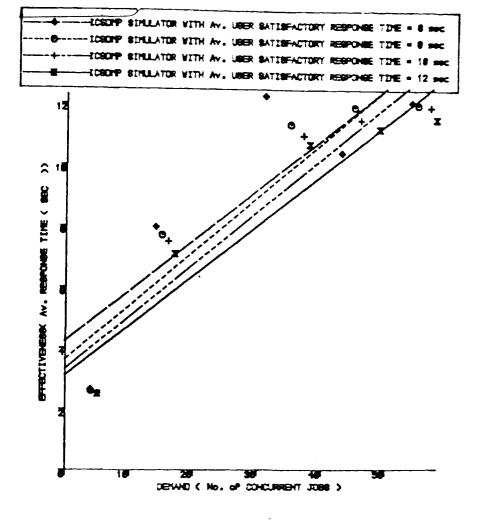

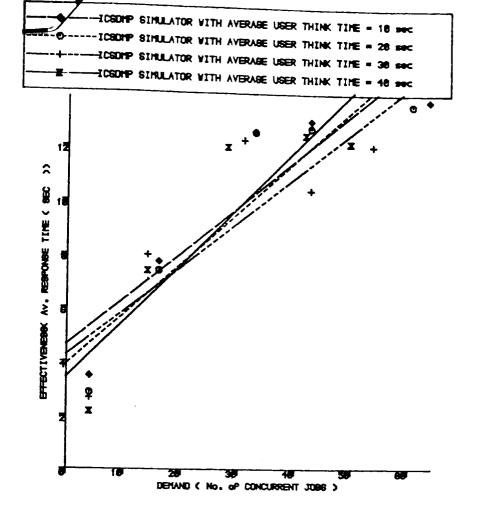

| 7.11 | PERFORMOACT Modelling: The Effects of Adding Terminals                                       | 232 |  |  |  |

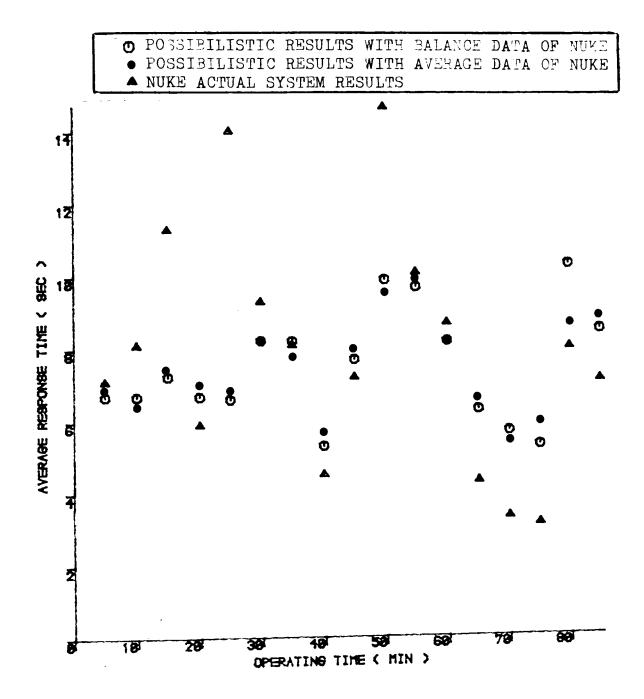

| 7.12 | Simulation vs Real System Results: A Validation Case Study                                   | 236 |  |  |  |

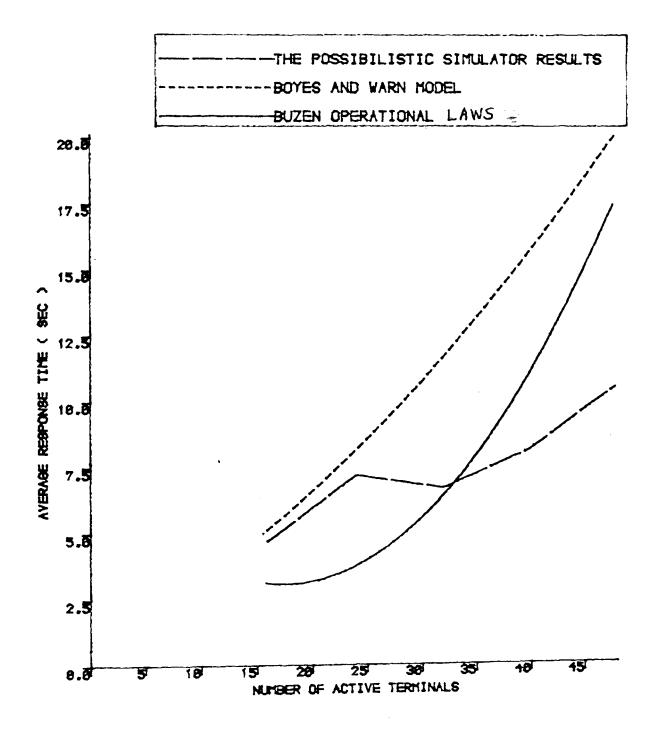

| 7.13 | Validating The Simulator Results with some Theoretical Models                                | 237 |  |  |  |

| 7.14 | A Comparison of Protected Systems Disc Utilisation Performance                               | 238 |  |  |  |

| 8.1  | Design factors of our computer design methodology.                                           | 240 |  |  |  |

•

## LIST OF TABLES

| 1.1 | The six generations of computer systems                                         | 2   |

|-----|---------------------------------------------------------------------------------|-----|

| 2.1 | Various Capability Designs                                                      | 28  |

| 2.2 | The CFA Selected Computer Organisations                                         | 39  |

| 3.1 | Some Less-Used Computer Systems Modelling Theories                              | 56  |

| 6.1 | User Environment Intention Parameters                                           | 141 |

| 6.2 | Conventional Descriptor Mapping Techniques                                      | 164 |

| 6.3 | The Port Map, Where IS : Inferential Structure CS : Control Structures          | 165 |

| 6.4 | Different Processor System Scheduling Policies                                  | 181 |

| 7.1 | NUKE System-oriented Verification Parameters.                                   | 215 |

| 7.2 | The User-Oriented Parameters                                                    | 216 |

| 7.3 | PERFORMACT MODELLING OF THE MAJOR REDUCTION ACTIVITIES USING                    |     |

|     | THE AVERAGE RESOURCES UTILISATION FOR EFFECTIVENESS                             | 223 |

| 7.4 | THE EFFECTS OF THE MAJOR REDUCTION TECHNIQUES UPON THE AVER-                    |     |

|     | AGE SYSTEM THROUGHPUT INDEX                                                     | 224 |

| 7.5 | THE EFFECTS OF THE MAJOR REDUCTION TECHNIQUES UPON THE AVER-                    |     |

|     | AGE RESPONSE TIME INDEX                                                         | 225 |

| 7.6 | Summary of the experimentation                                                  | 230 |

| 7.7 | The Effects of Changing The Average Number of Terminals on The Average Response |     |

|     | Time Index                                                                      | 231 |

|     |                                                                                 |     |

.

•

.

.

## Chapter 1

### INTRODUCTION

### 1.1 Motivation

The human-computer interface is becoming the major component of the success or failure of computer systems. Its improvement is an objective for the fifth-generation (Treleaven and Lima 1982) and the sixth-generation (Gaines and Shaw 1986, 1986a) computing development programmes. Since the start of these programmes, there has been a growing acceptance of opinion in the computer science community that the traditional sequential control flow fourth-generation computers will be superseded in next decade by a new generation of general-purpose computers (see Table 1.1).

There are many factors supporting the adoption of a radically new generation of generalpurpose computers. Firstly, the computional requirement is changing from a sequential and centralised type to a parallel and distributed type. Secondly, the processing tasks performed by the computers are becoming more "intelligent", moving from scientific calculations and data processing to artificial intelligence.

However, today's fourth generation computers are still based on the old von Neumann architecture; all that has happened during this period is that the software systems have been repeatedly extended to cope with the increasingly sophisticated applications.

To overcome the above limitation we had to consider the Human-Computer interaction in the case of the computer design. We are posed with the question,

Can we achieve a relativistic synthesis in the field of computer systems design

| Generations                            | Ezample                           | Bare H.W. | Functional Features                                                                                              | Problems                                                              |

|----------------------------------------|-----------------------------------|-----------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| FIRST                                  | UNIVAC I                          | Valves    | Bootstrap Software,                                                                                              | No resource                                                           |

| 1946-                                  |                                   |           | Machine Code                                                                                                     | sharing,                                                              |

| 1956                                   |                                   |           | Software                                                                                                         | User could                                                            |

|                                        |                                   |           |                                                                                                                  | destroy the                                                           |

|                                        |                                   |           |                                                                                                                  | bootstrap                                                             |

|                                        |                                   | ĺ         |                                                                                                                  | Software,                                                             |

|                                        |                                   |           |                                                                                                                  | Bad performance                                                       |

|                                        |                                   |           |                                                                                                                  | (Speed: 10 kips;                                                      |

|                                        |                                   |           |                                                                                                                  | Space: 1 kbyte)                                                       |

| SECOND                                 | IBM 7000                          | Trans-    | Monitor Software,                                                                                                | Poor performance                                                      |

| 1957-                                  |                                   | istors    | Logical I/O                                                                                                      | (200 Kips;                                                            |

| 1963                                   |                                   |           | devices,                                                                                                         | 32 kbyte),                                                            |

|                                        |                                   |           | library functions,                                                                                               | Monoprog-                                                             |

|                                        |                                   |           | user at a time,                                                                                                  | amming,                                                               |

|                                        |                                   |           | overlayed memory,                                                                                                | No protection                                                         |

|                                        |                                   |           | H.L. Languages                                                                                                   | assumed                                                               |

| THIRD                                  | IBM 360                           | IC        | Operating System,                                                                                                | Low performance                                                       |

| 1964-                                  |                                   |           | Multiprogramming,                                                                                                | (5 Mips;                                                              |

| 1981                                   |                                   |           | Protection,                                                                                                      | 2 Bbyte),                                                             |

|                                        |                                   |           | Timesharing                                                                                                      |                                                                       |

| FOURTH                                 | IBM 370                           | VLSI      | Concurrency,                                                                                                     | Low reliability                                                       |

| 1982-                                  |                                   |           |                                                                                                                  | Good performance                                                      |

| NOW                                    |                                   |           |                                                                                                                  | unless                                                                |

|                                        |                                   |           |                                                                                                                  | protection is                                                         |

|                                        |                                   |           |                                                                                                                  | enforced                                                              |

|                                        |                                   |           |                                                                                                                  | (50 Mips;                                                             |

| FIFTH                                  | Not                               | ULSI      | Functional Prog-                                                                                                 | 8 Mbyte)<br>Empirical                                                 |

|                                        |                                   | 0131      | •                                                                                                                | •                                                                     |

| -                                      | Implemented                       |           |                                                                                                                  |                                                                       |

| 19/9                                   |                                   |           |                                                                                                                  | -                                                                     |

|                                        |                                   |           |                                                                                                                  | Inter action (1101)                                                   |

| SIXTH                                  | Not                               | ULSI      |                                                                                                                  | No apparent                                                           |

|                                        | +···                              |           | 1 ÷                                                                                                              | 1                                                                     |

| 1986                                   |                                   |           |                                                                                                                  | F                                                                     |

|                                        |                                   |           | diverse fields                                                                                                   |                                                                       |

|                                        |                                   |           |                                                                                                                  |                                                                       |

|                                        |                                   |           |                                                                                                                  |                                                                       |

|                                        |                                   |           |                                                                                                                  |                                                                       |

|                                        |                                   |           |                                                                                                                  |                                                                       |

| Proposed<br>1979<br>SIXTH<br>Propossed | Implemented<br>Not<br>Implemented | ULSI      | ramming,<br>Natural Languages,<br>Speech,<br>Vision,<br>Better design<br>using theoretical<br>models of HCI from | Models of<br>Human-Compu<br>Interaction(HC<br>No apparent<br>problems |

Table 1.1: The six generations of computer systems

via the paradigm of general or meta systems methodologies?

This was the point of departure for several researchers of the development of effective foundations of research in this area (notably Antonin Svoboda, Brian Gaines, Ladislav Kohout and Wyllis Bandler) which led me to develop a new approach for designing general/meta systems-oriented computer models. The fundamental element of these theories is the triplet

(SYSTEM MODEL, DESIGN PROBLEM, DESIGNER)

The essential ideas that have been used in the thesis for the construction of computer

system models, which can include both the computer user behaviours and the designer activities, were given by Ladislav Kohout in a series of research papers (starting in 1974 and still evolving, e.g. Kohout 1986) establishing a methodological approach for the study of actions of natural and artificial systems (named in 1979 as the activity structures methodology).

Historically, the research in Activity Structures methodology emerged from Neuroscience research, aiming at providing techniques for capturing the diverse knowledge sources and can be used to model/analyse the "deep knowledge" of this application field in an effective formal and/or computer representable form.

The view in this thesis is that activity structures framework is an approach which can be used to construct  $total^1$  information processing systems which support the self-regulating<sup>2</sup> architectures whose processing environments can be dynamic and operate under maximal constraints<sup>3</sup>. Note that this definition is not identical to the original definition of Kohout:

"The design framework of the Activity Structures provides the means for identifying

the necessary processing environments. It also provides the structures, as well as

their linkage interfaces, that are seen to be essential for supporting a successful

<sup>2</sup> Self-regulating is the behaviour which reaches a stable condition of satisfactoriness. The machine environment may reach a stable condition of satisfactoriness, when initially the performance of the machine environment oscilates (because of the interaction with the user environment) between the acceptable and non-acceptable, with respect to some predefined thresholds, but it must finally become acceptable and remain so. In this condition we may say that the machine environment has become "adapted" to the user environment activities. The user environment may aslo behave in a self-regulating manner. In a similar way we may define the user environment self-regulation.

<sup>3</sup>In a maximally constrained system the interaction between the user environment and the machine environment is restricted to one degree of freedom only, i.e. only the cooperation behaviour is allowed between these two environments. The reason for such a restriction is given by the fact that with cooperation, the self-regulating behaviour can be ensured simultaneously within both environments. This is in contrast to the effects of the competion behaviour in which only one environment may behave in a self-regulating manner. However, a distiction should be made between a maximally constrained system in which cooperation behaviour is enforced at all times, and a highly constrained system; the type of interactions at the initial stage do not matter and only after the system leaves the initial stage the interaction must be forced to be of the cooperation type. A slightly different definition of the criterion of maximal constraints is given by Rosen (1986).

<sup>&</sup>lt;sup>1</sup> A total system can be described as a finite set of rules which integrates the design and constraint functional structures with the substratum structures. The functional structures represent coherent goal-oriented segments of behaviour. Each functional structure identifies a specialised domain of the total system activities. These can be classified into primary structures of activities (design modules/structures) identifying the essential activities of the primitive design, and the secondary structures of activities (constraint modules/structures) identifying the constraints imposed on the primary activities c.f. Kohout 1986). The substratum structures represent fragments of the code and data used for the realisation/simulation of the functional structures (c.f. Kohout 1986).

design" (Kohout 1984).

#### However,

"the growing area that concerns the design of total systems still needs a broader and formal foundation, more automation, and a higher level of integration into the overall design and realisation process." (Roman et al 1984)

The purpose of this thesis is to introduce an effective approach for the construction of total computer systems based on the activity structures methodology. The reasons for focusing our attention on achieving this purpose came from the examination of current experience in the design of total computer systems operating under maximal constraints. A summary of results is given below:

Constraint structures enforcement is by no means an inconsequential problem. Constraint structures have become an important and challenging goal in the design of computer systems. Constaint structures comprise engineering and managment activities imposed on the functionalities of the basic design of a computer system. For example the enforcement of a protection constraint structure is ligitimately of major concern.

"At present the effecient implementation of protection system presents difficulties and further research is called for." (Wilkes 1984)

2. There is no successful highly constrained computer system.

"To date, most systems designed to include constraints such as protection in computer systems have exhibited either slow response times or awkward user interface or both." (Landwehr 1981)

"Although variety of improvements have been introduced to the structure of certain advanced computer systems (e.g. by using parallel architectures), the resulting systems have suffered from complexity in both the use and understanding." (Bic 1982) 3. A total system design framework is needed to overcome the system inadequacies that might be the fault of the designers who did not look at the whole picture including the constraint structures at each design stage.

"To be successful, a design must merge hardware and software functionalities into a single, unified perspective." (Roman et al 1984).

4. Not every design framework can be effective.

"The form of the design framework representation may affect the various design tasks." (Gaines 1974)

5. Design must start right from the first steps.

"Many computer systems (e.g. B6700, ROLM 1664) failed to meet the user requirements owing to the inadequacy of the original system representation." (Dietz and Szewerenko 1979)

6. Design must not concentrate only on the actual products but it should consider the human factors.

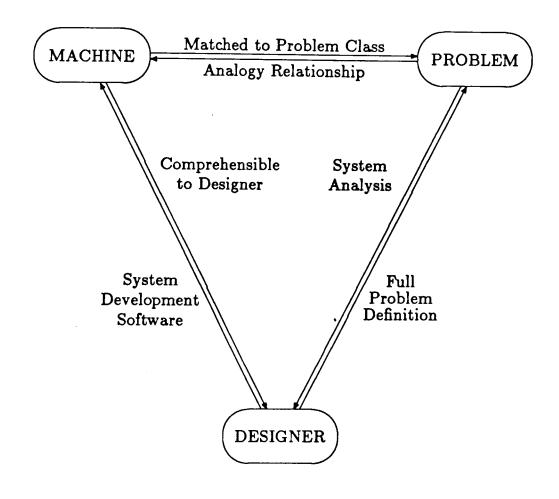

"An adequate design methodology for designing computer systems should capture the basic design trajectory, involving the three design relationship between computer, problem, and designer." (Gaines 1973)

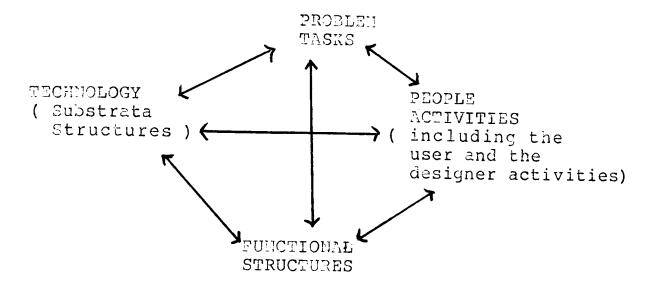

Figure 1.1 illustrates Gaines design triangle.

Figure 1.1: The essential elements of successful computer design methodologies.

7. To delegate the design activities in 6,

"numerous schemes must be formalised first; to a considerable extent we must formalise those human activities that contribute to the design." (Mills 1985)

Such efforts, however, have been largely fragmented within the science paradigm<sup>4</sup>

"there has been little discourse between mainstream computer scientists, Al

<sup>&</sup>lt;sup>4</sup>The science paradigm can be described as a 'learning system' characterised by reductionism, repeatability and refutation (Checkland 1976).

theorists, system developers, communication engineers, and so on. A general theory of design, and its relationship to human knowledge and activity, would help us to relate these theoretical fragments and to judge their worth, but no such coherent methodology or theory has emerged." (Tully 1985)

Capper (1986) expressed similar opinion.

8. In contrast to 7, the success of applying the activity structures approach which is based on principles similar to the more present general/meta systems paradigms<sup>5</sup><sup>6</sup>), motivates me to use and develop the activity structures approach in the realm of effective computer systems design.

Hence, in this research project, we have developed a software tool to simulate many activity structures based computer systems. This is a detailed simulation which replicates the essential capabilities of modern computer systems and provides those activity structures mechanisms that are required for self-regulation. This tool supports a methodological approach for designing maximally constrained, high-performance computer systems that provide elegant solutions to several problems which previous attempts have handled only in an ad hoc fashion.

Indeed, in implementing the support tool for activity structures based computer systems, the aim is not only to show the applicability of the method presented. We also have to demonstrate the feasibility of writing a support tool for such systems in a highlevel language, to develop a comprehensive and effective methodological approach to the construction of computer system architectures, and devise some techniques for aiding the process of exploring and evaluating these architectures.

The software tool described in this thesis consists of the following major components:

<sup>&</sup>lt;sup>5</sup>The general systems paradigm takes into account the indivisibility of systems domains where organised complexity prevails. It originates from concerns that the science paradigm, which was designed to deal with the physical world, breaks down when faced with living systems (Gigch 1979). However, the metasystem paradigm originates in the premise that one cannot arbitrate deficiencies among systems in other than a meta language that is in the language of a metasystem which lies above that of the systems whose is sought (Gigch 1979).

<sup>&</sup>lt;sup>6</sup>Examples of such sucesses in the construction of sophisticated information processing systems include expert systems (Kohout and Bandler 1982, Kohout et al 1984, Mohamad et al 1983), a decision support system (Kohout et al 1985, Ohiorenoya and Mohamad 1983).

- 1. preprocessor for eliciting the design information from the designers wishing to construct activity structures based computer architectures,

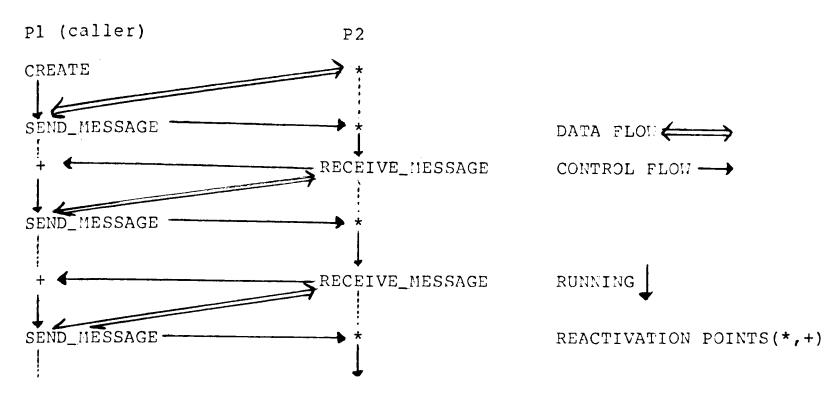

- 2. subsystem simulating the user intentions and his/her learning capabilities for the purpose of generating the user interaction environment.

- 3. a subsystem simulating the machine activities (i.e. traps and interrupts) and learning, for the purpose of generating the machine environment.

- 4. a highly parameterised shell which provides the designer with the essential design and functionality constraint modules (called the functional structures). These modules are linked in a distributed fashion (i.e. message-passing) and consist of:

- (a) Design Modules : These represent the essential functional structures needed for producing the primary activities of the computer system. These are:

- i. Knowledge representation structures,

- ii. Inferential structures,

- iii. Control Structures,

- (b) Constraint Modules : These represent the secondary activities imposed on the primary activities. These consist of the following functional structures:

- i. Protection structures,

- ii. Communication structures,

- iii. Interpretive structures.

The structures (4(a)i, 4(a)ii, 4(a)iii and 4(b)i) were introduced and used by Kohout (c.f. Kohout 1986, Kohout and Bandler 1986) in the designs based on his activity structures framework; communication structures he used only in the context of protection, and I extend their use in this thesis to other domains. Interpretive structures constitute my original contribution to the Activity structures framework.

The flexibility of the proposed tool allows the designer to explore the variations of any given design by direct experimentation, in order to force it to behave in an interesting way (i.e. to have high-performance).

### **1.2 Terminology and Definitions**

This section contains the essential definitions used later in the text. The reader is also directed to the index.

- ACTIVITY STRUCTURES METHODOLOGY: The activities of the designer that are essential for the construction of activity structures based computer systems.

- THE DESIGNER ACTIVITIES: The process of dealing with the problem of the design and construction of computer systems. This process involves four design steps: selection, decomposition, realisation, and exploration (see section 4.6).

- ACTIVITY STRUCTURES BASED MODEL OF A COMPUTER SYS-TEM: A total model of a computer system which incorperates the user and the machine environments (c.f. footnote number 1 of page 3 of this chapter). In this model the interaction between the user environment and the machine environment is maximally constrained. The implementation of this model is called the complete shell.

- MAXIMALLY CONSTRAINED BEHAVIOUR: The cooperation behaviour between the user environment and the machine environment which is restricted to one degree of the freedom of interaction.

- COOPERATION BEHAVIOUR The interaction which reaches a stable condition of satisfactoriness.

- USER ENVIRONMENT A user oriented possibilistic automaton that updates its demand probabilities on the basis of the resulting machine environment performance, so that it chooses asymptotically the optimal demand. The implementation of this environment is called the *outer shell*. The updating criterion is referred to as the user environment self-regulation (c.f. foot note number 2 of page 3 of this chapter).

- MACHINE ENVIRONMENT: A machine oriented possibilistic automaton that controls its performance on the basis of the required user environment demand, so that it asymptotically reaches the optimal performance. Its implementation is called

the *inner shell*. The control criterion and in this context is referred to as the machine environment self-regulation (c.f. footnote number 2 of page 3 of this chapter.

- USER POSSIBILISTIC AUTOMATON: A highly-parameterised user model stochastic automaton which generates the user demands and is connected in a feedback loop with the machine environment.

- MACHINE POSSIBILISTIC AUTOMATON: A highly-parameterised and extensible *computer system model* stochastic automaton which is connected in a feedback loop with the user environment.

- USER MODEL: This is a statistical model which represents a quadruple  $\langle r, \alpha, p, T \rangle$ where:

| r                                         | total number of user demands. |

|-------------------------------------------|-------------------------------|

| $\alpha = \{\alpha_1, \cdots, \alpha_r\}$ | set of demands of             |

|                                           | the user environment,         |

| $p = [p_1, \cdots, p_r]$                  | demand probability vector of  |

|                                           | the user environment,         |

| Т                                         | an updating operator          |

If  $\alpha(t)$  represents the demands chosen by the user environment at time t  $(t = 0, 1, \cdots)$ , then<sup>7</sup>

$$p_i(t) = \Pr \left[ lpha(t) = lpha_i

ight]$$

$\sum_{i=1}^r p_i(t) = 1$  for all t

$P(t+1) = T[P(t), a(t), b(t)]$

$\beta(t)$  is the binary set of performance reactions from the machine environment the same as input to the user environment such that

$$\beta(t) \in \{0,1\}$$

• The input to the user environment  $\beta(t) = 1$  is called the penalty performance input and  $\beta(t) = 0$  the reward performance input. The penalty probability vector

$$egin{aligned} c &= [c_1, \cdots, c_r] & ext{has the following property} \ c_i &= \Pr\left[eta(t) = 1 \mid lpha(t) = lpha_i

ight] \end{aligned}$$

<sup>&</sup>lt;sup>7</sup>Note: These probabilities are produced in our implementation by two types of distributions and the user model is simulated by two routines PARTICIPANT-ONE and PARTICIPANT-TWO

The average penalty M(t) that the user environment receives from the machine environment is given by

$$M(t) = E[\beta(t) | p(t)]$$

$$= \sum_{i=1}^{r} p_i(t)c_i$$

The operator T represented by an algorithm called the updating (or user adaptive) algorithm. The user adaptive algorithm can be expressed by the formula

$$M(0) = \frac{1}{r} \sum_{i=1}^{r} c_i$$

such that

$$\lim_{t\to s} E[M(t)] \leq M(0)$$

where s is the observation time limit.

• COMPUTER SYSTEM MODEL: This is a simulation model which is partly driven by itself and partly driven by the outer shell. This model represent a quadruple (FS, ST, UD, PCR), where

**FS:** FUNCTIONAL STRUCTURES

**ST:** SUBSTRATUM STRUCTURES

**UD:** USER DEMAND

**PCR:** PERFORMANCE AND CHANGES REQUIREMENTS.

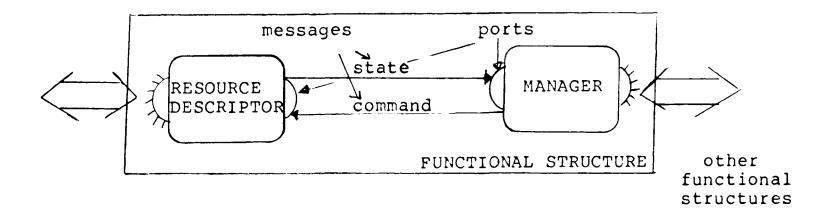

• THE COMPUTER SYSTEM FUNCTIONAL STRUCTURES: These are coherent goal-oriented segments of behaviour. Each functional structure represents a specialised domain of computer system activities. This leads to communication and exchange of knowledge between the domains. Each functional structure represents an algorithm that updates some activities. In addition to the module that traps the user demand and generates the intention steps (i.e.the external interrupts) and is called the PROCESS GENERATOR, there are other two main types of functional structures used here, the design structures and the constraint structures.

- DESIGN FUNCTIONAL STRUCTURES: These represent the essential functional structures needed to produce the primary activities of a computer system. These are

- 1. the Information Structures (c.f. section 5.3.1),

- 2. the Inferential Structures (c.f. section 5.3.2), and

- 3. the Control Structures (c.f. section 5.3.3).

- CONSTRAINT FUNCTIONAL STRUCTURES: Represent the secondary activities imposed on the primary activities. These consist of the following structures:

- 1. the Protection Structures (c.f. section 5.3.4),

- 2. the Communication Structures (c.f. section 5.3.5), and

- 3. the Interpretive Structures (c.f. section 5.3.6).

- THE SUBSTRATA STRUCTURES: These are the fragments of code and data simulating the implementation dependent responses (in absence of the real hardware). These responses in our implementation(i.e. internal interrupts) are generated by the job scheduler routine.

- USER DEMAND: This is the average user demand, expressed by the number of concurrent tasks or processes placed by the user environment. This measure implicitly identifies the user environment average panalty (demand / number of active terminals).

- PERFORMANCE AND CHANGE REQUIREMENTS: These are the measures used to monitor the performance of the modelled computer system model activities via the software probes. There are two types of measures that can be used to assess the average panalty of the machine environmen. These are: the average response time for an interactive system, and the average system throughput for the general system. The change requirements include the designer changes on the computer system model introduced in order to achieve a target computer system. The

change that involve the algorithmic non-parametric changes on the original computer system model produce a constelation. The changes that involve the non-algorithmic changes (i.e. parametric changes) on the original model or on a constelation produce a general system family. The repeated changes on the general system family produce the admissible data that are used to tune the general system to reach the stability state. This tuning procedure is called the performoact modelling.

## 1.3 The Thesis Synopsis

#### **1.3.1** Presentation of the Thesis:

This thesis is concerened with the following topics:

- 1. outlining the problems encountered in some contemporary computing systems that need solution,

- 2. presenting a new design method that can deal with the outlined problems,

- 3. designing and implementing a design support tool based on this new method, and

- 4. validation of this proposed method.

We concentrate on the design of highly constrained multiprocessing computer systems. The aim is to produce well- protected systems of high-performance, that can achieve stable dynamics of user-computer interaction. A more precise statement of the problem and further discussion of the origin of the problem, its significance and its motivations are discussed in chapter 1.

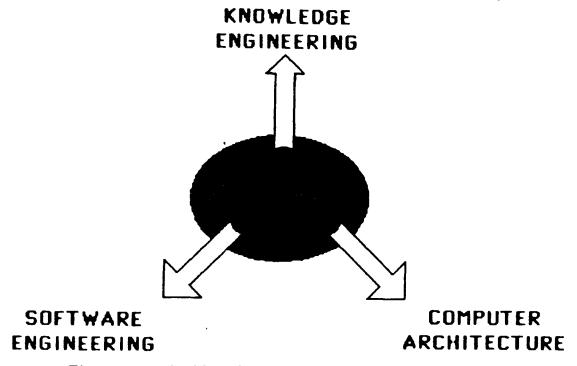

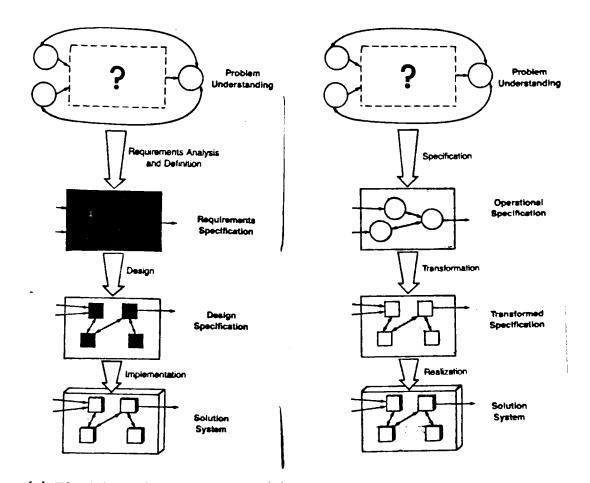

Chapter 2 critically surveys the current design techniques that are available within the three major computer science design fields. Namely, software engineering, knowledge engineering, and computer architecture. Chapter 3 critically reviews the current theoretical approaches, dealing with computer design, and pinpoints their inadequacies.

**Chapter 4** presents the conceptual framework which forms the foundation of the proposed design method. This framework is arrived at by analysing the activities of the designer by the means of Activity Structures approach. **Chapter 5** outlines new essential structures which we need in the design of the complete shell of the tool, the design of which is also derived here. and Chapter 6 describes the details of the implementation of the design tool. Chapter 7presents the so called *performoact modelling*, a new framework for evaluating a computer performance and for selecting those sets of the design data thatforce acceptable performance. Within this framework, the evaluation of the design tool is carried out.

#### **1.3.2 CHAPTER 2:**

INVESTIGATING THE EXISTING TECHNIQUES FOR CONSTRUCTING COMPUTER SYS-TEMS

In an effort to deal with the problem of designing effective maximally constrainted computer systems, we surveyed the "computer architecture", "software engineering", and "knowledge engineering" fields as they were considered to be relevant to the overall problem (see section 2.1). These fields provide the design techniques relevant to the construction of effective complex computer system designs, since they capture the results and accomplishment of research in various parts of the computer science (see sections 2.2, 2.3, and 2.4). In this chapter we investigate the role of each field in constructing effective computer systems and conclude that the techniques provided by these fields are largely fragmented and there is very little discourse between the workers of these three fields. Hence, there is no widely accepted or even practiced methodology that outlines the construction discipline which would link effectively together the methods of these three fields (see sections 2.5 and 2.6).

#### **1.3.3 CHAPTER 3:**

AN OVERVIEW OF THE EXISTING THEORETICAL APPROACHES FOR DESIGNING COM-PUTER SYSTEMS

In this chapter we investigate the role of the existing theoretical approaches in the area of designing effective computer systems. We conclude that there is no effective design theory. Indeed, the current conventional building blocks of scientific theory, the theoretical and methodological constructs as well as the mathematical formalisms, have made it difficult to conceive of the possibility of a general account of the nature of computer systems design

and its organisation. We have had to rely on the essential notions of physics (time, length, etc.) or else on descriptive analogies taken from ordinary experience in order to describe intelligibly natural phenomena (see section 3.1). The advance of "statistical" sciences (operational research, queueing theory, statistical mechanics and operational analysis, meanvalue analysis, etc.) have led to the new ways of simplifying complex phenomena within an empirically meaningful framework (see section 3.2). Successes in these areas suggest that behind the formidable complexity of nature there is actually a surprisingly small number of simple relations governing interactions; the difficulty has been to refine several theories to the point where such relations could emerge clearly. Hence, the road to understanding the behaviour and predicting the performance of computer systems has been, and still is, arduous. Sections 3.2.1, 3.2.2, and 3.2.3 review the main theoretical models based on the Queueing theory for designing computer systems.

#### **1.3.4 CHAPTER 4:**

ACTIVITY STRUCTURES AS A METHODLOGICAL APPROACH FOR CONSTRUCTING EF-FECTIVE COMPUTER SYSTEMS

In this chapter we introduce a methodology approach for designing effective computer systems. This approach is based upon the use of the activity structures design concepts. This methodological approach provides total computer system designs which support selfregulating architectures whose processing environments are dynamic (i.e. changing) and operate under maximal constraints ( see sections 4.1- 4.5). Section 4.6 presents the main design steps of the activity structures. Finally section 4.7 presents the main meta-definitions that are used in the process of the design and evaluation of activity structures based computer systems.

#### **1.3.5** CHAPTER 5:

AN ABSTRACT COMPLETE SHELL FOR THE ACTIVITY STRUCTURES BASED COM-PUTER SYSTEM DESIGNS

The design issues are discussed here which lead to the subsequent abstract description of

an activity structures based complete shell of the support tool. The shell design represents a conceptual model, from which a variety of computer systems can be built. In section 5.2 the cooperation activities of both, the outer shell concerning the user shell, and the inner shell concerning the computer machine environment are described. In section 5.3 we present the abstract design features of the inner shell using the notion of the functional structures. Section 5.4 presents the main performance probes. finally, section 5.5 discusses the problem of selecting a suitable programming language for the implementation of the complete shell.

#### **1.3.6 CHAPTER 6:**

THE IMPLEMENTATION DETAILS OF THE SIMULATION OF AN ACTIVITY STRUCTURES BASED POSSIBILISTIC GENERATOR

In this chapter, we present the implementation details of the internal structure of the activity based complete shell that was outlined in chapter 5. The complete shell can be used for generating extensible (i.e. possibilistic) computer systems. Sections 6.1-6.3 and part of section 6.4 present the first three design steps of the designer. In section 6.4.1 the generation of the cooperation environment activities are presented. Section 6.5 describes the implementation details of the various functional structures used in the design.

#### **1.3.7 CHAPTER 7:**

EXPLORING THE DYNAMIC BEHAVIOUR OF THE ACTIVITY STRUCTURES BASED POSSIBILISTIC GENERATOR OF COMPUTER SYSTEMS

In this chapter, we develop a special theoretical framework, the *performoact*, which captures the trends of behaviour of interest to the designer and selects those admissible trends that can be used to tune the activity structures based designs. This framework helps to preserve two important criteria, the self- regulation and concurrency (see sections 7.2 and 7.3). The parameters (of a similar, in substrata) of a highly constrained system, the Nuke, are assigned to the possibilistic generator in order to verify the activities of the generator (see section 7.4). The verification process is used to carry out several case studies in order to analyse the effects of various changes within the user interaction environment, the changes within the machine environment, different addressing policies, and many other parameters having influence upon the performance indices (see section 7.6). The purpose of establishing these case studies is to understand the contribution of those design parameters and functionality changes that are responsible for producing effective computer systems. Finally, the chapter discusses the validation process of the possibilistic generator (section 7.7).

#### **1.3.8 CHAPTER 8:**

#### CONCLUSIONS AND FUTURE RESEARCH

In this chapter we summarise the main research contributions of this thesis and discuss the new research problems suggested by this work (see section 8.1). Suggestions for expansion of this work were presented (see section 8.2).

## Chapter 2

## AN OVERVIEW OF THE EXISTING TECHNIQUES FOR CONSTRUCTING HIGHLY CONSTRAINED COMPUTER SYSTEMS WITHIN THE SCIENCE PARADIGM

### 2.1 General Discussion

This chapter presents an exposition of current problems and issues associated with design, development and evaluation of highly constrained computer systems. This strives at:

- Outlining the particular difficulties associated with the application of the existing techniques of the science paradigm to the problems in which their solutions are sought in the subsequent chapters.

- 2. Outlining the major areas of concern of which one should be aware of in the construction of highly constrained computer systems.

- 3. Establishing a certain outlook, or an overview, towards the phenomenon of protection; one of the major constraints required for constructing the highly constrained computer systems.

Since the early days of the computer industry, there has been considerable interest in the construction, and performance evaluation, of computer systems. The most common goal has been obtaining better insight into their behaviour and improving their performance.

"During the last decade, we have seen the development of a large number of computer systems. In most cases, these systems have failed to meet <sup>1</sup> the performance objectives predicted during the initial design. During the same period, the complexity of these systems has increased tremendously with the introduction of multiprogramming, protection, multiprocessing, virtual memories, etc. It has thus become more difficult to understand the behaviour of these systems in a qualitative sense, let alone quantitatively predict their performance" (Graham 1984).

There are many difficulties in constructing a general-purpose computer system. Problem decomposition, component connections, and interprocessor communication are some issues which can pose significant obstacles to the successful application of such systems.

Therefore, the road to understanding the behaviour and predicting the performance of protected computer systems has been, and still is, arduous. Many people have realised this (Downs 1984, Fabry 1974, Lampson and Sturgis 1976, Wilkes and Needham 1979) and have attempted to investigate the problem of constructing effective highly constrained computer systems, and to proceed towards the development of superior tools. Here we should note that we are concentrating on both construction and evaluation tools, since

"it has been proven that construction without evaluation is usually inadequate"

(Cantrell and Ellison 1968).

The tool that should be developed must not only provide the design primitives but also it should enable the designer to monitor performance and determine (*dynamically*) where restrictions or bottlenecks occur.

There are certain typical questions that the designer can easily answer with a design tool that provide performance information, for example, the time spent by the processor running or waiting for a task, or the time spent in communication.

In efforts to deal with the problem of designing effective highly constrained computer systems, the expressions "computer architecture", "software engineering", and "knowledge

<sup>&</sup>lt;sup>1</sup>Notable examples on such failures are: the CAP computer system designed by Wilkes and Needham (Needham 1977), its performance degredation reported by Watson (1978), NYU Ultracomputer by Gottlieb et al (1983), and its performance degredation reported by Maples (1985); and the NEPTON system by Evans (1981) its performance degredation reported by Newman and Woodward (1981).

engineering" designate the relevant solution fields. These fields capture the results and accomplishment of research in various parts of computer science (Gaines and Shaw 1986, Tully 1985, Capper 1986), that contribute to the problem of constructing suitable highly constrained computer systems.

According to the results of investigation presented later in this chapter, there is no widely accepted or practiced methodology for the construction of highly constrained computer system, that outlines clearly the construction discipline, based on the three design feilds. The conclusion reached was that the existing attempts of constructing effective highly constrained computer systems can be described as *"black-box"* designs (c.f. Figure 2.1).

Figure 2.1: The black box: The Traditional Design Methods

The general consensus is that many problems in systems construction and development are caused by the following:

- 1. The lack of a consistent construction methodology that can offer a the framework

- which captures the different processing environments and provides effective structures (in hardware, firmware, and software) as well as the integration constraints for holding them together. This is quite an important issue, since we noticed the repeated failures of many of the existing highly constrained computer systems (c.f. Bic 1982) and a large amount of cosmetic techniques used. For example, while designing highly

constrained computer systems using mainly software engineering techniques (e.g. Madsen 1981) one could face several performance difficulties and might require the system to be redesigned with the use of, e.g. performance engineering (Smith 1980), or the transparency design technique (Parnas and Siewiorek 1975). All these steps are certainly expensive and do not ensure the optimal results (Mamrak and Randal 1977). Similarly if computer architecture is used to design highly constrained computer systems (e.g. Dennis 1980) there are variety of other problems, such as the "von Neumann bottleneck" and the "semantic gap" problems.

The von Neumann bottleneck refers to the type of interaction between the CPU and the computer memory: the huge content of the store must pass, one word at a time, to the CPU and back again. In other words, the von Neumann bottleneck stems from the fact that at the machine language level, any access of a data object requires first the fetch and execution of an appropriate instruction. This is aggravated by the fact that only the elementary (scalar) data objects exist (c.f. Backus 1985). The semantic gap is defined by Myer (1978):

"The semantic gap is a measure of the difference between the concepts in high-level languages and the concepts in the computer architecture."

Further descussion on the semantic gap is provided by Jones (1977) and Flynn (1980). Here we summarise our findings about the semantic gap issue. It is known that the data objects of typed high- level languages may be defined as a triple:

DATA OBJECT ::=  $\langle IDENTIFIER, VALUE, TYPE \rangle$

In a computer, the data object is represented by the content of some memory location (or a number of consecutively addressed memory locations). If the computer is of the von Neumann variety, then only the component VALUE is represented in the memory. Consequently, TYPE is not an attribute of the data object any more but becomes the attribute of an operation (see Wulf 1981). This discrepancy produces a large semantic gap. The semantic gap of the von Neumann architecture (e.g. VAX architecture) motivates me to search the better operational principles that are matched to the requirements of the support software tool and that provide better performance. Current solutions of the semantic gap minimisation are obtained by introducing the capability addressing of the objects that are encapsulated into memory segment. This allows for typing and access right control at the granulation of the memory segments, at the cost of aggravating the von Neumann bottleneck. This is so become since every single memory location is accessed through at least two levels of indirections.

Mohamad (1982) suggested the introduction of the descriptor-oriented architecture which deals with the semantic gap minimisation. In this scheme, each data object (elemantery or complex) is presented to the hardware by a descriptor that containes all the information needed to enable the communication structure to carry all data transports between the main memory and the CPU of the system. Briefly, it states:

"the larger the semantic gap the higher the performance degradation is".